# 宽带信号采样的关键技术研究

王志刚,卢涛,田书林

(电子科技大学自动化工程学院 成都 610054)

【摘要】提出了一种实现宽带信号实时采样的技术原理和应用设计方法;论述了混合滤波器组技术对传统并行交替采样结构进行非均匀采样的校准处理,多通道采样的时钟与触发同步机制,以及分相存储实现大容量采样数据存储等研究内容;给出了系统的可行性设计。

关键词 AD变换; 非均匀采样校准; 多通道同步; 采样存储中图分类号 TM930.2; TM930.111 文献标识码 A

## Study on Key Techniques in Sampling for Wide-Band Signal

WANG Zhi-gang, LU Tao, TIAN Shu-lin

(School of Automation Engineering, UEST of China Chengdu 610054)

**Abstract** This paper presents a design method for Wide-Band Signal Sampling (WBSS). Hybrid filter banks, unique clock distribution and multi phase storage are discussed for considering high precision, synchronized sampling and mass samples storage. Consequently, a design of WBSS based on above techniques is presented and its hardware prototype is realized with a 12 bit, 200 Msa/s for applications of WBSS.

Key words ADC; calibration on non-uniformity; multi-channels synchronization; samples storage

广泛应用于雷达、数字通信、电子对抗等领域的宽带信号实时采样技术,通常要求具备几百MHz采样率、10位以上有效分辨位数、亚纳秒通道同步能力,以及持续大容量存储数据等性能指标。限于模数转换 (Analog to Digital Conversion,ADC)芯片速度,一般以多片ADC并行交替采样获得高采样率。但以多片ADC并行交替采样,需对非均匀采样校正处理;由于传输延迟、时钟抖动,导致多通道间采样同步误差,需要加以控制处理。持续高速的采样数据流存储也是系统瓶颈之一。建立大容量的数据存取控制,可以使以上问题在较大程度上得以缓解,本文详细论述了相应的关键技术原理及其系统设计方法。

#### 1 并行交替采样的非均匀处理

传统上采用多片ADC并行交替采样的方式获得更高采样率<sup>[1]</sup>,当系统垂直分辨率不大于8位时,采用低抖动时钟分配、器件遴选、屏蔽隔离等措施,就能满足采样精度的要求。而当系统垂直分辨达12位以上时,由于采样时钟的微小抖动、时延,以及ADC器件参数的离散性(如增益、偏移失配)无法忽略,导致传统并行交替结构存在非均匀采样状况,严重降低了ADC系统的无杂散动态范围、有效分辨位数等指标<sup>[2]</sup>。

图1所示为2片ADC并行交替采样的非均匀校正处理原理,该处理原理应用的混合滤波器组(Hybird Filter

Bank,HFB)重建技术<sup>[3]</sup>,实际上是多抽样率信号处理的一种应用<sup>[4]</sup>。图中每路ADC子系统的采样率均为系统采样率的1/2,由同一时钟及其反相进行驱动。设输入为一限带信号u(n),即有 $0 \le \omega \le \pi/T$ ,其中T为系统采样周期; $A_0(j\omega)$ 、 $A_1(j\omega)$ 为两路分解滤波器的频响, $A_0(j\omega)$ 为低通滤波器, $A_1(j\omega)$ 为

图1 应用混合滤波器组技术2路ADC交替采样的原理

带通滤波器,-3 dB频率为T/4。将输入信号u(n) 划分为2个子带,子带信号经ADC以T/2速率采样,图中,ADC视为2倍抽取器。 $\uparrow$  2表示2倍升采样率器(内插器),即对2个子带离散样值相邻2点间均匀插入1个0样值;

收稿日期: 2005-08-31

作者简介: 王志刚(1967-), 男, 讲师, 主要从事测量仪器、数据采集与信号处理方面的研究.

$D_0(z)$ 、 $D_1(z)$ 表示两路综合滤波器,用于将内插后产生的以原始采样率谐波 $\pm 2\pi/2$ 、 $\pm 4\pi/2$ 等为中心的基带镜像频谱滤除,以重建原始信号均匀样值。设2路交替采样的输出为 $Y(e^{i\omega})$ ,则可导出系统输入输出关系式为:

$$Y(e^{j\omega}) = \frac{1}{2T}G_0(e^{j\omega})U(j\omega) + \frac{1}{2T}G_1(e^{j\omega})U(j\omega - j\pi/T)$$

(1)

$$G_0(e^{j\omega}) = A_0(j\omega)D_0(e^{j\omega}) + A_1(j\omega)D_1(e^{j\omega})$$

(2)

$$G_1(e^{j\omega}) = A_0(j\omega - j\pi/T)D_0(e^{j\omega}) + A_1(j\omega - j\pi/T)D_1(e^{j\omega}) \qquad 0 \le \omega T \le 2\pi$$

(3)

从式(1)~(3)可见,在式(1)中,如果满足当 $G_0(e^{j\omega})$ 仅为一个比例因子k或延时d,以及 $G_1(e^{j\omega})$ 为0,即信号的混叠影响成分 $U(j\omega-j\pi/T)$ 为0,表示为:

$$\begin{cases}

G_0(e^{j\omega}) = e^{-j\omega d} \\

G_1(e^{j\omega}) = 0

\end{cases}$$

(4)

则得到 $Y(e^{j\omega})=e^{-j\omega d}U(j\omega)$ ,即理想的采样均匀重建目标。 $G_0(e^{j\omega})$ 、 $G_1(e^{j\omega})$ 分别表征系统失真及混叠的频率响应。因此,若先给定分解滤波器的频响 $A_0(j\omega)$ 、 $A_1(j\omega)$  及系统延时d,则通过式(2)~(4)可以计算出综合滤波器的频响 $D_0(e^{j\omega})$ 、 $D_1(e^{j\omega})$ 。实际设计中,常采用一种参数优化逼近方法来实现。

首先,在给定的上述条件下,可以得到综合滤波器理想频响,令其为 $D(e^{j\omega})$ ,并设综合滤波器为长度为L的有限冲激响应 (Finite Impulse Response,FIR)滤波器 $D_r(e^{j\omega})$ ,其冲激响应为 $d_r(n)$ ,则由误差能量最小原则可得:

$$\varepsilon = \int_{-\pi}^{\pi} \left| D(e^{j\omega}) - D_r(e^{j\omega}) \right|^2 d\omega \tag{5}$$

求极值可导出:

$$d_r(n) = \frac{1}{2\pi} \int_{-\pi}^{\pi} D(e^{j\omega}) e^{j\omega n} d\omega$$

(6)

式中  $d_r(n)$  为理想滤波器  $D(e^{j\omega})$  的逆傅里叶变换(Inverse Fast Fourier Transform, IFFT)运算,可利用 MATLAB计算。

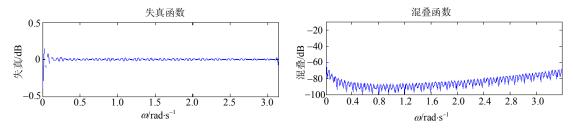

以3阶模拟分解滤波器为例,分解滤波器-3 dB频率为T/4,利用IFFT得到L=64的综合滤波器,系统的失真函数和混叠函数如图2所示,延时d为49;平均失真误差为0.03 dB;平均混叠误差为-75 dB。需注意选择IFFT运算中的点数n,为考虑误差精度要求,可选为512点或1024点。

整个设计过程是分解滤波器  $A(j\omega)$ 、延时d、综合滤波器  $D_r(e^{j\omega})$  及长度L等参数的迭代优化过程。设计中采用Analog Device公司12位模数转换芯片AD9432,采样率105 MHz;设定分解滤波器采用巴特沃斯3阶滤波器,子带分割点50 MHz。通过迭代优化得到设计综合滤波器系数及长度L,再由可编程逻辑芯片硬件实现综合滤波。

图2 系统失真及混叠仿真结果

#### 2 多通道采样精确同步设计

在宽带高精度采样系统的实际应用中,如雷达系统测距、定向作业等,要求严格的对多通道的定时与同步控制机制<sup>[5]</sup>。多通道同步目标是在多系统或多通道之间建立准确同步的启动采集机制。

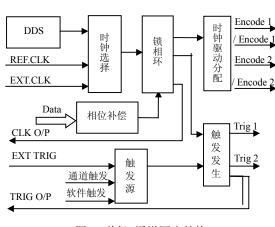

图3为单系统2通道的同步结构,其中直接数字合成(Direct Digital Synthesis, DDS)用于产生高分辨采样时钟,锁相环(Phase Locked Loop, PLL)是同步控制机制的核心部件,要求极低的抖动(jitter)贡献。

根据多通道采样系统应用中不同采样模块之间的主从关系,以下用两种工作模式对多通道采样加以说明。在单机应用、或本机做多机系统主者(master)时,锁相环对本机DDS电路的输出时钟进行相位锁定,输

出三路时钟:一路经时钟驱动分配电路供本机2个通道PECL采样时钟(encode),一路送至触发电路同步触发信号的输出,使本机的2个通道采集操作可同步启动触发;一路输出用于多机系统中的其他从者仪器的采样时钟基准(EXT CLK)。对于本机2通道,其同步误差仅取决于时钟分配芯片及触发发生的延迟不确定度,以及线路布局分配的物理属性。在多机系统应用、本机做从者(slave)时,采样时钟来自外部,锁相环对外部主者时钟EXT CLK或参考时钟REF CLK进行倍频和相位锁定,经时钟分配产生本机2个通道PECL同步采样时钟。相位补偿电路的一个作用是在锁相环路注入调节量,使得环路输出时钟与外部时钟同步;另一个作用是预置一个相位偏差,当多机系统中参考时钟或外部时钟由于传导延迟不同而产生固定的相差时,可以通过此相位偏差进行通道间相位的手工校准,其数据Data由系统中各仪器独立设置。触发发生电路提供通道电平触发、外触发,以及系统软件触发3种触发模式,输出触发信号TRIG O/P用于触发多机系统内其他从者仪器。

设计中采用了DDS+PLL频率合成结构,由AD公司集成DDS芯片AD9852、SYNERGY差分数字锁相环频率合成芯片SY89421构成,时钟分配采用差分时钟驱动器SY100E111,具有高分辨、频率捷变、宽频及控制灵活的特点。为使触发尽量同步,采用了等尺寸、高带宽的RF线缆及MMCX连接组件构成物理连接。设计中还注意了杂散、残余相差、传输干扰等带来的影响,可通过选取合适的DDS参考频率、PLL倍频、高稳定时钟电路、传输匹配,以及结构设计来加以改善。

#### 3 采样数据分相存取设计

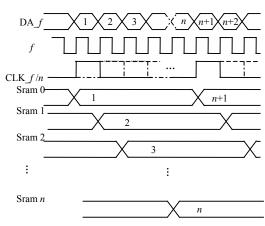

为解决几百兆速率的采样数据的持续存储问题,可以将高速数据分相以降低速率。数据分相的方法是将采样率为f的高速采样数据流在时间上分成相差为360/n的n相、慢速数据流,再以低速SRAM器件存储。图4所示为数据分相存储时序。图中,DA\_f为原始采样数据,f为采样时钟,CLK\_f/n为分相时钟,由f作n分频移相获得。Sram 0,1,2,…,n为各片存储器件数据端口。采样操作时,速率为f的高速ADC输出数据DA\_f,首先经n相分离,在CLK\_f/n分相时钟控制下,原始数据流被分离为n路 f/n 速率的慢速数据流,送至n片SRAM。同时,分相时钟CLK\_f/n经写地址发生电路产生n片SRAM的写地址信号,使n路速率f/n的慢速采样数据写入n片SRAM中,实现慢速存储器件对高速数据流的连续存储。SRAM区采用环状地址管理,用一个可循环计数器实现,触发发生时,写地址发生电路记录下当前地址,循环计数器继续环状产生写地址,直至指定的预触发深度,停止计数。

图3 单机2通道同步结构

图4 采样数据的分相存储时序

在读取数据时,利用DSP器件具有的较大程序访问空间特点,将n片SRAM空间映射到DSP外部程序存储空间内,产生对应的SRAM地址及其片选、使能信号,通过DSP读取操作,完成n片SRAM的数据输出,顺序输出SRAM 0~n的数据,从而合成原始采样数据流。设计中,DSP采用TI公司TMS320c5409芯片,其外部程序存储空间达8 M字,可映射采样数据空间较大。除SRAM器件外,所有控制逻辑电路均利用FPGA器件实现。

#### 4 系统应用

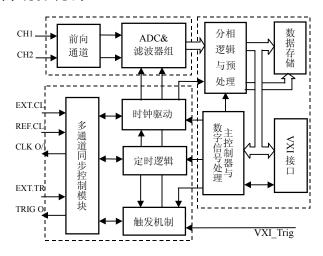

系统应用如图5所示。宽带信号CH1/CH2经放大/衰减、带宽抑制、偏移调整等调理后,滤波器重组完成采样数据的非均匀校准。由多通道同步控制、触发机制、定时逻辑与时钟驱动等构成组合,通过对时钟(EXT.CLK、REF.CLK等)、触发(EXT.TRIG)的选择,构成不同类型的同步控制组态。由数据分相逻辑、主控制器与数据处理构成组合,分相将数据写入或读出多片SRAM组成的数据缓存。DSP实施系统控制和数据处理,VXI部分为模块提供一个寄存器基的VXI接口。基于此结构,可实现一种宽带高精度采样系统。经测试,系统采样速率为200 Msa/s,有效分辨位数大于10.5位,多通道同步误差小于250 ps,单次记录深度2 M字,主要技术指标达到系统设计要求。

图5 高速高精度数字化仪系统体系结构

### 5 结 论

上述关键技术研究成果应用于某波形分析仪项目的研制中,已通过技术鉴定与设计定型。目前,宽带信号实时采样技术仍处在不断发展中。在非均匀校准方面,考虑对分解滤波器的设计再优化,以提高信号重建的精度(有效分辨接近11位);多通道同步方面,若能降低时钟分配环节对时钟抖动的贡献,改进触发同步,同步误差有望接近100 ps;而在采样存储方面,对于更高采样率的应用,应考虑设计FPGA+DDR SDRAM(双速率动态存储)结构,解决高速率、大容量问题。

#### 参考文献

- [1] Black J W C, Hodges D A. Time interleaved converter arrays[J]. IEEE Journal of Solid State Circuits, 1980, 15: 1 022-1 029.

- [2] Looney M. Advanced digital post-processing techniques enhance performance in time-interleaved ADC systems[R]. Analog Devices Inc.: Analog Dialogue 37-8, 2003.

- [3] Velazquez S R. Hybrid filter banks approach for analog/digital conversion[D]. Cambridge: Mass. Inst. Tech., 1997.

- [4] Crochiere R E, Rabiner L e. 多抽样数字信号处理[M]. 北京: 人民邮电出版社, 1987.

- [5] Blake J, Bullock T, King M. Test results and analysis of a low cost core GPS receiver for time transfer applications[C]// 1997 IEEE Frequency Control Symposium, Orlando Florida, 1997.

编 辑 熊思亮