· 学术论文与技术报告 ·

## 锁相跳频源的极值相位裕量设计法\*

## 刘光祜\*\*

(电子科技大学电子工程系 成都 610054)

【摘要】 针对电流型电荷泵 PLL 频率综合器芯片,提出一种称为极值相位裕量的无源环路滤波器方案和设计方法。使 PLL 频率合成器成为 2型(3~4)阶环;论证了设计公式,并用良好设计方法研制了一个 L 波段的跳频源。该跳频源在相位噪声、调频速度和杂散抑制等方面的性能指标较高。

关键 词 锁相; 频率综合器; 滤波器; 跳频源; 相位裕量; 相位噪声中图分类号 TN911.8

锁相(PLL)频率综合器(跳频源)的低杂散特性是直接数字频率综合器(DDS)所无法取代的一个优点。PLL 频率综合器的设计,其主要工作就是正确选择和设计环路滤波器(LF),使频率综合器指标在相位噪声、杂散抑制、跳频速度和稳定性等方面合理兼顾,实现综合性能最佳。因此,本文仅讨论环路滤波器的设计方法。

目前电流型电荷泵锁相频率综合器芯片占主流,在设计 PLL 时,有源 LF 较无源 LF 几乎已经失去传统意义上所有的优点。计算机仿真和实践都表明:获得较高的边带抑制度,无源 LF 仅需简单的 RC 低通滤波,而有源 LF 却往往要使用具有传输零点的高阶 LC 低通滤波。此外,有源 LF 使用了集成运算放大器,还会使相位噪声增加。因此,很多半导体器件公司如 NSC、PSC 都推荐使用无源环路滤波器。

本文针对用电流型电荷泵鉴相的频率综合器芯片,提出了一种无源三阶环路滤波器的工程设计方法。该方法与用 Matlab 作理论分析的结果吻合,应用该方法在 L 波段完成的微波锁相跳频源达到了相当高的性能指标。

### 1 环路滤波器

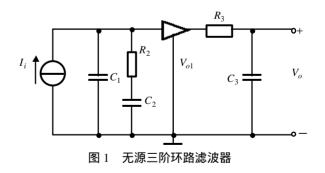

无源环路滤波器见图 1 ,  $C_1$ 、 $C_2$ 和  $R_2$ 构成滤波器主体。由于电流型电荷泵鉴频鉴相器作为该滤波器的输入,使 PLL 成为三阶二型环,其性能优于电压型鉴相器采用有源滤波器的理想二阶环。图 1 中的  $R_3$ 和  $C_3$ 构成鉴相频率抑制滤波器。此外,对图中的电压放大器,希望具有 $Z_i \rightarrow \infty$ 和  $Z_o \rightarrow 0$  的特性,可以用运放来实现。该放大器作用之一是隔离两个滤波器,使环路滤波器传输函数简单,工程设计简化。另一个作用是

提高 VCO 的控频电压,以获得所需的频率输出。放大器增益  $K_A$  的选取由所需的最大控频电压  $V_{om}$  决定,而  $K_A$  对环路的影响在设计中统一考虑。由于滤波器的输出送至 VCO,故只要将提高 VCO 的输入电容计入  $C_3$ ,可以认为滤波器负载  $Z_C \rightarrow \infty$ 。

由于环路滤波器由前级电流泵鉴相器输入信号,故环路滤波器的信号源是电流源,环路滤波器

<sup>2001</sup>年7月17日收稿

<sup>\*</sup> 国防科工委预研基金项目

<sup>\* \*</sup> 男 55 岁 硕士 教授

的传递函数为传输阻抗 Z(s),为

$$Z(s) = \frac{V_o(s)}{I_i(s)} = Z_1(s) \frac{K_A}{1 + sC_3R_3} = \frac{sC_2R_2 + 1}{s^2C_1C_2R_2 + s(C_1 + C_2)} \frac{K_A}{1 + sC_3R_3}$$

(1)

### 2 PLL 频综的线性数学模型及传递函数

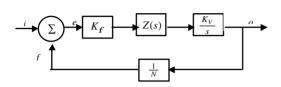

图 2 给出了 PLL 频综关于相位的线性数学模型。图中, $K_F(\text{mA})$ 和  $K_V(\text{MHz/V})$ 分别是鉴相跨导和 VCO 压控灵敏度。 $K_F$ 和  $K_V$ 单位中的  $2\pi$ 因相乘会抵消,故没有示出。

由反馈环知识,模型的开环传输函数为

$$H_o(s) = \frac{\boldsymbol{q}_f}{\boldsymbol{q}_e} = \frac{K_{\Phi} K_V Z(s)}{Ns}$$

(2)

图 2 PLL 频率合成器相位线性模型

将式(1)代入式(2),整理可得

$$H_o(s) = \frac{K_{\Phi} K_V K_A (1 + sT_2)}{Ns^2 C_1 (1 + sT_1) (1 + sT_3)} \frac{T_1}{T_2}$$

(3)

式中

$$T_1 = R_2 \frac{C_1 C_2}{C_1 + C_2}$$

,  $T_2 = C_2 R_2$  ,  $T_3 = C_3 R_3$  o

观察式(3)可知,由于  $R_3$ 、 $C_3$ 的使用,该 PLL 其实已经是四阶环。为了提高环路的稳定性,在设计杂散抑制滤波器时,应该使  $R_3$ 、 $C_3$ 产生的极点适当远离主极点,为此,可设定如下条件

$$\frac{1}{T_3} > \frac{5}{T_1} \tag{4}$$

由此,使PLL仍具有三阶环的特性。

令式(3)中的 s=iw, 便获得环路的开环频率特性函数为

$$H_{o}(j\mathbf{w}) = \frac{-K_{F}K_{V}K_{A}(1+j\mathbf{w}T_{2})}{\mathbf{w}^{2}C_{I}N(1+j\mathbf{w}T_{1})(I+j\mathbf{w}T_{2})}\frac{T_{I}}{T_{2}}$$

(5)

### 3 环路滤波器设计原理

#### 3.1 时间常数与环路参数的关系

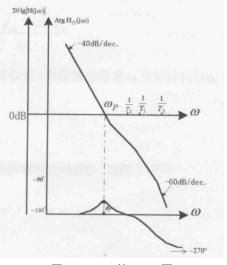

根据  $T_1$ 、  $T_2$  的定义,成立  $1/T_2 < 1/T_1$ 。又  $1/T_3$  5/ $T_1$ ,因此  $H_o(\mathbf{j}\mathbf{w})$ 应具有图如 3 所示的波特图,图中  $\mathbf{w}_n$  是增益交叉频率。

将式(5)分母两个极点因子展开,注意到  $_p<1/T_1$   $_p<<1/T_1$ ,因而 $oldsymbol{w}_p^2T_1T_3<<1$ ,表明在 $oldsymbol{w}_p$  附近,

成立 $\mathbf{w}^2T_1T_3 << 1$ ,故

$$(1 + jwT_1)(1 + jwT_3) \approx 1 + jw(T_1 + T_3)$$

(6)

将式(6)代入式(5),则可写出在 $w_p$ 附近开环频率特性函数的幅频特性函数为

$$\left| H_{o}(\mathbf{j}\mathbf{w}) \right| = \frac{T_{1}}{T_{2}} \frac{K_{\Phi} K_{V} K_{A}}{\mathbf{w}^{2} N C_{1}} \sqrt{\frac{1 + \mathbf{w}^{2} T_{2}^{2}}{1 + \mathbf{w}^{2} (T_{1} + T_{2})^{2}}}$$

(7)

在 $\mathbf{w}_p$  附近开环频率特性函数的相频特性函数为

$$\arg H_{o}(j\mathbf{w}) = -180^{\circ} + \tan^{-1}(\mathbf{w}T_{2}) - \tan^{-1}[\mathbf{w}(T_{1} + T_{3})]$$

(8)

#### PLL 的相位裕量为

$$\mathbf{f} = 180^{\circ} - |\arg H_{\circ}(\mathbf{j} \mathbf{w})| = \tan^{-1} [\mathbf{w}(T_1 + T_3)] - \tan^{-1} (\mathbf{w} T_2)$$

(9)

为保证环路的可靠稳定,可将增益交叉频率 $\mathbf{w}_p$  设在相位裕量的极点处,如图 3 所示。即

$$\left. \frac{\mathrm{d} \mathbf{f}}{\mathrm{d} \mathbf{w}} \right|_{\mathbf{w} = \mathbf{w}_{a}} = 0 \tag{10}$$

将式(9)代入式(10),可得

$$T_2 = \frac{1}{\mathbf{w}_p^2 (T_1 + T_3)} \tag{11}$$

再将式(11)代入式(9),经运算,可得

$$T_1 + T_3 = \frac{\sec \mathbf{f}_m - \tan \mathbf{f}_m}{\mathbf{w}_n} \tag{12}$$

图 3  $H_0(j\mathbf{w})$ 的 Bode 图

式(11)和(12)便是三个时间常数与环路设计参数(单位增益带宽 $\mathbf{w}_p$ 和相位裕量 $\mathbf{f}_m$ )的关系。

#### 3.2 时常数 T<sub>3</sub>的确定

选定鉴相频率抑制滤波器对鉴相频率泄漏的衰减为 $\alpha(dB)$ ,由图 1 可得

$$201g \left| \frac{V_{o1}}{V_o} \right| = 201g \left| 1 + j \boldsymbol{w}_r T_3 \right| = \boldsymbol{a}$$

(13)

由式(13),可求得

$$T_3 = \frac{\sqrt{10^{a/10} - 1}}{\mathbf{w}_r} \tag{14}$$

式中  $\mathbf{w}_r$ 是环路鉴相频率。另外要注意, $T_3$ 的取值应尽量满足式(4)。

#### 3.3 元件值的确定

在  $K_f$ 、  $K_V$ 已知,选定  $K_A$ 、  $\alpha$ 以及  $\mathbf{w}_p$  和  $_m$ 以后, $T_1$ 、  $T_2$ 、  $T_3$  便可以求得。进而可求得滤波器的全部元件值,由  $|H_o(\mathbf{j}\mathbf{w}_p)|=1$  和式(5),可求得  $C_1$  为

$$C_{1} = \frac{T_{1}}{T_{2}} \frac{K_{j} K_{v} K_{A}}{\mathbf{w}_{p}^{2} N} \sqrt{\frac{1 + \mathbf{w}_{p}^{2} T_{2}^{2}}{(1 + \mathbf{w}_{p}^{2} T_{1}^{2})(1 + \mathbf{w}_{p}^{2} T_{3}^{2})}}$$

(15)

进而求得

$$C_2 = \left(\frac{T_2}{T_1} - 1\right) C_1 \tag{16}$$

$$R_2 = \frac{T_2}{C_2} {(17)}$$

选择

$$R_3$$

后,则

$$C_2 = \frac{T_3}{C_2} \tag{18}$$

### 4 设计实例

设计 L 波段跳频源,步长  $f_{\nu}=1$  MHz,中心频率  $f_{0}=1$  000 MHz,带宽 200 MHz,分频比 N=1 000,采用 AD 公司频率合成器芯片和 HP 公司的 VCO。环路带宽  $\mathbf{w}_{\nu}$  的选取与跳频源性能关系很大。  $\mathbf{w}_{\nu}$

增大可以使跳频速度加快,但鉴相频率的杂散也会增加。另外, $\mathbf{w}_p$ 增加对近端相位噪声改善有利,但对抑制由 VCO 和分频器产生相位噪声不利。该实例选取 $\mathbf{w}_p=2\pi\times40\times10^3\,\mathrm{rad/s}$ 。鉴相频率泄漏衰减器取 $\alpha=10\,\mathrm{dB}$ 。相位裕量取 45°。本文将原始数据代入该文导出的设计公式,便可得到环路滤波器的元件值。

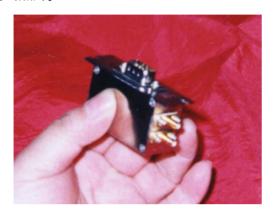

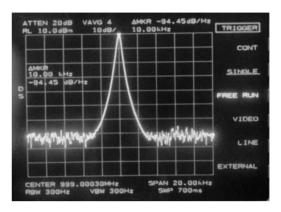

所设计的跳频源样机具有良好的综合性能:其相位噪声达到 – 95 dBc/Hz@ 10 kHz , 边带杂散 (1 MHz) – 70 dBc , 跳频建立时间 (  $\Delta f$ =120 MHz ) <50  $\mu$ s。图 4 和图 5 分别示出了实物和相位噪声测试照片。

图 4 PLL 跳频源外观照片

图 5 10 kHz 相位噪声测试照片

#### 参考文献

- 1 Willian O.Keese, National Semiconductor Application Note 1001, May 1996

- 2 National Semiconductor Date Sheet, Edtion 2000

- 3 Gardner, F.M. Charge-Pump Phase-Lock Loops, IEEE Trans.Commun. COM-28, Nov.1980

- 5 Liu Guanghu.Design fo a high quality AFC system.Journal of University of Electronic Science and Technology of China,1997,26(suppl):147~152[刘光祜.高性能 AFC 系统设计.电子科技大学学报,1997,26(增):147~152]

# Design of PLL Frequency Synthesizer by the Method of Extreme Value Phase Margin

Liu Guanghu

(Coljlege of Electronic Engineering, UEST of China Chengdu 610054)

**Abstract** A passive loop filter scheme and the design method of the filter for current charge pump PLL frequency synthesizer chip are given in the paper. The method is known as the method of extreme value phase margin. Also, all design formula are proved. In fact, the PLL frequency synthesizer is 2 type (3~4) order loop model. Using the method and formula above, a L-band synthesizer has been finished. It has satisfactory performance on phase noise, frequency jump speed and spur rejection.

**Key words** phase locked loop; frequency synthesizer; loop filter; frequency jump synthesizer; phase margin; phase noise