2. 美国加州大学洛杉矶分校计算机系 洛杉矶 加州 美国 90095;

3. 北京大学洛杉矶加州大学理工联合研究所 北京 海淀区 100871

2. Computer Science Department, University of California, Los Angeles Los Angeles CA USA 90095;

3. PKU-UCLA Joint Research Institute in Science and Engineering Haidian Beijing 100871

随着通信与计算机技术的迅猛发展,无线通信与网络已经深入到人们的日常生活,也成为了现代科技研究的一个重要领域。以WiFi为例,根据美国市场研究公司ABI Research的报道,2014年的WiFi芯片组出货量已超过26亿,预计2015~2019年间,WiFi芯片组的累计出货量将接近180亿[1]。

一方面,无线通信传输速率迅速提高,仍然以WiFi为例,从1999年开始,流行起来的WiFi标准数据传输速率以每6年11倍的速度迅速提升,到2015年802.11ac正式颁布时,WiFi标准数据传输率将达到6.9 Gbps。另一方面,随着无线通信的普及,衍生出了大量相关的新应用,小至可穿戴设备、无线电子医疗设备,大至空天一体军事化信息网络,多元化的无线应用对无线开发平台提出了新的需求。

目前,我国已经投入了大量科研力量对无线相关技术进行研究。但受限于当前的无线网络底层平台,研发人员往往不能对无线协议完成定制开发工作。传统无线算法的物理层和链路层(PHY、MAC层)基本都是在芯片中实现,其内部算法和协议固定,不具备可定制性,而且主流无线芯片均被若干家国外公司垄断。在某些特殊行业及特殊场景下,会对无线通信的特性提出一些特殊的需求。例如军事通信需要有更高的安全性、隐蔽性;可穿戴计算中的无线传输需要有低功率、低反应延迟的特性;在某些工控场景下,又需要进行远距离传输或者在信道拥堵时紧急传递信息。当原有的协议不能够满足上述类似的特殊要求时,研发人员希望能够定制一个新的无线网络底层系统(包括PHY、MAC层等),并投入实际场景使用。因此,我国无线领域的研发者和特殊需求的使用者亟需一种高性能、可定制的无线网络底层软硬件平台。

针对上述需求,本文设计了GRT系统,该系统具备以下3个特征。1)高性能。主要包括高吞吐率、低延迟两部分。2)高可定制性。GRT系统提供了一种标准化、模块化的无线协议软硬件协同开发环境。3)高兼容性与开放性。GRT系统可被定制为标准网络协议的软硬件平台,提供与商业无线设备的兼容性。

另外,GRT系统可以与现有网络协议无缝对接,易于与主计算机集成,实现网络跨层次优化。并能够给上层网络层提供开放接口,通过其可定制管控的特性,将软件定义网络(SDN)的管控能力延展到无线网络底层。

1 背景介绍 1.1 软件无线电(SDR)技术文献[2]于1992年首次明确提出了软件无线电的概念。软件无线电的中心思想是构造一个具有开放性、标准化、模块化的通用软硬件平台。基于这一相对通用的软硬件平台,可以采用软件编程、调用等方式,自定义地实现特定的通信功能。随着研发者对可定制无线设备的需求越来越强,软件无线电技术也逐渐开始吸引无线领域研发者的注意。

1.2 802.11技术IEEE 802.11是现今WiFi通用标准。从1997年的802.11到2015年的802.11ac,中间经历了802.11b、802.11a/g、802.11n几代变革,不到20年时间的发展,WiFi的数据吞吐率由最初的2 Mbps发展到了2015年将成为标准的6.9 Gbps。802.11技术的发展也对无线底层平台的性能需求(吞吐率、延迟)提出了很大挑战。

1.3 目前已有的无线底层平台当前的无线设备大部分都使用标准的无线芯片,这些芯片内部算法和协议是固定的,适合商业化的生产,但是无法被研发者所使用。无线芯片的物理层速率、频带宽度、中心频点以及PHY层和MAC层的实现算法都是固定的,而且功率往往受限。对于研发者来说,往往希望对协议进行修改,例如研发者希望修改802.11中MAC层的CSMA/CA算法,保证在限定时间内完成一次数据传输;或者希望修改802.11中PHY层的频偏估计算法,使得WiFi协议能够适用于更加高速的移动环境。而这些工作很难在标准芯片中进行定制。

针对上述矛盾,国内外已经开始了相应的可定制无线网络底层系统的研究。也产生了多种不同的平台结构。

第一种方案是基于纯软件的无线开发平台,这种方案采用通用处理器CPU作为计算工具实现底层协议的算法。基于CPU的无线开发平台可以为用户提供非常好的编程性,却无法保证无线通信技术的两个重要特性——高吞吐率和低延迟。无线通信协议的物理层往往需要完成大量浮点运算,例如FFT、帧同步、信道估计与均衡等模块,因此采用CPU作为计算工具不可能胜任高吞吐率的需求;另一方面,采用软件实现无线开发平台时,受到操作系统的一些不可控因素(中断、抢先式调度等),软硬件的交互延迟难以控制在几十微秒的量级。

基于纯软件的无线开发平台的代表是GNU Radio[3]。GNU Radio提供了非常好用的图形用户接口。它不仅可编程性强、并且代码开源。但受限于CPU的处理性能,GNU Radio只能提供最高2 Mbps左右的吞吐率,对802.11a/g的物理层协议处理延迟也高达几毫秒(802.11a/g的要求则是吞吐率达到54 Mbps、处理延迟为几十微秒)。因此,GNU Radio只能适用于无线通信算法的初步验证。

Sora[4]也是一种主要采用软件实现的无线开发平台,它采用高端的多核处理器作为无线底层的计算工具,用户在Windows操作系统上进行软件编程。为了解决软件吞吐率低、延迟大的问题,Sora将物理层的模块分放至不同的CPU核,并将时序性非常强的ACK模块用专用的FPGA硬件进行加速。Sora平台可以支持802.11a/g的54 Mbps吞吐率,其2*2MIMO版本可达到117Mbps的吞吐率[5]。但Sora作为一个开发平台,仍有其局限性。首先,Sora受到Windows操作系统调度算法的限制,不能够完全保证WiFi中MAC层的时序。其次,采用Sora完成开发需要具备多核、并行的编程基础,在设计底层协议的时候,需要特地为算法进行优化,大大提高了研发者的开发难度。最后,Sora的开发环境是基于Windows的操作系统,与当前大部分的软件无线电平台都无法兼容。

第二种方案是基于FPGA硬件的开发平台。FPGA是一种特殊的可重构硬件,可以根据需要重构成所需的功能逻辑。它可以提供比软件高的多的吞吐率,并保证非常好的实时性。但是,硬件设计难度比软件要大的多,导致平台的可编程性降低。尽管研发者能够自主地在FPGA上通过编写硬件代码做无线底层协议的开发,但他们必须分散大量的精力去考虑硬件是如何设计,大大降低了开发效率。

WARP[6]平台是一种典型的基于FPGA的无线开发平台。WARP通过以太网接口与PC机相连,它采用高性能的FPGA作为协议算法的实现平台,能够实现高吞吐率以及低延迟的要求。但是WARP更像是一个独立于计算机的设备,很难与主计算机中的上层网络协议栈无缝相连。另外,WARP也没有提供对FPGA中硬件编程的友好支持。

除此之外,还有一些其他结构的无线开发平台,例如DSP、GPU等。DSP和ASIC芯片一样,能够提供非常好的性能,但是内部算法和结构无法修改,无法达到灵活性的要求。而基于GPU的无线开发平台也有其局限性。GPU的数据并行计算结构并不适用于无线底层的计算模型,而且GPU本身无法和射频前端直接相连,这样就需要一种办法将GPU中的计算结果迅速地传递给射频前端,这将会导致非常大的延迟。

综上所述,当前的无线底层平台未能在高性能、高可定制性、高兼容性和开放性上均达到令人满意的指标。

1.4 GRT系统针对于其他无线网络底层平台的弊端,本文自主设计了GRT系统。GRT系统是一个具备高可定制性、高兼容性与开放性,同时又能达到无线协议所需的性能要求的无线网络底层软硬件平台。

GRT系统的前期相关工作已经在HEART 2014[7]和ICFPT 2014[8]两处国际会议中做过介绍。第一篇文章重点叙述GRT的体系结构设计;第二篇文章重点叙述802.11a/g协议在GRT平台上实现的应用。

本文将重点介绍GRT在高性能、高可定制性、高兼容性与开放性这3方面的相关技术,同时还展示评测了GRT系统的最新成果。

2 系统设计 2.1 设计目标1) 高性能

对于一个无线网络底层平台来说,高吞吐率和低延迟是两个非常重要的指标。随着无线网络协议的迅猛发展,未来的无线平台应当提供至少100 Mbps的数据吞吐率及微秒量级的延迟。采用普通的CPU作为计算平台是远远达不到要求的,即便是采用硬件作为计算工具,也需要对算法、底层结构进行精心设计,才可以满足系统在无线环境中真实全速率通信的要求。

2) 高可定制性

作为无线领域的研发者,总是希望在最短的时间内在平台上完成自主定制的协议设计。这就要求系统给用户提供良好的用户接口,并保证良好的高可定制性,即研发者可以方便地修改、添加、移除相关的软硬件功能模块;也能方便地修改、调整底层软硬件平台的参数。

3) 高兼容性与开放性

对于整个网络系统来说,仅有无线网络底层的研究是不够的。无线网络底层必须和上层协议的研究相结合。因此,研究的目标是能够将底层无线平台和上层网络协议栈无缝对接,使得研发者能够灵活自主地完成网络跨层次优化。这就要求GRT系统能够定制成标准的网络协议软硬件平台,并提供开放接口,易于上层网络获取信息及控制。

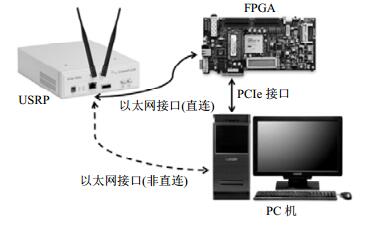

2.2 GRT系统设计 2.2.1 GRT系统整体结构GRT系统如图 1所示,主要由PC机、FPGA和USRP共3部分组成。

|

| 图1 GRT系统结构 |

PC机主要进行网络上层协议栈的相连以及完成一些控制与调度的工作。GRT系统在PC机中提供了一个TCP/IP标准网络驱动,用于协调MAC层与TCP/IP层之间的交互,在不考虑性能的情况下,PC机端也能基于软件完成所有的PHY层、MAC层算法。另外,在PC端,GRT系统提供了一个友好的图形化编程软件和测试软件,用户可以基于GRT系统快速自主开发新的网络协议或算法。

FPGA是GRT系统底层网络协议的主要计算平台,PHY层的基带处理算法和MAC层的调度算法均在FPGA中实现。FPGA与计算机之间采用PCIe接口连接,GRT系统提供了一个高速的PCIe接口驱动,使得计算机和FPGA之间能够高速、低延迟的传输数据,在全双工模式下,可提供高达43.02 Gbps的传输速率[9]。

USRP是一个通用软件无线电外设,它完成了上下变频和射频信号的收发等工作。当USRP作为发送设备时,它从以太网口获得基带采样信号,最终形成射频信号发送出去;当USRP作为接收设备,它从空口获得射频信号,转换成基带采样信号后,从以太网口传递出来。在GRT系统中,提供两种不同的USRP连接方式,包括以太网直连方式与非直连方式。使用直连方式时,USRP和FPGA直接连接;使用非直连方式时,USRP与PC机连接。在非直连的情况下,FPGA和USRP之间的交互需要经过PC机的协调才能完成。

2.2.2 GRT系统的高性能设计GRT系统的高性能体现在高吞吐率和低延迟两个方面。为了达到高性能这一设计目标,系统采用了多时钟域流水线结构和USRP与FPGA直连的设计方案。

1) 多时钟域流水线结构。在GRT系统的FPGA中,PHY层采用模块化设计方案,模块之间采用异步FIFO进行连接,模块与模块之间采用流水线结构。由于PHY层不同的模块的数据吞吐率是不同的,因此采用了多时钟域技术,解决不同模块之间的速率匹配问题。这样可以保证GRT系统不被吞吐率最低的模块的速率所限制,达到高吞吐率的特征。

2) USRP与FPGA直连。如图 1所示,GRT系统提供了两种不同的USRP连接方式,与FPGA直连或者非直连。采用非直连的方式时,每当基带采样信号需要在USRP和FPGA之间传递时,都需要通过计算机完成数据的传递。整个传递过程需要完成FPGA与PC机之间的数据传递、PC机与USRP之间的数据传递两个步骤。若采用直连方式,FPGA直接通过以太网接口与USRP相连,基带采样信号直接在FPGA于USRP之间传递,不再经过PC机。这样的设计大大减少了数据绕路所造成的延时。

在802.11a/g协议中,ACK帧需要在数据帧发完后的16 us(SIFS时间)被发出。根据测试,采用非直连的方式时,ACK的响应时间约为600~800 us;而采用直连的方式时,此时间会缩短到几十微秒。

2.2.3 GRT系统的高可定制性设计为了达到自主可定制这一设计目标,系统采用了以下设计方案。

1) 软硬件协同设计。GRT的每一个模块既可以在硬件中实现,也可以在软件中实现。软硬件之间采用高速PCIe总线进行通信,且软硬模块可以随时切换。

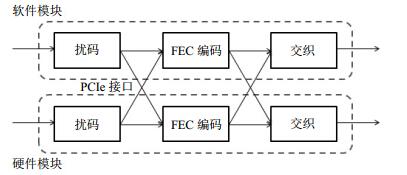

如图 2所示,PHY层的发送端前3个模块分别是扰码、FEC编码和交织。在GRT系统中,所有模块可以全部采用软件进行开发、也可以全部采用硬件进行开发,分别对应上半部分、下半部分的流水线结构。除此之外,GRT系统还提供软硬件交错开发的模式,所有模块都可以自由地在软硬件之间进行切换。例如扰码和交织模块选用软件模块、而FEC编码选用硬件模块。

|

| 图2 软硬件协同开发结构 |

这样的设计为开发者提供了一套非常灵活的结构,即开发者需要对协议进行修改时,可以任意选择在软件或者硬件中做开发,并支持开发者从快速的纯软件开发开始,逐步修改相应模块转为高性能的硬件流水线。

对于FPGA硬件编程,GRT还支持采用C/C++编写硬件模块(C-to-RTL,例如AutoESL或者Vivado HLS[10])。

2) 软件设计框架。对于FPGA中的PHY层的模块,GRT提供一套开发环境,能够自动地生成硬件的互连部分并将硬件模块组成流水线。这样,用户在设计PHY层模块的时候,就不必关注到硬件具体的设计的细节当中,能够将精力集中在模块算法的设计当中。这样的设计既保证了高吞吐率的特性,又保证了良好的可编程性。

2.2.4 GRT系统的高兼容性与开放性设计GRT提供了一个标准的Linux网络设备驱动,能够和主计算机中的TCP/IP层进行交互。加载驱动后,GRT系统能够作为一个可定制无线网卡使用。当定制为标准无线网卡时,能够和商业WiFi设备进行交互。

GRT系统还提供开放的字符型设备驱动,提供信息和控制接口,使进一步对无线网络底层进行管控成为了可能(例如与软件定义网络SDN进行对接)。

3 系统评测 3.1 评测环境GRT的测试环境如图 3所示,包括普通的PC机、FPGA开发板和USRP。PC机上安装有Linux 12.04版本的操作系统,FPGA开发板的型号为Xilinx ML605,USRP的母板型号为USRP N210[11],射频子板型号为XCVR 2450。

|

| 图3 GRT系统测试环境 |

FPGA开发板直接插在计算机主机的PCIe插槽中,USRP和FPGA之间采用以千兆太网线直接相连。这样,每一台PC机就对应了一个无线系统的终端。

3.2 GRT对802.11a/g的支持作为应用示例,在GRT系统上“定制”了标准的802.11a/g无线协议。

3.2.1 理论速率测试表 1、表 2给出了基于GRT系统的802.11a/g的硬件PHY层理论性能测试。由于PHY层采用模块化流水线结构设计,整个PHY层性能限制于模块中吞吐率最慢的模块。因此,PHY层流水线在这个设计中最高可能达到的吞吐率为125 Mbps(802.11a/g标准中的最高吞吐率为54 Mbps)。

| 表1 PHY层发送端主要模块性能评测 |

| 表2 PHY层接收端主要模块性能评测 |

实验采用两台基于802.11a/g协议的GRT系统,一台作为发送端,一台作为接收端。无线收发采用标准802.11a/g MAC层协议的DCF(分布式协调功能)机制。

测试环境为室内,频段为WiFi支持的标准频段信道10(即中心频率为2.457 GHz)。测试采用64-QAM的调制方式、3/4的卷积编码率,数据帧的长度为4 095 byte。本文在不同的带宽下,测试GRT系统的单向传输速率。

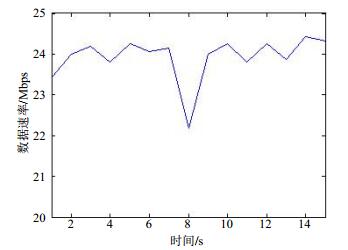

图 4是在12.5 MHz的带宽情况下,单向传输的速率统计情况。实验中设置传输总时间为15 s,每秒统计一次平均速率。图 4主要展现了传输平均速率随时间变化的结果。

|

| 图4 12.5 M带宽时GRT系统单向速率测试 |

表 3表示在不同带宽时,单向传输速率的测试结果。测试结果包括平均速率以及最大瞬时速率。

| 表3 不同带宽时单向传输速率测试 |

由于采用的射频前端USRP N210母板对20 MHz的频宽支持不好,导致其平均速率受限。最高的平均速率在12.5 MHz的频宽处。

3.2.3 GRT系统与商业WiFi设备的交互实验遵循802.11a/g协议,采用20 MHz的带宽,将GRT系统配置为AP模式。实验中,将AP的SSID设置为“GRT_AP”,之后手机可以通过WiFi搜索到该SSID,成功连接上“GRT_AP”并通过浏览器访问网络。

图 5的左半部分显示了手机连上GRT_AP的信息,GRT_AP为手机分配了IP地址。图 5的右半部分显示手机通过GRT_AP访问视频网站,流畅地观看网络视频。

|

| 图5 手机通过GRT_AP上网 |

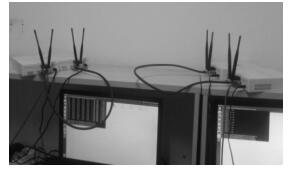

GRT平台已经在软件端实现了2*2 MIMO,根据实验,接收端可以成功解调发送端通过无线信道发出的数据。GRT的MIMO系统实际测试环境如图 6所示。

|

| 图6 基于GRT的MIMO系统 |

图 7是某次MIMO接收端信道估计得到的4组信道参数(H11、H21、H12、H22)的模值。

|

| 图7 2*2 MIMO信道估计参数 |

GRT系统是一个无线网络底层软硬件开放平台,为定制无线的研发者和特殊需求的使用者提供了高性能、可定制的无线网络底层环境。目前已经在GRT系统上实现了一套完全自主编写的基于802.11a/g协议的硬件代码,性能超过了协议的要求,且能够与商用WiFi设备进行互通。GRT系统对802.11n协议的支持正处于开发过程中。

未来的GRT系统将会继续发展。实现更高的速率、更好的编程性,并为用户提供更加丰富、开放的可定制功能。

| [1] |

ABI Research. Wi-Fi Chipset Shipments will near 18 Billion Chipsets during the Next Five Years[EB/OL]. [2014-05-05]. https://www.abiresearch.com/press wi-fi-chipset-shipments- will-near-18-billion-chips.

|

| [2] |

MITOLA J I. Software radios-survey, critical evaluation and future directions[C]//Aroa and Lron Ym Magazn. [S. l. ]: IEEE, 1992.

|

| [3] |

GNU Radio. GNU Radio[EB/OL]. [2014-01-07]. http://gnuradio.org.

|

| [4] |

TAN Kun, LIU He, ZHANG Jian-song, et al. Sora: High- performance software radio using general-purpose multicore processors[J].

Communications of the ACM, 2011, 54(1): 99–107.

DOI:10.1145/1866739 |

| [5] |

FANG Ji, TAN Zhen-hui, TAN Kun. Soft MIMO: a software radio implementation of 802. 11n based on Sora platform[C]//Wireless, Mobile and Multimedia Networks, 4th IET International Conference. Beijing: IET, 2011.

|

| [6] |

Mango Communications. Warp v3 Kit[EB/OL]. [2014- 01-01]. http://mangocomm.com/products/kits/warp-v3-kit.

|

| [7] |

WANG Tao, SUN Guang-yu, CHEN Jia-hua, et al. GRT: A reconfigurable SDR platform with high performance and usability to be published in ACM SIGARCH computer architecture news[J].

ACM SIGARCH Computer Architecture News, 2014, 42(4): 52–56.

|

| [8] |

CHEN Jia-hua, WANG Tao, WU Hao-yang, et al. A high-performance and high-programmability reconfigurable wireless development platform(demo paper)[C]// International Conference on Field-Programmable Technology(ICFPT). Shanghai: IEEE, 2014.

|

| [9] |

GONG Jian, WANG Tao, CHEN Jia-hua, et al. An efficient and flexible host-FPGA PCIe communication library[C]// Field Programmable Logic and Applications (FPL). [S. l. ]: IEEE, 2014: 1-6.

http://ieeexplore.ieee.org/document/6927459/ |

| [10] |

XILINX. Xilinx High-Level Synthesis (HLS)[EB/OL]. [2014-02-21]. http://www.xilinx.com/tools/autoesl_instructions.htm.

|

| [11] |

Ettus Research. USRP N210[EB/OL]. [2014-01-01]. http://www.ettus.com/product/details/UN210-KIT.

|

2015, Vol. 44

2015, Vol. 44