余数系统(residue number system,RNS)是一种非权重数值表征系统,它将传统的较大位宽的乘加运算分解为多个较小位宽的并行通道进行处理,从而降低了复杂度和计算的关键路径,可获得高速、低功耗的VLSI(very large scale integrated circuits)实现性能。因此,近年来余数系统在乘加密集型的数字信号处理(digital signal processing, DSP)系统中得到了广泛研究[1-3]。然而,在DSP系统的运算过程中,数值的动态范围会随着乘、加等基本运算而增加。这是RNS在DSP系统中应用面临的基本问题之一,如何高效地实现RNS动态范围的扩展对于其在DSP系统中应用有重要意义。

由于余数系统具有非权重的特性,故需要采用特殊的基扩展技术解决该问题。余数系统基扩展方法可以分为两类:第一类保留原余数基,通过增加新的余数基分量来扩大余数系统的动态范围[4-9];第二类保留原余数系统的通道数量不变,通过增加原余数基的数据位宽来实现动态范围的扩大。

目前关于余数动态范围的扩展主要集中在第一类方法的研究上。文献[4]提出了Szabo-Tanaka算法,该算法利用了混合基转换(mixed radix conversion, MRC)和一个附加修正单元现基扩展,其实质为先做余数系统到二进制系统转换(residue to binary,R2B),恢复出原数据后再对新余数基求模,算法复杂度较高。文献[5]讨论了两通道余数基

第一类基扩展方法的研究均采用余数系统后向转换算法为理论基础。在其实现中通常需要余数系统到二进制系统转换和二进制到余数系统转换(binary to residue,B2R)过程,算法复杂度太高。第二类余数基扩展方法则保留了原余数基的原有特点,仅增加各通道的位宽,保留了原余数基运算通道的电路结构,且不需要考虑扩展基与原始基的互质条件。另一方面,在DSP应用中如乘法级联为特征的离散付氏变换、离散余弦变换和离散小波变换等,需要方便高效地将余数通道的数据位宽扩大一倍。因此,第二类基扩展具有重要的应用价值,目前对这一方法的研究还较少。

针对目前研究最多且最为深入的一组基

余数系统由一组两两互质的余数基

在CRT中,主要问题是模M运算,当动态范围较大时,降低RNS的并行特性。而余数系统有与之相对应的混合基系统,它们具有相同的动态范围,于是有混合基转换(mixed radix conversion, MRC)。

令RNS余数基为

| $ \left\{ \begin{array}{l} {z_1} = {x_1}\\ {z_2} = {\left\langle {{{\left\langle {m_1^{ - 1}} \right\rangle }_{{m_2}}}({x_2} - {z_1})} \right\rangle _{{m_2}}}\\ {z_3} = {\left\langle {{{\left\langle {{{({m_2}{m_1})}^{ - 1}}} \right\rangle }_{{m_3}}}({x_3} - ({z_2}{m_1} + {z_1}))} \right\rangle _{{m_3}}}\\ \;\;\;\;\;\;\;\;\;\;\;\;\;\;\vdots \\ {z_L} = {\left\langle {\begin{array}{*{20}{l}} {{{\left\langle {{{({m_{L - 1}} \cdots {m_2}{m_1})}^{ - 1}}} \right\rangle }_{{m_L}}} \times }\\ {({x_{L - 1}} - ({z_{L - 1}}{m_{L - 2}} \cdots {m_1} + \cdots + {z_2}{m_1} + {z_1}))} \end{array}} \right\rangle _{{m_n}}} \end{array} \right. $ | (1) |

基扩展定义为:由基为

令整数X在原始余数系统

| $\left\{ \begin{array}{l} {z_1} = {x_3}\\ {z_2} = {\left\langle {{{\left\langle {m_3^{-1}} \right\rangle }_{{m_1}}}({x_1}-{z_1})} \right\rangle _{{m_1}}} \end{array} \right. $ | (2) |

可知

| $ \begin{array}{c} {x_1} = {z_2}({2^n} + 1) + {z_1} = \\ {\left\langle {{2^{n-1}}({x_1}-{x_3})} \right\rangle _{{2^n}-1}}({2^n} + 1) + {x_3} \end{array} $ | (3) |

对于式(3),可进行适当优化,以简化VLSI实现结构。对于

| $ {\left\langle {{2^{n-1}}({x_1}-{x_3})} \right\rangle _{{2^n}-1}} = {\left\langle {{2^{n - 1}}{{\left\langle {{x_1} - {x_3}} \right\rangle }_{{2^n} - 1}}} \right\rangle _{{2^n} - 1}} $ | (4) |

由端回进位的性质可知,令

对于

| $ {\left\langle {{x_1}-{x_3}} \right\rangle _{{2^n}-1}} = {\left\langle {{x_1}-{{\left\langle {{x_3}} \right\rangle }_{{2^n} - 1}}} \right\rangle _{{2^n} - 1}} $ | (5) |

模

| $ {\left\langle {{x_1}-{{\left\langle {{x_3}} \right\rangle }_{{2^n}-1}}} \right\rangle _{{2^n}-1}} = {\left\langle {{x_1} + \overline {{{\left\langle {{x_3}} \right\rangle }_{{2^n} - 1}}} } \right\rangle _{{2^n} - 1}} $ | (6) |

式中,当

由于

经优化后的

|

|

图1

|

由于

| $ \left\{ \begin{array}{l} X = {{a'}_1}({2^{2n}}-1) + {{x'}_1}\;\;\;\;\;\;\;\;\;\;\;\left( {7{\rm{a}}} \right)\\ X = {a_2}{2^n} + {x_2}\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\left( {7{\rm{b}}} \right) \end{array} \right. $ |

式中,

| $ {a'_1}({2^{2n}}-1)-{a_2}{2^n} = {x_2}-{x'_1} $ | (8) |

| $ {\left\langle {-{{a'}_1}} \right\rangle _{{2^n}}} = {\left\langle {{x_2}-{{x'}_1}} \right\rangle _{{2^n}}} $ | (9) |

由于

| $ {a'_1} = {2^n}-{\left\langle {{x_2}-{{x'}_1}} \right\rangle _{{2^n}}}{\rm{ = }}{\left\langle {{{x'}_1}-{x_2}} \right\rangle _{{2^n}}} $ | (10) |

对于基为

| $ \left\{ \begin{array}{l} X = {{a'}_1}({2^{2n}}-1) + {{x'}_1}\;\;\;\;\;\;\;\;\;\left( {11{\rm{a}}} \right)\\ X = {{a'}_2}{2^{2n}} + {{x'}_2}\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\left( {11{\rm{b}}} \right) \end{array} \right. $ |

式中,

| $ {x'_2} = {\left\langle {{{a'}_1}({2^{2n}}-1) + {{x'}_1}-{{a'}_2}{2^{2n}}} \right\rangle _{{2^{2n}}}}{\rm{ = }}{\left\langle {{{x'}_1}-{{a'}_1}} \right\rangle _{{2^{2n}}}} $ | (12) |

对于基为

| $ {x'_3} = {\left\langle {{{a'}_1}({2^{2n}}-1) + {{x'}_1}-{{a'}_3}({2^{2n}} + 1)} \right\rangle _{{2^{2n}} + 1}}{\rm{ = }}{\left\langle {{{x'}_1}-2{{a'}_1}} \right\rangle _{{2^{2n}} + 1}} $ | (13) |

由上所述,22n及22n+1通道的扩展需要3个模减运算:模2n减法、模22n减法和模22n+1减法。由于目前对模减法没有专门深入的研究,通常将其转化为模加法进行设计。

对式(10),有

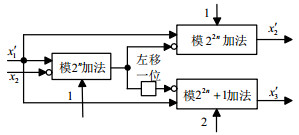

由此,3个模减法器均转化为模加法器,具体实现电路如图 2所示,其电路结构非常简单。

|

| 图2 22n及22n+1通道扩展VLSI实现结构 |

由2.1节和2.2节的分析可知,本文的扩展算法中,需先扩展出

|

| 图3 整体设计VLSI实现结构 |

由图 2可知,本文提出的扩展算法需要一个x3输入预处理模块,一个模

综上所述,本文提出的基扩展需要的面积和关键时延分别为:

| $ \begin{array}{c} {A_{{\rm{proposed}}}} = [1.5(2n-1)\log (2n-1) + \\ 9n\log n + 66n-11]{A_g} \end{array} $ | (14) |

| $ {\tau _{{\rm{proposed}}}} = [2\log (2n-1) + 6\log n + 27]{\tau _g}$ | (15) |

根据本文提出的基扩展算法,若原始余数系统动态范围为3n bits,则扩展后动态范围为6n bits。那么扩展每比特位宽所消耗资源为:

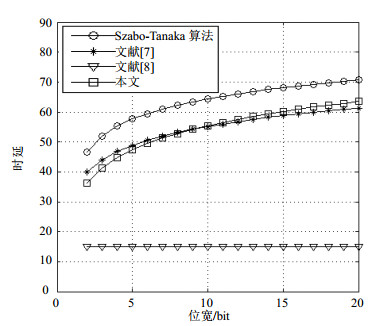

对于Szabo-Tanaka算法,文献[7]及文献[8]均为第一类基扩展,而本文提出的算法为第二类基扩展。限定原始余数基均为

表 1给出了本文算法、Szabo-Tanaka算法,文献[7]及文献[8]提出的算法在扩展3n比特位宽的条件下的硬件消耗、时延性能对比(基于单位门模型)。

| 表1 硬件性能及扩展基对比 |

在集成电路实现中,查找表中每比特存储单元所需CMOS管为6个[15],而相对应的单位门模型中简单门同样需要6个CMOS管,故可大致认为查找表中每比特存储单元的面积消耗对应于单位门模型的面积为Ag;同时可设查找表的平均查找时延为

图 4图 5分别给出了随着n增加,各算法基于单位门模型分析的时延和面积对比。可以看出本文算法在实现上具有最优的面积性能,其面积消耗随n的增加,基本为线性增加。其余3种算法由于使用查找表,实现面积随n的增加均为指数增加,随着n的增加,文献[8]所需的面积增长最快,文献[7]与Szabo-Tanaka算法所需的面积较为接近。而在时延上,文献[8]最优,文本算法在位宽10 bits以下,比文献[7]更优,位宽再增加,则比文献[7]略高,但总体与其相差不大,Szabo-Tanaka算法时延性能最差。

|

| 图4 基于单位门模型的时延对比 |

|

| 图5 基于单位门模型的面积对比 |

由于Szabo-Tanaka算法为较经典的第一类基扩展算法,其他第一类基扩展算法大多基于该思想进行设计,因此其对第一类基扩展算法具有较好的代表性。为了进一步进行性能分析和对比,基于VHDL语言对本文所提出的基扩展算法和经典的Szabo-Tanaka算法进行设计,其中所需的模

| 表2 ASIC综合结果 |

由表 2可见,本文提出的基扩展方法在时延方面占有较大优势,但面积与理论分析较为不同,分析原因是由于Szabo-Tanaka算法中的模加法器形式较为统一,因此综合软件采用了较多的复用,从而使得实际综合面积比理论分析面积小。

4 结论本文提出了一种基为

| [1] |

CONWAY R, NELSON J. Improved RNS FIR filter architectures[J].

IEEE Transactions on Circuit and Systems Ⅱ, 2004, 51(1): 26–28.

DOI:10.1109/TCSII.2003.821524 |

| [2] |

MADHUKUMAR A S, CHIN F. Enhanced architecture for residue number system-based CDMA for high-rate data transmission[J].

IEEE Transactions on Wireless Communications, 2004, 3(5): 1363–1368.

DOI:10.1109/TWC.2004.833509 |

| [3] |

MA Shang, HU Jian-hao, LING Xiang, et al. The applications of RNS in SDR systems[C]//2008 International Workshop on Software Radio Technology (SRT2008). Beijing: [s. n. ], 2008: 49-54.

|

| [4] |

SZABO N S, TANAKA R I.

Residue arithmetic and its applications to computer technology[M]. New York: McGraw-Hill, 1967.

|

| [5] |

O'KEEFE K H, WRIGHT J L. Remarks on base extension for modular arithmetic[J].

IEEE Trans Comput, 1973, 22: 833–835.

|

| [6] |

O'KEEFE K H. A note on fast base extension for residue number systems with three moduli[J].

IEEE Trans Comput, 1975, 24: 1132–1133.

|

| [7] |

SHENOY A P, KUMARESAN R. Fast base extension using a redundant modulus in RNS[J].

IEEE Trans Comput, 1989, 38: 292–296.

DOI:10.1109/12.16508 |

| [8] |

BARSI F, PINOTTI M C. Fast base extension and precise scaling in RNS for look-up table implementations[J].

IEEE Trans Signal Processing, 1995, 43: 2427–2430.

DOI:10.1109/78.469842 |

| [9] |

LAI Yu-feng, KONG Yi-nan. An implementation of a scaler in the residue number system[C]//International Symposium on Communications and Information Technologies. [S. l. ]: [s. n. ], 2012: 529-532

|

| [10] |

WANG Yu-ke. New Chinese remainder theorems[C]// Conference Record of the Thirty-Second Asilomar Conference on Signals, Systems & Computers. Pacific Grove: [s. n. ], 1998, 1: 165-171.

|

| [11] |

MA Shang, HU Jian-hao, ZHANG Lin, et al. An efficient RNS parity checker for moduli set |

| [12] |

MA Shang, HU Jian-hao, WANG Chen-hao. A novel modul |

| [13] |

PATEL R A, BOUSSAKTA S. Fast parallel-prefix architectures for modulo |

| [14] |

EFSTATHIOU C, VERGOS H T, NIKOLOS D. Fast parallel-prefix modulo |

| [15] |

WESTE H E, HARRIS D M.

CMOS VLSI Design[M]. 2nd ed. [S.l.]: Addison Wesley, 2005.

|

2015, Vol. 44

2015, Vol. 44