# 10 kV SiC LBD-MOSFET 结构 设计与特性研究

文 译<sup>1\*</sup>, 陈致宇<sup>1</sup>, 邓小川<sup>1,2</sup>, 柏 松<sup>3</sup>, 李 轩<sup>1,2</sup>, 张 波<sup>1</sup>

(1. 电子科技大学电子科学与工程学院 成都 610054; 2. 电子科技大学广东电子工程信息研究院 广东 东莞 523808; 3. 南京电子器件研究所宽禁带半导体电力电子器件国家重点实验室 南京 210016)

【摘要】针对 SiC MOSFET 体二极管双极退化效应,该文提出了一种集成低势垒二极管的 10~kV SiC MOSFET 器件新结构 (LBD-MOSFET)。该结构通过在一侧基区上方注入 N 阱,降低了漏源间的电子势垒,从而在元胞中形成一个低势垒二极管 (LBD)。当 LBD-MOSFET 在第三象限工作时,低的电子势垒使 LBD 以更低的源漏电压开启,有效避免了体二极管开通 所导致的双极退化效应。二维数值分析结果表明,SiC LBD-MOSFET 的击穿电压达 13.5~kV,第三象限开启电压仅为 1.3~V,相比传统结构降低 48%,可有效降低器件第三象限导通损耗。同时,由于 LBD-MOSFET 具有较小的栅漏交叠面积,其栅漏电容仅为  $1.0~pF/cm^2$ ,器件的高频优值为  $194~m\Omega\cdot pF$ ,性能相比传统结构分别提升了 81% 和 76%。因此,LBD-MOSFET 适用于高频高可靠性电力电子系统。

关键词 击穿电压; 栅漏电容; 低势垒; 碳化硅; 第三象限 中图分类号 TN386 文献标志码 A doi:10.12178/1001-0548.2021084

## Design and Characteristics of a Novel 10 kV SiC MOSFET Embedding Low Barrier Diode

WEN Yi<sup>1\*</sup>, CHEN Zhi-yu<sup>1</sup>, DENG Xiao-chuan<sup>1,2</sup>, BAI Song<sup>3</sup>, LI Xuan<sup>1,2</sup>, and ZHANG Bo<sup>1</sup>

- (1. School of Electronic Science and Engineering, University of Electronic Science and Technology of China Chengdu 610054;

- Institute of Electronic and Information Engineering in Guangdong, University of Electronic Science and Technology of China Dongguan Guangdong 523808;

- 3. State Key Laboratory of Wide-Bandgap Semiconductor Power Electronic Devices, Nanjing Electronic Devices Institute Nanjing 210016)

**Abstract** In this paper, a novel 10 kV SiC MOSFET embedding low barrier diode (LBD-MOSFET) is proposed and researched to solve the bipolar degradation effect in SiC MOSFET. The low barrier diode (LBD) in the cell is formed by introducing an N\_well above the P\_base region on one side, which reduces the electron barrier between the drain and the source. When the LBD-MOSFET works in the third quadrant, the low electronic barrier makes the LBD turn on with a lower source-drain voltage, thus effectively avoiding the bipolar degradation effect caused by the turn-on of the body diode. 2D numerical analysis results show that the breakdown voltage of the SiC LBD-MOSFET reaches 13.5 kV. In the third quadrant, the turn-on voltage is only 1.3 V, which is 48% lower than the traditional structure and effectively reduces the conduction loss of the device. At the same time, since the gatedrain overlap area of the LBD-MOSFET is reduced compared to the traditional MOSFET, the  $C_{gd}$  is only 1.0 pF/cm<sup>2</sup> and the high-frequency merit value of the device is 194 m $\Omega$ ·pF, which are reduced by 81% and 76% compared with the traditional MOSFET, respectively. Therefore, the LBD-MOSFET is suitable for high-frequency and high-reliability power electronic systems.

**Key words** breakdown voltage; gate-source capacitance; low barrier diode; SiC; The third quadrant

2020年3月4日,我国政府提出加快5G网络、特高压、大数据中心、城际高速铁路和城市轨道交通、新能源汽车充电桩、人工智能、工业互联网等新型基础设施建设进度<sup>[1]</sup>,简称"新基建"。

新基建本质上是信息数字化的基础设施建设,这些 设施都需要应用大量功率半导体器件和设备,尤其 是在智能电网、高速动车牵引、工业级电源、舰载 武器等领域,需要功率更大、速度更快、功能更丰

收稿日期: 2021-03-26; 修回日期: 2021-04-01

基金项目: 国家科技重点研发计划 (2017YFB0102302); 广东省自然科学基金 (2019A1515012085)

作者简介: 文译 (1990-), 男, 博士生, 主要从事 SiC 功率半导体器件方面的研究. E-mail: wenyi@uestc.edu.cn

富、效率更高的功率半导体器件。尽管体硅基或者 基于绝缘衬底上的硅功率器件目前仍然是功率器件 市场的主力军四,但由于材料特性的限制,硅功率 器件在耐压、工作频率以及转换效率等方面已经逼 近器件性能极限,往大功率、高频化发展的局限性 越来越显现。碳化硅 (SiC) 半导体材料以其高临界 击穿电场、高热导率以及高饱和电子漂移率等优 势,在超高压大功率电力电子应用领域表现出很大 潜力。纵观国内外整个产业,商业化的 SiC 功率器 件额定电压等级目前仍集中在 650~3 300 V 中高 压领域,类型包括二极管和 MOSFET 等。尽管 Si 器件通过串联形式可以将模块电压做到 10 kV 以 上,但是元器件数量众多,系统结构繁杂,寄生效 应多。10 kV 碳化硅器件无需复杂的串并联结构, 减少了系统元器件数目,简化了电路拓扑结构,提 高了电能转换效率。目前 10 kV 以上的超高压功率 器件, 仍处于研发试制阶段。2004年, 文献 [3] 在 110 μm/6×10<sup>14</sup> cm<sup>-3</sup> 的 4H-SiC 外延衬底上设计并 制备出世界第一个超高压 10 kV SiC MOSFET,常 温下器件的比导通电阻为 236 m $\Omega$ ·cm<sup>2</sup>@ $V_{GS}$ =25 V, 國值电压为 10 V, 泄漏电流为 70  $\mu$ A@ $V_{DS}$ =10 kV。 2011年,美国 Cree 公司、Powerex 公司、GE 公司 和美国 NIST 联合基于 4 英寸的 120 μm/6×10<sup>14</sup> cm<sup>-3</sup> 的 4H-SiC 外延衬底上研制出 10 kV SiC MOSFET 用于功率为 1 MW 的固态变电站<sup>[4]</sup>,该芯片面积为 8.1 mm×8.1 mm, 比导通电阻为 123 mΩ·cm², 阈值 电压为 3 V。当漏源电压为 4 V,该 MOSFET 获得 导通电流为  $10A@V_{GS}=20~V$ 。 2017 年,日本先进 功率电子研究中心在 150 μm/6.7×10<sup>14</sup> cm<sup>-3</sup> 的 4H-SiC 外延衬底上研制出一种在 JFET 区具有逆向掺 杂分布的 13.1 kV 的超高压 SiC MOSFET<sup>[5]</sup>,其漏 电流为 10 μA/cm<sup>2</sup>, 芯片面积为 5 mm×5 mm。室温 下,该器件比导通电阻为 169 m $\Omega$ ·cm<sup>2</sup>@ $V_{GS}$ =20 V,  $V_{DS}$ =1 V。对于 10 kV 量级的功率 MOSFET, 当器 件处于第三象限工作时,由于 MOSFET 的体二极 管存在,第三象限的开启电压一般会高于 2.5 V, 导致器件第三象限导通时的损耗加大。为了解决这 个问题, 行业内开始研究集成二极管的 MOSFET, 目前多数采用的是单片集成 MOSFET 和结势垒肖 特基二极管 (JBS) 或肖特基势垒二极管 (SBD)[6-7]。 然而, 肖特基接触会导致反向泄漏电流的增加和高 温性能的下降[8]。

本文提出了一种集成低势垒二极管的 10 kV SiC MOSFET 器件新结构 (low barrier diode-MOSFET, LBD-MOSFET)。通过二维 TCAD 仿真工具 Silvaco

进行设计和研究,器件击穿电压为 13.5 kV。在第三象限工作时,低的电子势垒使 LBD 以更低的源漏电压开启,避免了体二极管开启导致的双极退化效应。传统平面型 10 kV SiC MOSFET 第三象限的开启电压为 2.5 V,而 LBD-MOSFET 的开启电压仅 1.3 V,相比降低了 48%,可有效降低器件第三象限导通损耗。LBD-MOSFET 的栅漏交叠面积相比传统平面型结构有所减小,可有效降低器件的栅漏电容,从而降低器件开关损耗。

## 1 LBD-MOSFET 机理研究

#### 1.1 第三象限静态特性

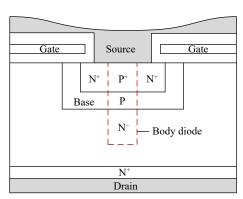

图 1 为常规平面型 SiC MOSFET 结构示意图,由 P<sup>+</sup>区、P\_base 区和 N<sup>-</sup>漂移区形成寄生体 PiN 二极管。当 SiC MOSFET 在第三象限工作时,电流从 MOSFET 的源端经过体二极管 P<sup>+</sup>PN<sup>-</sup>流向漏端。由于 SiC 宽禁带、低本征载流子的特性,其体二极管开启电压远大于 Si MOSFET,导致 SiC MOSFET 在第三象限的导通损耗比 Si MOSFET 更高。基平面位错 (BPD) 是 SiC 晶圆普遍存在的缺陷,当传统 SiC MOSFET 在第三象限工作,作为双极型器件的体二极管 P<sup>+</sup>PN<sup>-</sup>导通,电子和空穴的复合释放的能量导致堆垛层错在 BPD 处蔓延<sup>[9-11]</sup>,这种现象就是双极退化效应。双极退化效应导致 SiC MOSFET的导通电阻增大,体二极管 P<sup>+</sup>PN<sup>-</sup>的开启电压增大,SiC MOSFET第三象限的导通损耗增加,器件反向漏电流也会增加。

图 1 SiC MOSFET 的体二极管示意图

#### 1.2 工作机理

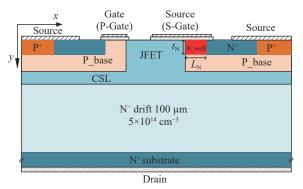

为了解决传统 SiC MOSFET 第三象限开启电压高,避免双极退化效应,本文提出 10 kV SiC LBD-MOSFET,其截面结构如图 2 所示。N\_well上方的多晶硅与源极短接,简称为 S-Gate。引入N well 可以降低第三象限开启电压。N well 在

$N_{well/P_{base}}$  结的内建电势作用下完全耗尽,表现为常关型特性。导通状态,LBD-MOSFET 由左侧  $P_{base}$  反型单沟道导通,虽然牺牲了一侧导电沟道,但仍有效利用了 JFET 区和漂移区的导电通路。反向阻断状态,器件仍主要由  $N_{con}$  drift 区承担阻断电压  $V_{DS}$ 。当器件工作在第三象限,随着  $V_{SD}$  增大,电子在  $N_{con}$  well 表面积累,形成沟道,电流 $I_{SD}$  的路径是从  $N_{con}$  4% 过  $N_{con}$  well、JFET 区流向漏极。因此集成的 LBD 可以降低第三象限开启电压,消除双极退化效应。

图 2 10 kV SiC LBD-MOSFET 截面示意图

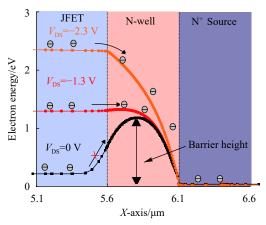

图 3 标出了 SiC LBD-MOSFET 在不同源漏电压下,导带能级  $(E_C)$  沿 SiO<sub>2</sub>/SiC 表面的分布。纵坐标"0"是费米能级的位置,当源漏电压为0 时,N<sup>+</sup>区作为重掺杂区域,其导带位置低,趋近于零,而 JFET 区掺杂轻,其导带位置相比 N<sup>+</sup>区更高。LBD 的势垒高度随着  $V_{SD}$  增加而降低,而低的电子势垒会使 LBD 以更低的源漏电压开启,当第三象限  $V_{DS}$  达到-1.3 V时,LBD 的势垒消失,单极型传导开始。

图 3 导带能级  $E_C$  沿  $SiO_2/SiC$  表面的分布

基于泊松方程,LBD势垒高度的一维表达式为:

$$V_{\text{LBD}} = \frac{\varphi_{\text{Si|SiC}} - \frac{qN_{\text{Nwell}}t_{\text{N}}^{2}}{2\varepsilon_{\text{SiC}}}}{\frac{\varepsilon_{\text{ox}}t_{\text{N}}}{\varepsilon_{\text{SiC}}t_{\text{ox}}} + 1} + \chi_{\text{Si|SiC}}$$

(1)

式中, $V_{LBD}$ 是势垒高度; $\varphi_{Si|SiC}$ 和  $\chi_{Si|SiC}$ 分别是 Si 和 SiC 的功函数之差和电子亲和能之差; $N_{Nwell}$ 和  $t_N$ 分别是  $N_{L}$ well 区的浓度和厚度;q 是单位电子电荷; $\varepsilon_{ox}$  和  $\varepsilon_{SiC}$ 分别是  $SiO_2$  和 SiC 的介电常数。 SiC LBD-MOSFET 相比平面型 SiC MOSFET,具有不同的第三象限开启机制。新结构利用集成的低势垒二极管抑制了体二极管的开启,进而避免了体二极管开启导致的双极退化效应。因此,SiC LBD-MOSFET 的第三象限特性可获得较大提升。

## 2 结果与分析

#### 2.1 LBD-MOSFET 特性

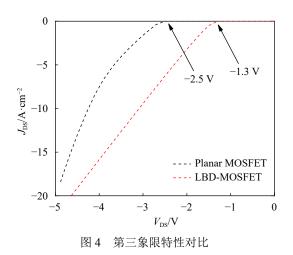

本文设计的 10 kV LBD-MOSFET 结构参数如下: N\_well 浓度为  $5 \times 10^{16}$  cm<sup>-3</sup>; N\_well 厚度  $t_N = 0.2 \, \mu \text{m}$ ; N\_well 长度  $L_N = 0.5 \, \mu \text{m}$ ; 栅氧化层厚度  $t_{\text{ox}} = 60 \, \text{nm}$ ; JFET 宽度  $W_{\text{JFET}} = 2.2 \, \mu \text{m}$ 。作为比较的传统 MOSFET,其结构参数与 LBD-MOSFET 一致。两种结构的第三象限特性对比如图  $4 \, \text{所示}$ 。LBD-MOSFET 由于低的电子势垒而提前导通,从而抑制体二极管开启,拥有更优的第三象限特性。LBD-MOSFET 的第三象限开启电压  $V_{\text{on}}$  为  $1.3 \, \text{V}$ ,相比传统平面型 MOSFET 的开启电压  $V_{\text{on}}$  为  $2.5 \, \text{V}$ ,下降了 48%,可以有效降低器件在第三象限的导通损耗。

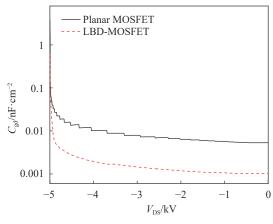

LBD-MOSFET 与传统 MOSFET 的电容特性对比如图 5 所示。由于 LBD-MOSFET 的栅漏两极交叠面积更小,对应栅漏电容  $C_{\rm gd}$  明显小于平面型 MOSFET。当  $V_{\rm DS}$ =5 kV 时,传统平面型 MOSFET

的栅漏电容  $C_{\rm gd}$  为 5.2 pF/cm²,LBD-MOSFET 的  $C_{\rm gd}$  为 1.0 pF/cm²,降低了 81%。传统平面型的高频优值 ( $R_{\rm on} \times C_{\rm gd}$ ) 为 806 m $\Omega$ ·pF,LBD-MOSFET 的高频优值为 194 m $\Omega$ ·pF,降低了 76%,因此 LBD-MOSFET 更适用于高频应用。

图 5 栅漏电容对比

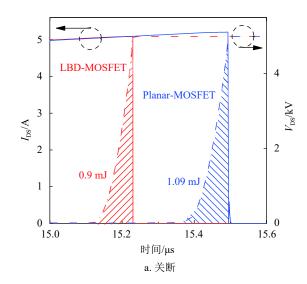

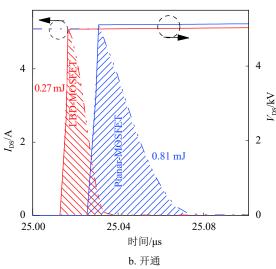

图 6 开关特性对比

LBD-MOSFET 和传统平面型 MOSFET 的开关 波形如图 6 所示。传统平面型 MOSFET 的开启损耗为 0.81 mJ,LBD-MOSFET 的开启损耗为 0.27 mJ,相比降低了 66.7%。传统平面型 MOSFET 的关断损耗为 1.09 mJ,LBD-MOSFET 的关断损耗为 0.90 mJ,相比降低了 17.4%。

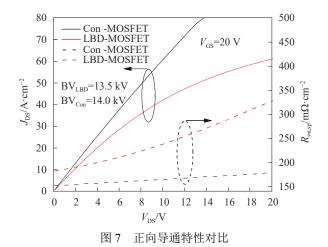

LBD-MOSFET 与传统 MOSFET 的击穿电压和正向导通特性对比如图 7 所示。LBD-MOSFET 击穿电压为 13.5 kV,达到传统平面型 SiC MOSFET 击穿电压的 96%,达到理论平行平面结构的 95.7%。由于缺少一个正向导通沟道,因此 LBD-MOSFET 的正向特性略差于平面型 MOSFET。器件虽然牺牲了一侧导电沟道,但仍有效利用了 JFET 区和漂移区的导电通路,因此在线性区, $V_{\rm GS}$ =20 V, $V_{\rm DS}$ =3 V,LBD-MOSFET 比导通电阻  $R_{\rm on,sp}$ =194 m $\Omega$ ·cm²,是传统 MOSFET 比导通电阻 155 m $\Omega$ ·cm² 的 1.25 倍。

#### 2.2 N well 的设计研究

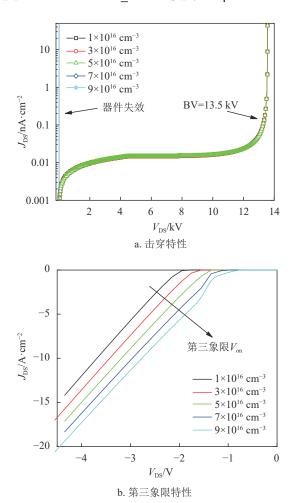

N\_well 浓度越低,器件阻断时,N\_well 区越容易在 N\_well/P\_base 内建电势作用下发生耗尽,N\_well 区没有电子沟道形成,有助于提升器件第一象限的阻断能力。但是 N\_well 浓度降低,会造成 LBD 的势垒升高,导致 N\_well 表面形成积累电子层所需的源漏电压增大,造成第三象限导通损耗增加。因此,N\_well 浓度需要进行折中优化。不同 N\_well 浓度下器件的击穿特性和第三象限特性分别如图 8a 和图 8b 所示。随着 N\_well 浓度的增加,器件的阻断特性迅速退化,当浓度高于  $7 \times 10^{16}$  cm $^{-3}$  后,N\_well 在 PN 结内建电势作用下无法全耗尽,存在电子沟道,器件无法阻断。设定  $I_{\text{SD}}=0.1$  A/cm $^{2}$  对应第三象限开启,当 N\_well 浓度从  $1 \times 10^{16}$  cm $^{-3}$  增加到  $9 \times 10^{16}$  cm $^{-3}$ ,与之对应的第三

象限开启电压分别为 1.95、1.60、1.30、1.14、0.86 V。N\_well 浓度越大,器件第三象限开启电压降低,终其原因是 N\_well 势垒降低。器件结构基本参数如下:漂移区厚度为 100  $\mu$ m,漂移区掺杂浓度为  $5\times10^{14}$  cm<sup>-3</sup>,JFET 区宽度为 2.2  $\mu$ m,JFET 浓度为  $2\times10^{16}$  cm<sup>-3</sup>,沟道长度为 0.5  $\mu$ m,P\_base 浓度为  $2.1\times10^{18}$  cm<sup>-3</sup>,P base 深度为 1.5  $\mu$ m。

图 8 N well 浓度对器件影响

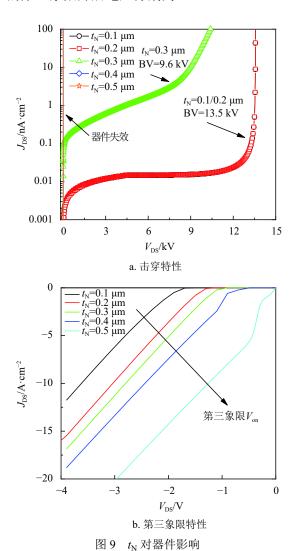

N\_well 厚度  $t_N$  如果太大,N\_well 在 PN 结内建电势作用下可能发生不完全耗尽。器件处于阻断状态时,在靠近 SiC/SiO<sub>2</sub> 表面仍有可动电子,造成器件阻断时 N\_well 发生漏电流,器件提前击穿。当器件工作在第三象限,根据式 (1) 的分析, $t_N$  越大,LBD 的势垒降低,导致第三象限开启电压降低,进而减小器件在第三象限的导通损耗。因此 N\_well 厚度需要折中考虑。不同 N\_well 厚度  $t_N$  对器件阻断特性和第三象限特性分别如图 9a 和图 9b,其中 N\_well 浓度为  $5 \times 10^{16}$  cm<sup>-3</sup>。当  $t_N$ = 0.1  $\mu$ m 或 0.2  $\mu$ m,击穿电压达到 13.5 kV,当  $t_N$ =

$0.3 \, \mu m$ ,击穿电压退化为  $9.6 \, kV$ ,当  $t_N$  高于  $0.4 \, \mu m$ ,  $N_well$  在器件阻断态时无法完全耗尽,在  $N_well$  表面存在电子沟道,器件阻断能力失效。考虑有效 击穿电压,当  $t_N$  从  $0.1 \, \mu m$  增加到  $0.3 \, \mu m$ ,与之对 应的第三象限开启电压分别为  $1.72 \, \sim 1.30 \, \sim 0.98 \, V$ 。

式 (1) 从一维上对 LBD 势垒进行了描述,实际上,N\_well 长度也会对集成二极管的势垒高度有影响。N\_well 长度  $L_{\rm N}$  对 LBD-MOSFET 的击穿特性和第三象限特性影响如图 10a 和图 10b 所示,其中 N\_well 浓度为  $5\times10^{16}$  cm<sup>-3</sup>。N\_well 基于横向尺寸  $L_{\rm N}$  对器件的性能影响相对纵向尺寸较小。击穿特性方面,当  $L_{\rm N}$ =0.1  $\mu$ m,击穿电压低于 9.2 kV, $L_{\rm N}$ =0.3  $\mu$ m,击穿电压增加到 13.3 kV,当  $L_{\rm N}$ > 0.4  $\mu$ m,击穿电压维持在 13.5 kV。考虑到有效击穿电压,当  $L_{\rm N}$  从 0.3  $\mu$ m 增加到 0.6  $\mu$ m,与之对应的第三象限开启电压分别为 0.91、0.92、1.30、1.73 V。

### 2.3 $t_{ox}$ 的设计研究

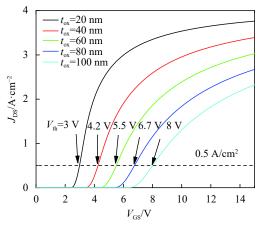

不同栅氧厚度  $t_{\rm ox}$  对应 LBD-MOSFET 的阈值电压如图 11 所示。LBD-MOSFET 的 N\_well 在正向导通时 N\_well 全耗尽,正向电流通过 P\_base 沟道流经 JFET 区,阈值电压与传统 MOSFET 几乎一致,当  $t_{\rm ox}$  低于 60 nm,阈值电压  $V_{\rm th}$  均低于 5 V,考虑到器件容易受环境干扰导致误开启, $t_{\rm ox}$ =60  $\mu$ m 对应阈值电压  $V_{\rm th}$ =5.5 V 较合适。

图 10  $L_N$  对器件影响

图 11 tox 对器件阈值电压影响

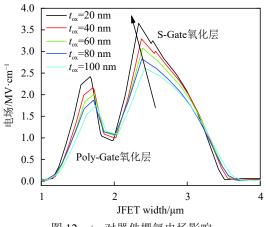

$t_{\rm ox}$  降低将伴随栅氧化层电场的增加,当  $t_{\rm ox}$  低于 60 nm 时,阻断状态下 S-Gate 下氧化层电场已经超过 3 MV/cm,长期工作可能带来栅氧可靠性问题。不同  $t_{\rm ox}$  对应器件栅氧化层中的电场分布如图 12 所示。

图 12 tox 对器件栅氧电场影响

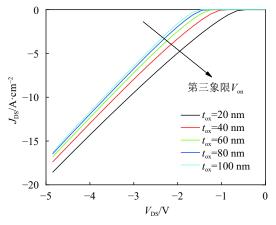

若  $t_{\rm ox}$  过大,器件在第三象限时 LBD 的导通电压大,造成第三象限通损耗增大;若  $t_{\rm ox}$  过小,除了引起栅氧电场过大导致可靠性问题外,根据 LBD 势垒高度式 (1) 可知,LBD 势垒将减小,在器件导通时,N\_well 可能耗尽不充分,在 N\_well 处发生漏电。  $t_{\rm ox}$  对于器件第三象限特性影响如图 13 所示。设定  $I_{\rm SD}$ =0.1 A/cm² 对应第三象限开启,当  $t_{\rm ox}$  从 20 nm 增加到 100 nm,与之对应的第三象限开启电压分别为 0.63、1.06、1.30、1.46、1.52 V。

图 13  $t_{ox}$  对器件第三象限特性

## 3 结束语

本文提出一种集成低势垒二极管的 10 kV LBD-MOSFET 新结构,通过形成一个低势垒二极管 (LBD),降低器件第三象限的开启电压,从而有 效避免体二极管开启所导致的双极退化效应。LBD-MOSFET 击穿电压为  $13.5 \, \mathrm{kV}$ ,在第三象限工作时,开启电压为  $1.3 \, \mathrm{V}$ ,相比传统平面型 SiC MOSFET  $2.5 \, \mathrm{V}$  的开启电压,降低了 48%,可有效降低器件第三象限导通损耗。同时,LBD-MOSFET 的栅漏电容  $C_{\mathrm{gd}}$  仅为  $1.0 \, \mathrm{pF/cm^2}$ ,相比传统平面型 SiC MOSFET 的  $C_{\mathrm{gd}}$  为  $5.2 \, \mathrm{pF/cm^2}$ ,降低了 81%。LBD-MOSFET 的开启损耗为  $0.27 \, \mathrm{mJ}$ ,关断损耗为  $0.90 \, \mathrm{mJ}$ ,相比传统结构分别降低了 66.7% 和 17.4%,因此更适用于高频应用。

#### 参 考 文 献

- [1] 盘和林, 胡霖, 杨慧. 新基建-中国经济新引擎[M]. 北京: 中国人民大学出版社, 2020.

PAN He-lin, HU Lin, YANG Hui. New infrastructure-the new engine of the economy of China[M]. Beijing: China Renmin University Press, 2020.

- [2] BALIGA B J. Fundamentals of power semiconductor devices[M]. [S.l.]: Springer, 2010.

- [3] RYU S H, AGARWAL A K, KRISHNASWAMI S, et al. Development of 10 kV 4H-SiC power DMOSFETs[C]// Materials Science Forum. [S.l.]: Trans Tech Publications, 2004: 1385-1388.

- [4] GRIDER D, DAS M, AGARWAL A, et al. 10 kV/120 A SiC DMOSFET half H-bridge power modules for 1 MVA solid state power substation[C]//2011 IEEE Electric Ship Technologies Symposium. [S.I.]: IEEE, 2011: 131-134.

- [5] KITAI H, HOZUMI Y, SHIOMI H, et al. Low onresistance and fast switching of 13-kV SiC MOSFETs with optimized junction field-effect transistor region[C]//2017

- 29th International Symposium on Power Semiconductor Devices and IC's (ISPSD). Sapporo: IEEE, 2017: 343-346.

- [6] SAITO K, MIYOSHI T, KAWASE D, et al. Simplified model analysis of self-excited oscillation and its suppression in a high-voltage common package for Si-IGBT and SiC-MOS[J]. IEEE Transactions on Electron Devices, 2018, 65(3): 1063-1071.

- [7] TOMINAGA T, HINO S, MITSUI Y, et al. Superior switching characteristics of SiC-MOSFET embedding SBD[C]//2019 31st International Symposium on Power Semiconductor Devices and IC's (ISPSD). [S.I.]: IEEE, 2019: 27-30.

- [8] SUNG W, BALIGA B J. On developing one-chip integration of 1.2 kV SiC MOSFET and JBS diode (JBSFET)[J]. IEEE Transactions on Industrial Electronics, 2017, 64(10): 8206-8212.

- [9] AIBA R, OKAWA M, KANAMORI T, et al. Experimental demonstration on superior switching characteristics of 1.2 kV SiC SWITCH-MOS[C]//2019 31st International Symposium on Power Semiconductor Devices and IC's (ISPSD). [S.l.]: IEEE, 2019: 23-26.

- [10] RYU S H, HUSNA F, HANEY S K, et al. Effect of recombination-induced stacking faults on majority carrier conduction and reverse leakage current on 10 kV SiC DMOSFETs[C]//Materials Science Forum. [S.l.]: Trans Tech Publications, 2009: 1127-1130.

- [11] PETERS D, SIEMIENIEC R, AICHINGER T, et al. Performance and ruggedness of 1200V SiC Trench MOSFET[C]//2017 29th International Symposium on Power Semiconductor Devices and IC's (ISPSD). Sapporo: IEEE, 2017: 239-242.

编辑税红