-

有源相控阵天线在雷达和无线通信等领域应用广泛,可支持快速波束成形和波束扫描,并可消除来自不同方向的干扰,从而达到更好的信噪比和更高的信道容量[1-2]。大规模有源相控阵天线通常由数千个发射接收(T/R)单元组成,其通道一致性、可靠性和成本控制取决于其核心功能器件的性能和集成度[3-5]。传统设计中通常将放大器、数控移相器、数控衰减器、微波开关等不同的单元电路集成在同一颗芯片上组成多功能芯片[6-8](multi-function chip, MFC),实现对信号的幅度、相位控制和收发切换,以降低相控阵的成本,提高集成度和可装配性。

X波段相控阵技术是微波雷达应用的研究热点,文献[9]基于0.25 μm GaAs pHEMT工艺研制了一款X波段多功能芯片,集成了6 bit移相器、5 bit衰减器等,面积5.0×4.0 mm2。在8.5~11.5 GHz,移相器移相RMS误差小于5.5°。文献[10]研制了一款X波段GaAs多功能芯片,集成了6 bit移相器、5 bit衰减器等,面积5.0×4.0 mm2。在8.5~11 GHz,移相器移相RMS误差小于4°,衰减器衰减RMS误差小于0.4 dB。文献[11]基于0.5 μm GaAs pHEMT工艺研制了一款X波段多功能芯片,集成了6 bit移相器、6 bit衰减器等,面积5.5×4.0 mm2。在8.5~10.5 GHz,移相器移相RMS误差小于2.5°,衰减器衰减RMS误差小于0.5 dB。以上3款多功能芯片采用移相器控制相位,获得了较低的无源插损和高精度的移相特性。仅采用移相器的相控阵系统通常是一个窄带系统,其窄带特性表现在天线波束指向随信号频率变化发生波束色散,进而限制了信号的瞬时带宽[12],通过采用真延时(TTD)可以消除波束色散,提高瞬时带宽。

基于宽带相控阵系统的应用需求,本文提出了一种在传统多功能芯片上加入2位延时器的新架构。多功能芯片集成了2位数字延时器、6位数字移相器、6位数字衰减器、4个单刀双掷开关及2个驱动放大器。采用移相器实现了高精度的移相特性,同时加入的两位延时器有效降低了波束的空间色散,提高了相控阵系统的扫描角度和瞬时带宽。在幅相特性方面,采用高低通移相网络和开关型衰减拓扑,实现了良好的幅相性能。

-

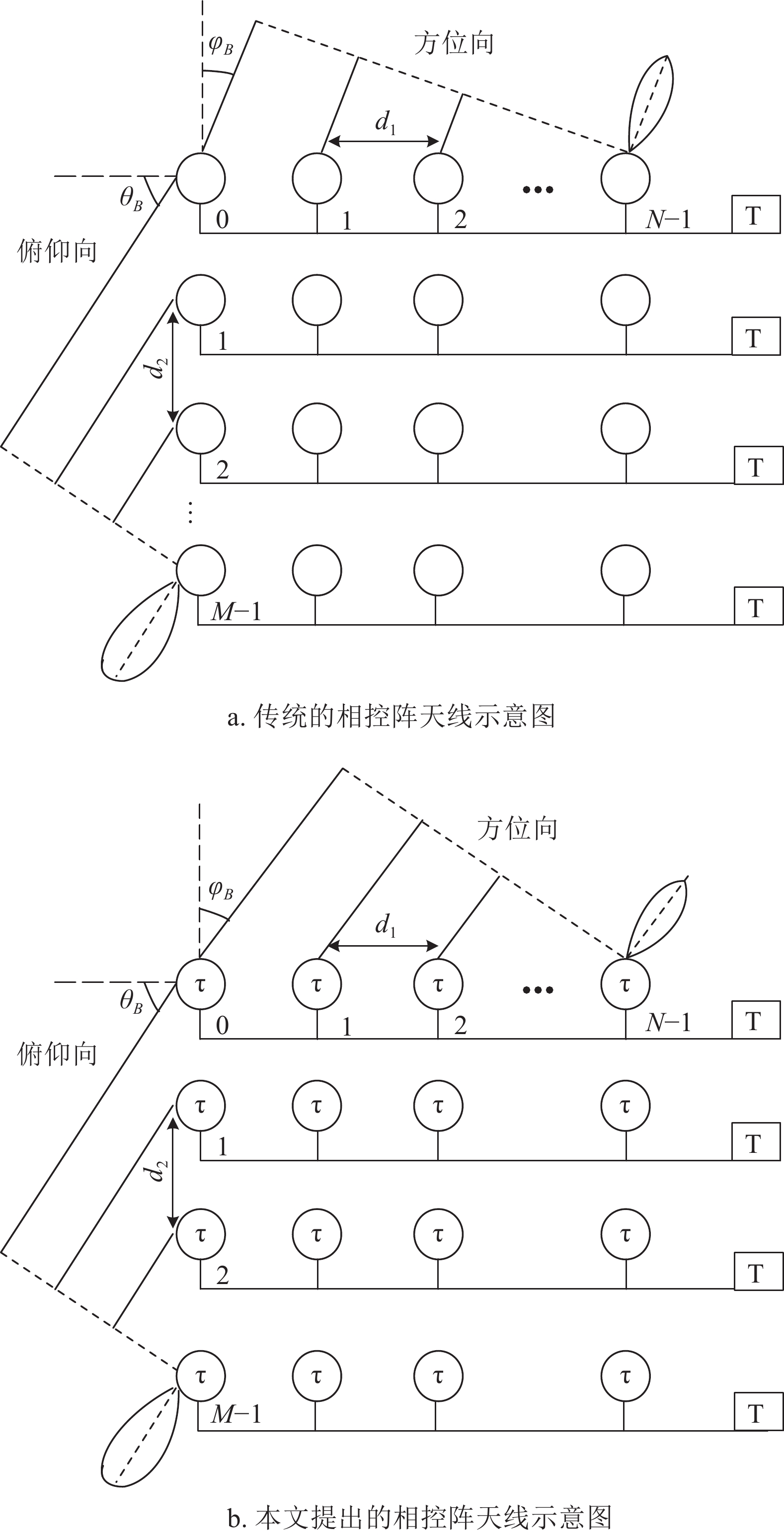

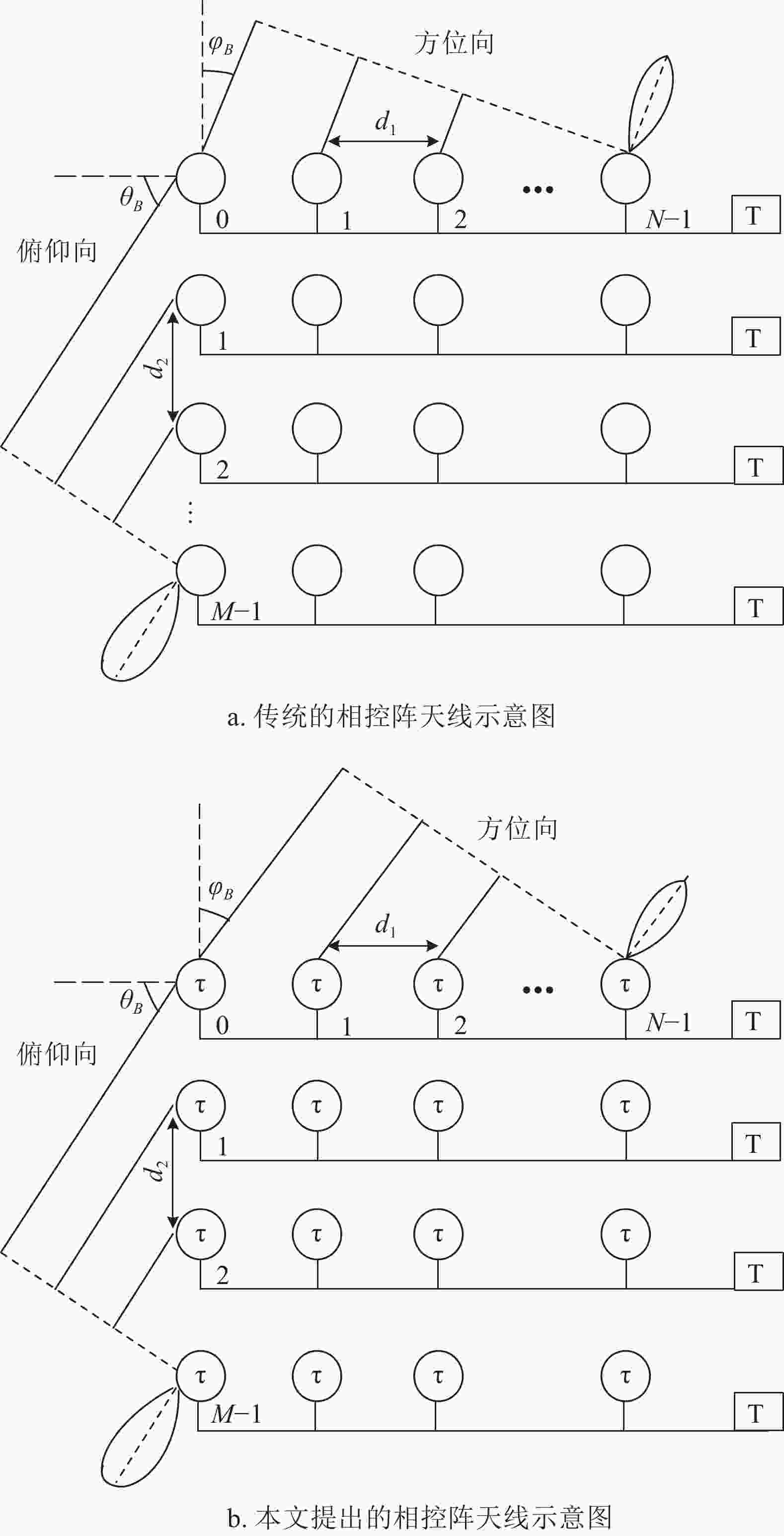

在工程应用中,一般将整个阵列均匀划分为几个子阵,对各个子阵进行时间延时,在子阵内部阵元上采用移相器控制相位。图1a为传统的二维平面相控阵天线示意图,其中

${\varphi _B}$ 为天线波束在方位向的扫描角,${\theta _B}$ 为天线波束在俯仰向的扫描角,阵元间距分别为d1与d2。将该平面阵划分为M个行线阵,每个行线阵包含N个单元。通常在子阵级上接入具有大延时量的数控延时器(T),补偿子阵间的孔径渡越时间,天线在俯仰向上可实现宽角扫描。而子阵内部的阵元上仅采用移相器实现阵内相位差,天线在方位向的扫描角度受到严重限制。对于在方位向扫描的阵内天线,第N−1个单元辐射的信号将最先到达目标,第0号单元最晚到达目标。0号与第N−1个单元的阵内相位差可表示为:

$$\Delta \phi = \left( {\frac{{2{\text π} }}{c}} \right)fL\sin {\varphi _B}$$ (1) 式中,

$\Delta \phi $ 为阵内相位差;$L$ 为子阵孔径长度,$L = (N - 1){d_1}$ 。对于窄带系统,

$\Delta \phi $ 通常为中心频点${f_0}$ 对应的阵内相位差,当扫描角度${\varphi _B}$ 增大,移相器需要补偿的$\Delta \phi $ 随之增大;对于宽带系统,当信号频率变化时,低频时波束指向${\varphi _B}$ 比中心频点${f_0}$ 时大,高频时波束指向${\varphi _B}$ 比中心频点${f_0}$ 时小,波束指向随信号频率变化而发生波束色散。为了实现在相控阵应用中可同时支持宽带、宽角工作,本文提出了在传统多功能芯片加入2位数字延时器(τ)的新架构,图1b为本文提出的相控阵天线示意图。通过加入延时器补偿阵内相位差,增大扫描角度;延时器的相移量随频率线性变化,波束指向与频率无关,有效降低色散。同时加入的2位延时器提高了多功能芯片的集成度,并避免了全部采用延时器取代移相器时,数量众多、损耗较大的延时器给工程实现带来的巨大代价。

以

$N = 4$ ,${d_{\rm{1}}} = {\lambda _0}/2$ 的子线阵为例进行分析,为了实现带宽$(0.8{f_0} \sim 1.2{f_0})$ 、最大偏转角度(45°~60°)的波束扫描,通过理论计算,本设计选择加入2位$(0.25{\lambda _0},\,0.5{\lambda _0})$ 数字延时器。表1总结了加入2位延时器对扫描角度、带宽的影响。表 1 延时器对扫描角度和带宽的影响

单一移相器子阵 移相器+2 bit TTD子阵(本文方案) ${\varphi _B}$/(°) 移相状态/rad ${\varphi _B}$/(°) 延时(λ)+移相状态/rad 0.8f0 f0 1.2f0 N=1 N=2 N=3 N=4 0.8f0 f0 1.2f0 N=1 N=2 N=3 N=4 12.5 10 8.3 0.519π 0.346π 0.173π 0 12.5 10 8.3 0λ+0.519π 0λ+0.346π 0λ+0.173π 0 25.3 20 16.6 1.026π 0.684π 0.342π 0 25.3 20 16.6 0λ+1.026π 0λ+0.684π 0λ+0.342π 0 38.7 30 24.6 1.5π π 0.5π 0 30 30 30 0.75λ+0π 0.5λ+0π 0.25λ+0π 0 53.5 40 32.4 1.926π 1.284π 0.642π 0 42.7 40 38.3 0.75λ+0.426π 0.5λ+0.284π 0.25λ+0.142π 0 − − − − − − − 49.4 45 42.7 0.75λ+0.621π 0.5λ+0.414π 0.25λ+0.207π 0 − − − − − − − 73.2 60 53.6 0.75λ+1.098π 0.5λ+0.732π 0.25λ+0.366π 0 从表1可得出,单一移相器子阵只能实现最大40°的扫描角度,且在

${\varphi _B}$ =40°时,工作频带内波束最大漂移达到33.8%。加入2位延时器后,可实现最大60°的扫描角度,并显著降低了波束随频率变化的角度漂移,${\varphi _B}$ =40°时,带内波束最大漂移6.7%,${\varphi _B}$ =60°时,带内波束最大漂移22%。 -

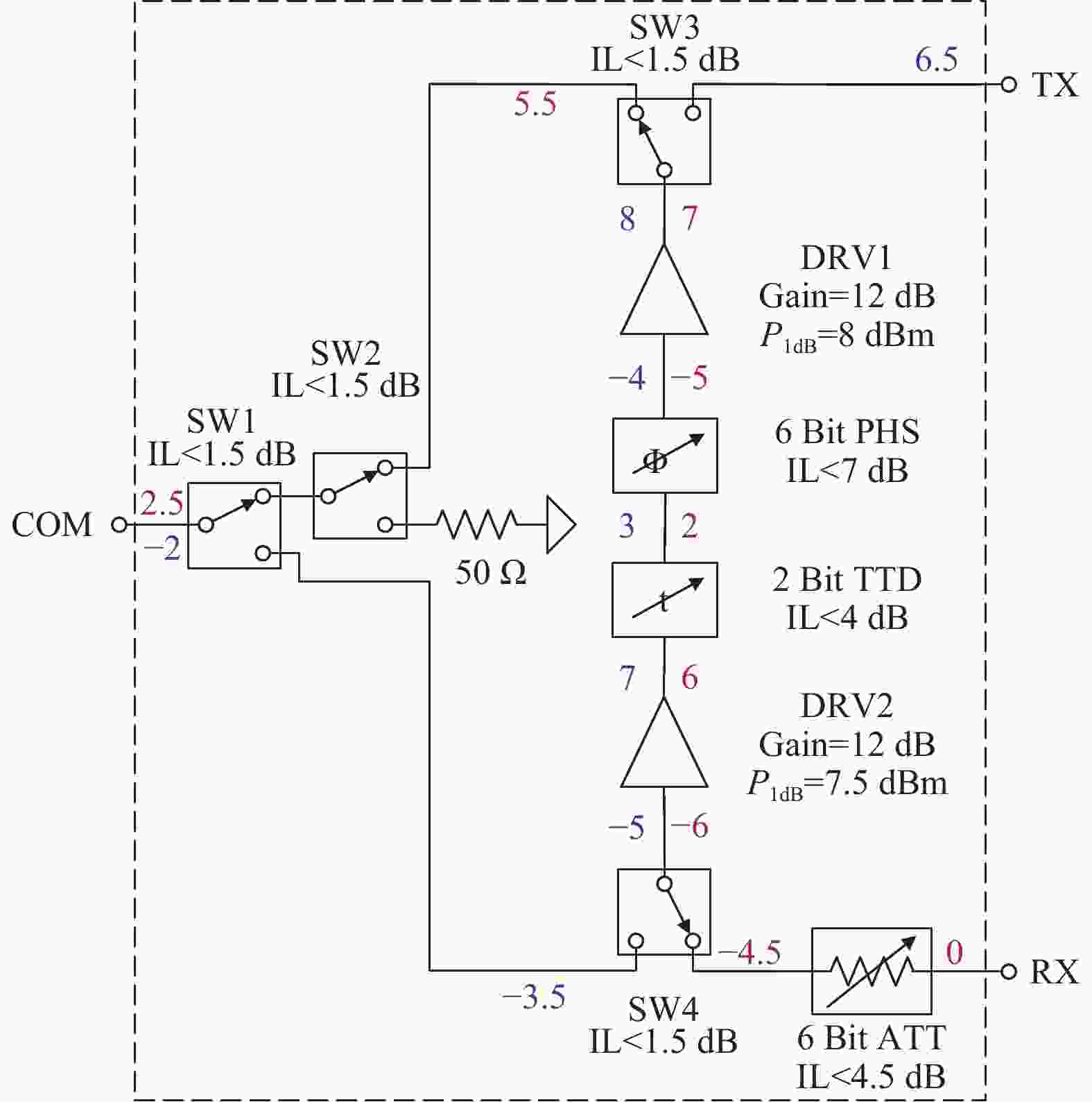

基于本文提出的加入2位延时器的新架构进行多功能芯片的设计,多功能芯片总体框图如图2所示。链路结构采用了公共支路拓扑[13-14],发射(TX)、接收(RX)支路共用2位延时器,6位移相器、2个驱动放大器以减小芯片的尺寸。移相器用来调节收发支路的相位特性,延时器用来补偿不同频率引起的相位差,驱动放大器用来补偿无源电路的插入损耗,并提供一定的输出功率。在接收支路增加6位数字衰减器实现接收幅度调制功能。4个单刀双掷开关(SPDT)组成的微波开关阵列用来实现收发切换,并在公共端(COM)串联的开关SW2一端接入50 Ω负载,保证负载态时COM端口的良好匹配。

根据芯片总体指标对链路进行增益和功率预算,图2标明了各个模块电路的增益或损耗及信号经过链路的功率变化,其中蓝色标记为发射链路功率预算,红色标记为接收链路功率预算。

-

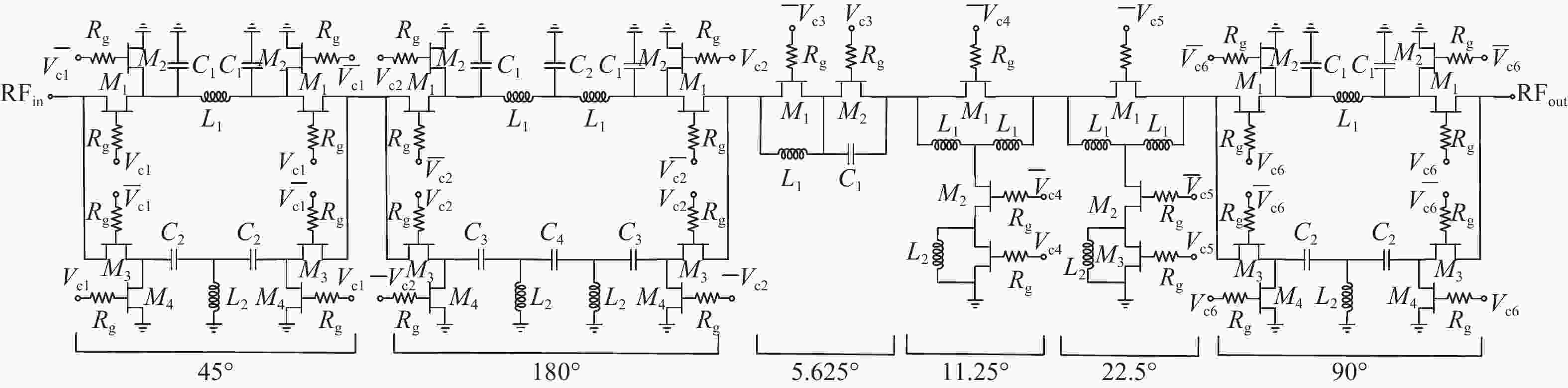

移相器作为幅相多功能芯片的关键模块,其电路拓扑如图3所示。6位数字移相器由6个基本位组成,分别为5.625°、11.25°、22.5°、45°、90°和180°,通过控制6个移相单元的组合,可实现步进值为5.625°的64个移相状态,移相范围0°~360°。

5.625°移相位采用了简化的串联型FET结构,参考态时,M1导通,M2截止,信号通过电容C1产生超前相位。移相态时,M2导通,M1截止,信号通过电感L1产生滞后相位,两种状态的相位差即为所需要的相移量。这种结构引入较小的插入损耗,且匹配性好,体积小。

11.25°和22.5°采用桥T型结构,参考态时,M1,M2导通,M3截止,调节电感L2的感值使其与M3的截止电容产生并联谐振。由于串联管芯M1的导通电阻Ron很小,此时信号传输的相位差和插入损耗都很小。在移相状态,M1,M2截止,M3导通,电路等效为T型低通移相网络。该拓扑只有一个串联开关,具有较小的插入损耗,并将开关的截止态寄生电容作为移相网络的一部分,消除寄生参数对电路性能的影响[15]。

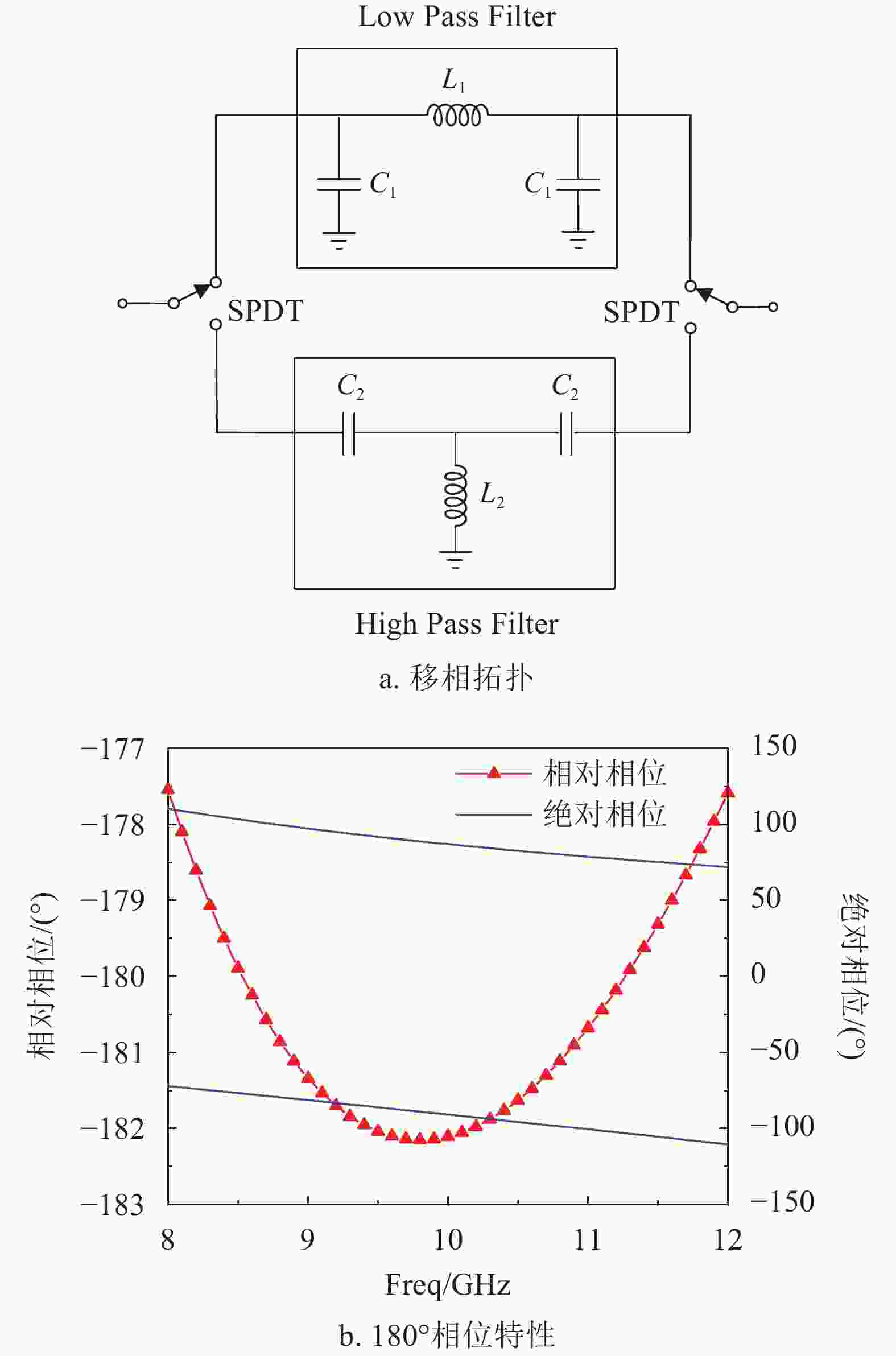

由于管芯寄生效应作用,桥T型移相器的工作带宽较窄,不再适合相位变化较大的移相位。45°、90°、180°移相位采用了高低通结构进行设计,电路拓扑如图4a,通过SPDT开关使信号在高通滤波器和低通滤波器之间切换,利用两个网络函数的相频特性的差别实现移相。高通滤波器电路的相位超前随频率的升高而减小,低通滤波器电路的相位滞后随频率的升高而增大,这两种滤波器在移相时可以互相补偿相位,从而实现较宽频率范围内平坦的移相特性。高低通网络的各元件值可通过式(2)、式(3)计算所得:

$${L_1} = \frac{{{Z_0}\sin \left(\dfrac{{{\varphi _0}}}{2}\right)}}{{{\omega _0}}},\quad{C_1} = \dfrac{{1 - \cos \left(\dfrac{{{\varphi _0}}}{2}\right)}}{{{Z_0}{\omega _0}\sin \left(\dfrac{{{\varphi _0}}}{2}\right)}}$$ (2) $${L_2} = \frac{{{Z_0}}}{{{\omega _0}\sin \left(\dfrac{{{\varphi _0}}}{2}\right)}},\quad{C_2} = \frac{{\sin \left(\dfrac{{{\varphi _0}}}{2}\right)}}{{{Z_0}{\omega _0}\left( {1 - \cos \left(\dfrac{{{\varphi _0}}}{2}\right)} \right)}}$$ (3) 式中,

${Z_0}$ 为特征阻抗(50 Ω);${\omega _0} = 2{\text π}{f_0}$ ;${\varphi _0}$ 为所需要的相移量。对于180°移相位,通过增加滤波器阶数,采用了5阶高低通网络,增大了移相值,拓宽了移相器的响应带宽[16]。图4b为180°相位特性,在整个频带内,移相范围180±2.5°。表2列出了基于开关管芯寄生影响的6位数字移相器设计参数。

表 2 6位数字移相器设计参数

Unit Cell/(°) M1/μm M2/μm M3/μm M4/μm L1/nH L2/nH C1/pF C2/pF C3/pF C4/pF 5.625 6×55 6×45 − − 0.19 − 2.7 − − − 11.25 6×70 6×60 6×20 − 0.034 4.18 − − − − 22.5 8×80 8×55 6×75 − 0.138 1.65 − − − − 45 8×45 2×20 8×45 2×20 0.5 1.39 0.033 2.98 − − 90 6×55 2×25 6×55 2×30 0.66 1.38 0.12 0.75 − − 180 6×70 2×20 6×70 2×20 0.75 1.25 0.07 0.24 0.82 0.33 -

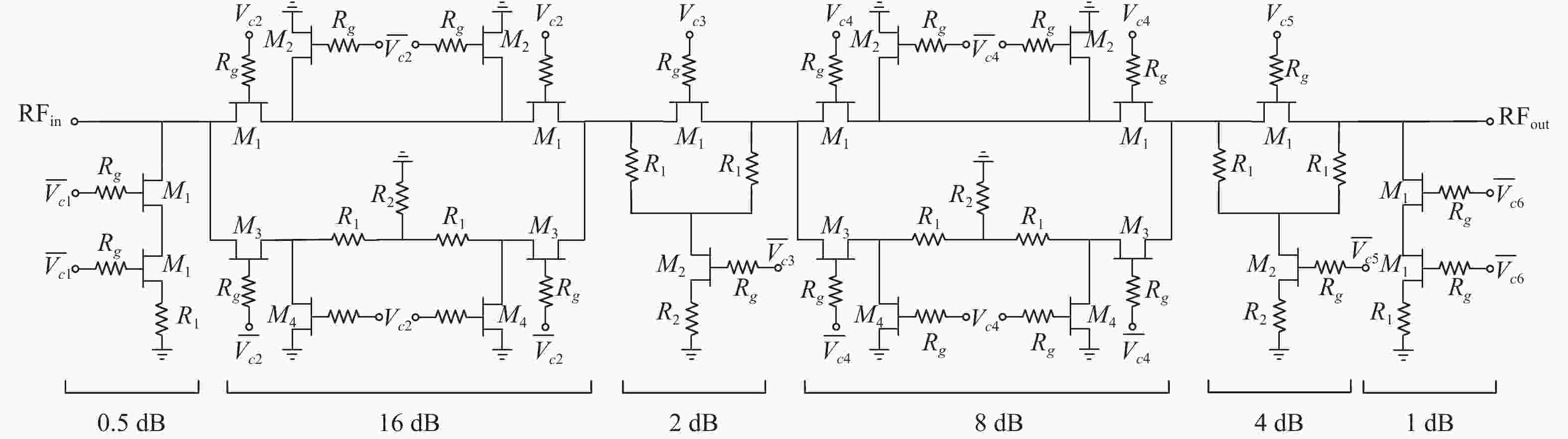

数字衰减器电路拓扑如图5所示。6位数字衰减器由0.5、1、2、4、8、16 dB衰减单元级联而成,在0.5~31.5 dB的衰减范围内可以实现以0.5 dB为步进的64种衰减状态。

0.5 dB和1 dB衰减位采用的是简化的T型衰减器结构,仅采用一个并联电阻进行衰减,开关选用两个小尺寸的管子串联而成。参考态时开关管M1截止,信号不衰减,由于M1截止电容足够小,对于射频信号相当于开路,提高了隔离度;当开关管M1导通时,衰减器工作在衰减态,并联支路到地电阻对信号进行衰减。该结构适用于小衰减位,具有结构简单、插入损耗小等优点。其衰减量及衰减态回波损耗与电阻R1的阻值关系如表3所示。

根据表3可知,当衰减量较小(0.5、1 dB)时,衰减器的回波损耗也比较小;当衰减量大于2 dB时,回波损耗将会严重恶化,该简化T型衰减结构不再适用。

对于2 dB和4 dB衰减位,采用了开关T型衰减结构。当处于参考态时,M1导通,M2截止,电路等效为小电阻,信号的幅度与相位变化都不大;当处于衰减态时,M1截止,M2导通,电路等效为T型衰减网络,衰减网络的各电阻值可通过式(4)、式(5)计算所得。该结构本身具有很好的端口匹配特性,可以很好地与其他衰减位级联[17]。

表 3 衰减量及回波损耗与电阻R1的关系

IL/dB R1/Ω RL/dB 0.5 425 −25 1 205 −19.3 2 96 −13.7 4 43.6 −8.6 $$R_2 = 2{Z_0}\sqrt {{{10}^{\frac{L}{{10}}}}} \Bigg/({10^{\frac{L}{{10}}}} - 1)$$ (4) $$R_1 = {Z_0}({10^{\frac{L}{{10}}}} + 1)/({10^{\frac{L}{{10}}}} - 1) - R_2$$ (5) 式中,Z0是特征阻抗(50 Ω);L是需要的衰减量。

对于8 dB,16 dB衰减位,较大的衰减会在衰减状态与参考状态之间产生较大的附加相移,而仅通过T型衰减结构很难消除[18]。因此采用了开关型衰减拓扑结构,通过两对SPDT将信号在参考支路和衰减支路之间切换实现衰减。在衰减支路采用T型衰减网络提高衰减平坦度,同时在参考支路增加一段微带线来补偿衰减支路的相位误差,该结构虽然增加了两对SPDT的插入损耗,但在整个带宽内有很好的衰减特性,并减小了对相位的调制,有效降低了衰减器的附加相移。表4为基于开关管芯寄生影响的6位数字衰减器设计参数。

表 4 6位数字衰减器设计参数

Unit Cell/dB M1/μm M2/μm M3/μm M4/μm R1/Ω R2/Ω 0.5 2×25 2×25 − − 431 − 1 2×25 2×25 − − 105 − 2 4×80 4×25 − − 7.2 170 4 6×50 2×25 − − 11.6 65 8 6×50 4×25 4×45 4×25 8.3 32.8 16 6×45 4×50 4×50 4×50 33.6 15.6 -

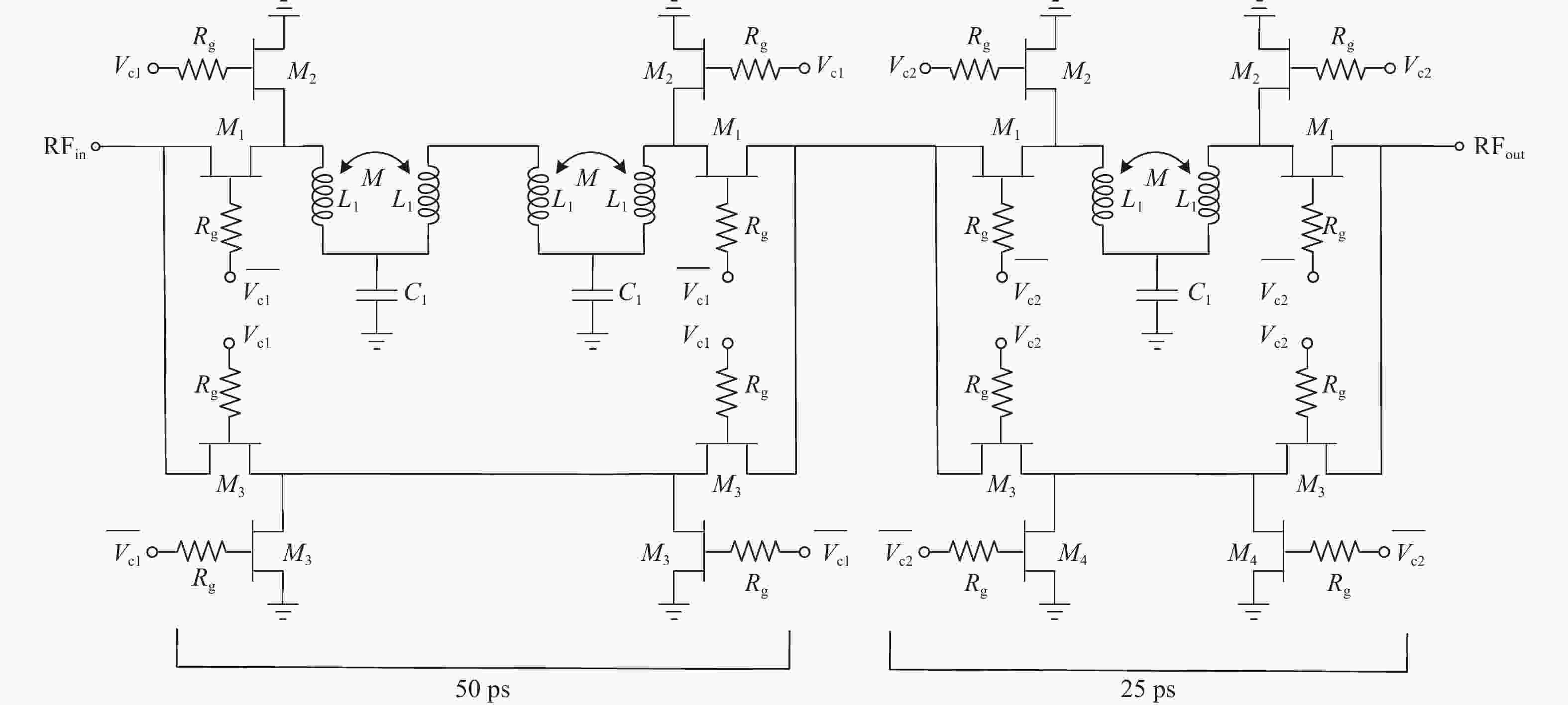

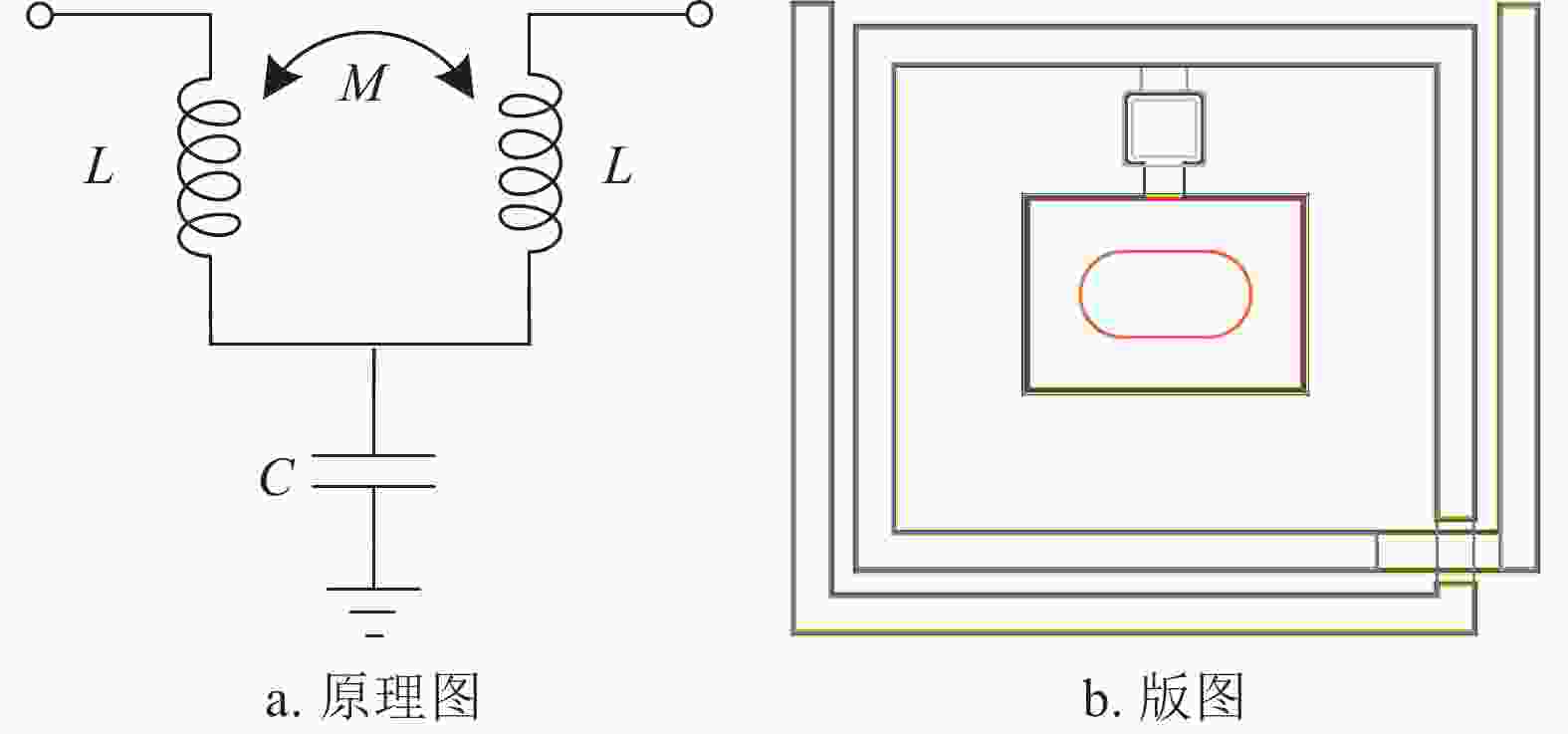

延时器采用开关型延时结构[19],如图6所示,由2组SPDT与延时网络组成,开关在参考态和延时态进行路径切换,实现恒定的时延变化。

以25 ps(0.25 λ)作为一个延时单元,50 ps延时采用2个25 ps延时单元堆叠而成,通过控制两个延时位的组合,可实现25、50、75 ps的3组延时状态。延时单元采用如图7a所示的L-C-L的T型延时网络。为了减小延时单元的面积,延时单元中的耦合电感采用耦合微带线实现,延时单元版图如图7b所示。

表5为2位数字延时器电路设计参数。由于耦合电感采用了微带线实现,电感参数不再列出。

表 5 2位数字延时器设计参数

Unit Cell/ps M1/μm M2/μm M3/μm M4/μm L1/nH C1/pF 25 4×80 2×25 4×80 2×25 − 0.284 50 4×60 2×25 4×50 2×30 − 0.206 -

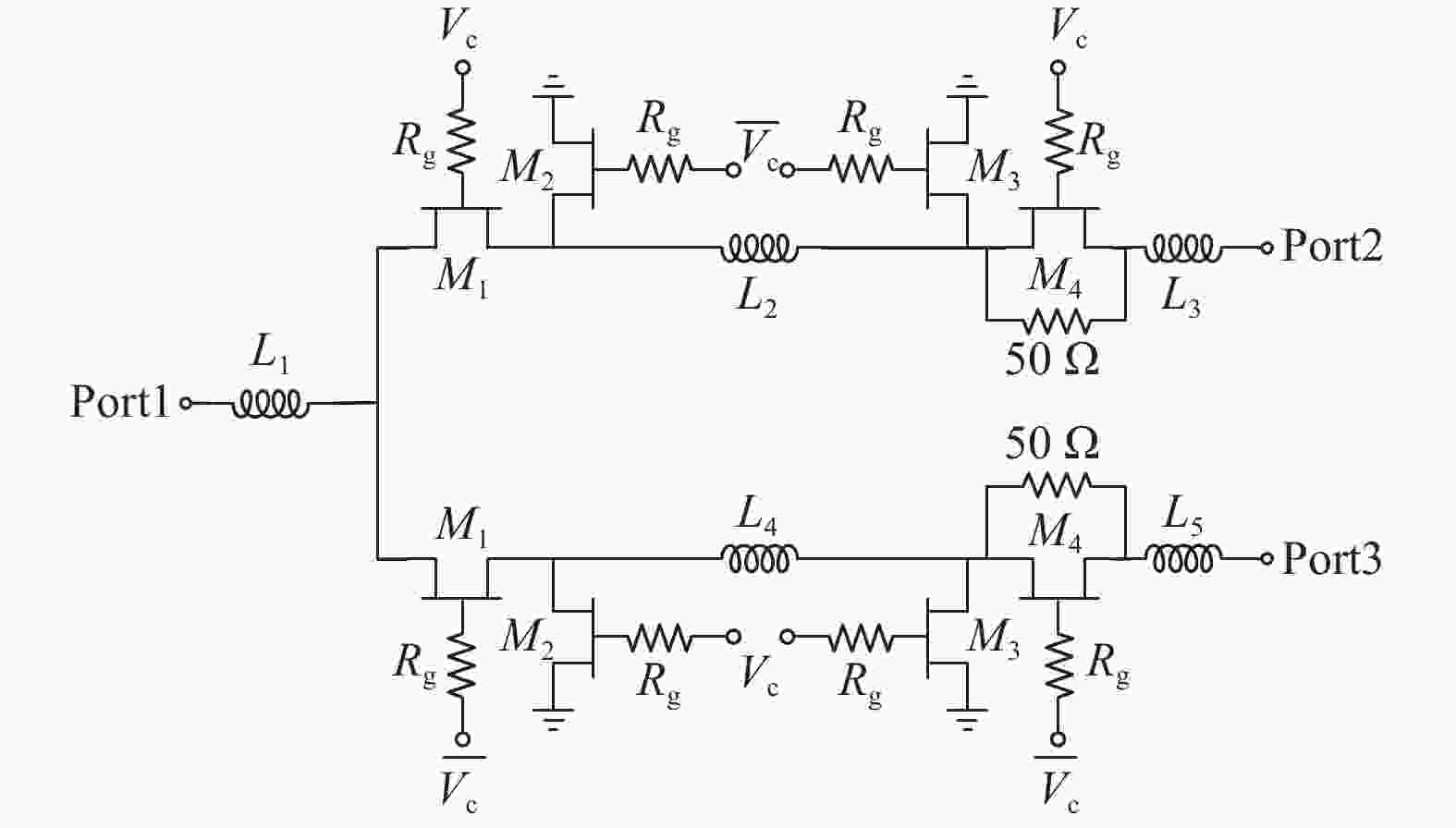

单刀双掷开关拓扑如图8所示,采用两级串并联结构。在导通支路上,串联管芯决定了支路的插入损耗,并联管芯提高支路的隔离度。同时,在串并联结构的基础上改进为吸收式开关,即在两个支路端的开关管上并联50 Ω左右的电阻,使开关在开闭状态下,各端口均有良好匹配。

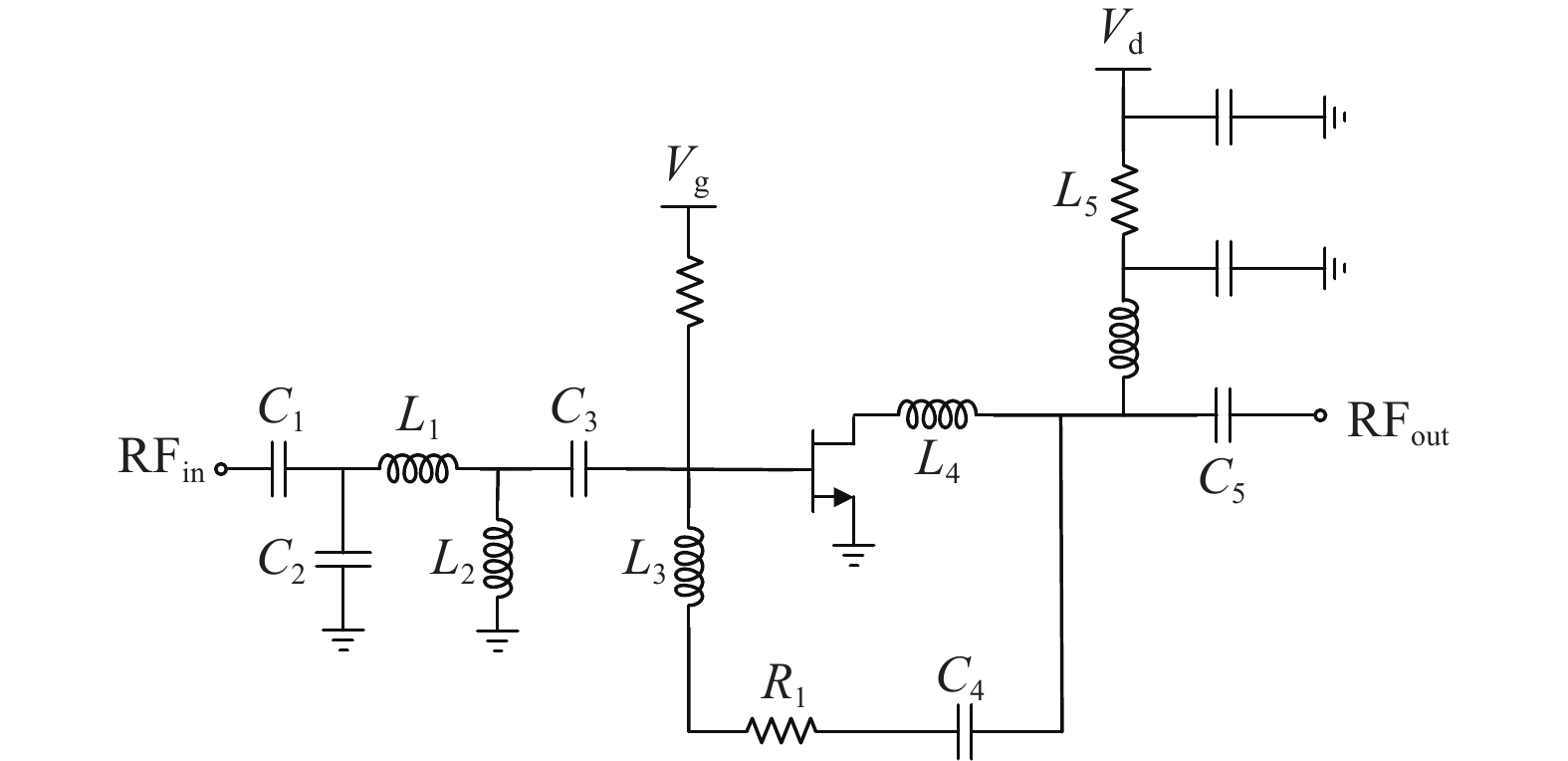

驱动放大器的电路拓扑如图9所示,采用单级放大,电路采用管芯并联RLC负反馈网络实现。

电阻R1作为负反馈结构的关键元件,决定了放大器的基础增益和带宽,它能够提高晶体管的稳定性,并使得输入输出阻抗更接近50 Ω。电感L3为电路带来一定程度的频响特性,当电路工作在低频时,由R1控制电路的增益水平;当电路工作在高频时,L3会降低负反馈效应,使放大器表现出一个平坦的增益特性曲线。在漏极输出端引入电感L4,用于补偿晶体管的输出寄生电容Cds,同时为电路提供一定的增益正斜率特性。

-

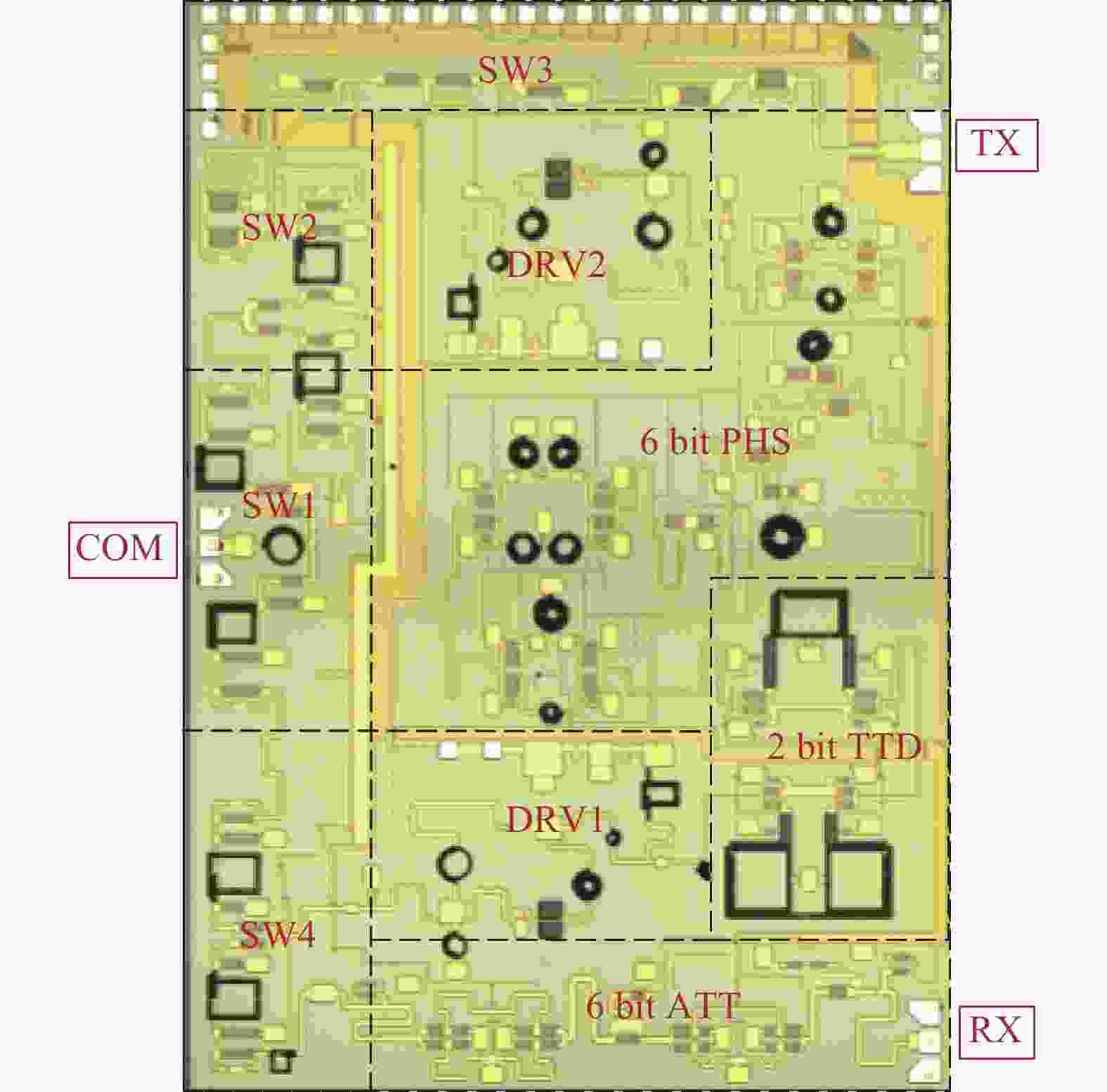

在版图的整体布局中,根据各基本位的端口阻抗特性,确定各移相位及衰减位的级联顺序,并调整公共支路移相器的接口以减小芯片面积。多功能芯片的照片如图10所示,芯片尺寸为5.0×3.5 mm2。

测试系统采用Cascade微波探针台、矢量网络分析仪(Agilent PNA N5224A)、开关矩阵(Agilent 34980A)以及电源,测试系统如图11所示。矢量网络分析仪、开关矩阵和计算机通过GPIB进行连接。开关矩阵负责对移相器、衰减器、延时器、微波开关阵列发送控制信号及切换;电源负责对芯片放大器供电;矢量网络分析仪负责对多功能芯片S参数的测量;计算机用来实现自动测试,以及测试结果的处理和显示。

采用微波探测台对多功能芯片进行在片测试,控制微波开关阵列实现芯片收发通道的切换,并分别测试收发通道中的移相器、衰减器、延时器的幅相特性,以及通道增益和输出功率。测试条件为:芯片的放大器工作电压为+5 V,静态工作电流为33 mA,开关栅极偏置电压0/−5 V,输入功率Pin=−15 dBm。

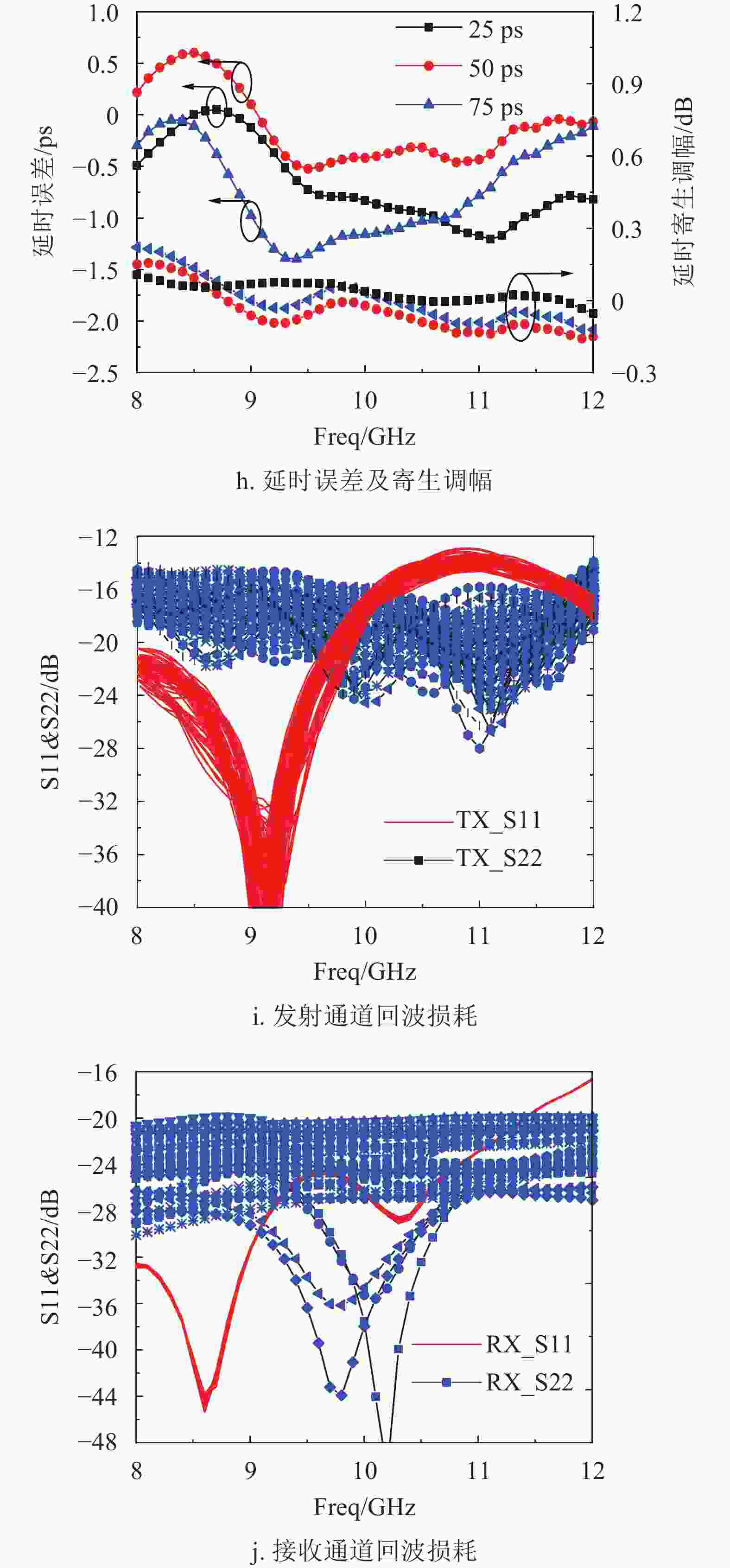

射频性能测试结果如图12所示。图12a和图12b所示,芯片的发射增益大于7 dB,接收增益大于3 dB;发射通道P1dB大于7.5 dBm,接收通道P1dB大于5 dBm。图12c和图12d分别为64态移相特性和64态衰减特性,在整个频带内都具有较好的移相、衰减平坦度。图12e为收发通道中移相器的相位、幅度误差,收发状态下,移相器64态移相RMS误差均小于3.5°,移相寄生调幅RMS误差均小于0.3 dB。图12f为接收状态下的衰减器测试性能,64态衰减RMS误差小于0.4 dB,衰减附加相移RMS误差小于2.5°。图12g和图12h,延时器延时特性相对平坦,3态延时的延时误差在±1.5 ps,3态延时寄生调幅误差在±0.3 dB。图12i和图12j所示,发射通道全态端口回波损耗小于−12 dB;接收通道全态端口回波损耗小于−16 dB。

表6总结了本文与公开文献发表的其他同频段内多功能芯片的性能对比。本文设计的多功能芯片在移相精度、移相寄生调幅、衰减精度、衰减附加相移等幅相特性上具有明显优势。此外,本文的设计与采用CMOS工艺设计的文献[4-5]相比,在同等增益水平时功耗相当。相比于文献[4-6, 9-11],本设计工作频带为8~12 GHz,具有更大的工作带宽。与文献[20-21]相比,在均具有覆盖整个X波段的带宽下,本设计在工艺造价上具有更低的成本。 同时在多功能芯片上集成了2位延时器,具有更高的集成度,可显著改善相控阵应用中的波束色散。

表 6 多功能芯片性能对比

文献 频率

/GHzATT/PHS/

TTD位数

/bitRX/TX

增益

/dBRX/TX

输出

P1dB/dBmRMS衰减

误差/dB

(ATT)RMS寄生

调相/(°)

(ATT)RMS移相

误差/(°)

(PHS)RMS寄生

调幅/dB

(PHS/TTD)时延误差

/ps (TTD)移相范围

(deg)+时延

范围 (λ)功耗

/mW通道数/

尺寸/mm2工艺 [4] 8.5~10.5 5/6/− 3.5/3.5 6.5/6.5 0.33 7.4 4.3 0.8/− − 360/− 154 1T1R/1.2 0.13-µm CMOS [5] 8~10.5 6/6/− 3.7/3.7 5.1/5.1 0.5 8 4 0.9/− − 360/− 170 1T1R/9.6 65-nm CMOS [6] 8.5~10 6/6/− 12/11 11/11.5 0.5 9 2 0.5/− − 360/− 670 1T1R/12.8 0.18-µm CMOS [9] 8.5~11.5 5/6/− 27/− 13/19 − 3 5.5 −/− − 360/− 1200 1T1R/20 0.25-µm GaAs [10] 8.5~11 5/6/− 21/19 17.5/23.5 0.4 5 4 0.5/− − 360/− 2100 1T1R/20 GaAs pHEMT [11] 8.5~10.5 6/6/− 14/22 −/19 0.5 3.5 2.5 0.5/− − 360/− 1000 1T1R/22 0.5-µm GaAs [20] 8~12 6/6/− 5/5 11/11 0.6 − 5 −/− − 360/− 360 1T1R/17.9 0.18-µm GaAs [21] 8~12 6/6/− 11.5/22 16.5/− 0.6 4 4 0.4/− − 360/− 1750 1T1R/22.6 0.25-µm GaAs 本文 8~12 6/6/2 3/7 5/7.5 0.4 2.5 3.5 0.3/0.3 1.5 360/0.75 165 1T1R/17.5 0.5-µm GaAs -

本文基于0.5 μm GaAs pHEMT工艺研制了一款X波段宽带幅相多功能芯片。芯片集成了延时器、移相器、衰减器、单刀双掷开关、驱动放大器等5种单功能电路,提高了T/R组件的集成度,降低了T/R组件的成本,满足相控阵雷达对前端T/R组件高集成度和低成本的要求,同时集成的两位数字延时器可有效提高相控阵系统的瞬时带宽。在幅相特性方面,采用高低通移相网络和开关型衰减拓扑,实现了高精度的移相、衰减特性,并有效降低了寄生调幅和附加相移。测试结果表明,该芯片实现了宽带性能和良好的幅相性能,可广泛应用于微波相控阵雷达T/R组件等领域。

Design of X-Band Wideband Multi-Function Chip with Phase and Amplitude Control

-

摘要: 为了降低相控阵天线T/R组件的尺寸和成本,提高集成度,该文基于0.5 μm GaAs pHEMT工艺,设计了一款X波段宽带幅相多功能芯片。芯片在架构设计方面除了集成传统的6位数字移相器、6位数字衰减器、单刀双掷开关和驱动放大器以外,新引入了2位数字延时器,实现了收发通道的幅相与时延的独立控制和单芯片集成,改善了宽带相控阵应用中的波束色散。在幅相特性方面,采用高低通移相网络和开关型衰减拓扑,实现平坦的移相、衰减特性,并有效降低了寄生调幅和附加相移。实测结果表明:8~12 GHz工作频带内,64态移相均方根(RMS)误差小于3.5°,寄生调幅RMS小于0.3 dB;64态衰减RMS误差小于0.4 dB,附加相移RMS小于2.5°;延时器延时误差小于1.5 ps。芯片尺寸为5.0 mm×3.5 mm。Abstract: An X-band multi-function chip(MFC) with phase and amplitude control is designed and fabricated in 0.5 μm GaAs pHEMT technology, which can significantly improve the integration of transmit/receive (T/R) radar module. The MFC consists of a 2-bit true time delay(TTD), a 6-bit digital phase shifter, a 6-bit digital attenuator and two drive amplifiers. In terms of architecture design, a 2-bit TTD is introduced at the first time to achieve wideband operation while lowering beam squinting, and realizing the independent control of amplitude, phase and time delay on a single chip. The high-low pass phase shifting network and switch-path-type attenuation topology are employed in order to achieve high-precision phase and amplitude performance. The measurement results show that the RMS phase and amplitude error of 64-state phase shifter is 3.5° and 0.3 dB max, the RMS amplitude and phase error of 64-state attenuator is less than 0.4 dB and 2.5°, and the delay error of 3-state TTD is less than 1.5 ps over the 8 GHz to 12 GHz frequency band. The chip size is 5.0 mm×3.5 mm including the test pads.

-

Key words:

- attenuator /

- multi-function chip /

- phase shifter /

- T/R Module /

- true time delay /

- X band

-

表 1 延时器对扫描角度和带宽的影响

单一移相器子阵 移相器+2 bit TTD子阵(本文方案) ${\varphi _B}$ /(°)移相状态/rad ${\varphi _B}$ /(°)延时(λ)+移相状态/rad 0.8f0 f0 1.2f0 N=1 N=2 N=3 N=4 0.8f0 f0 1.2f0 N=1 N=2 N=3 N=4 12.5 10 8.3 0.519π 0.346π 0.173π 0 12.5 10 8.3 0λ+0.519π 0λ+0.346π 0λ+0.173π 0 25.3 20 16.6 1.026π 0.684π 0.342π 0 25.3 20 16.6 0λ+1.026π 0λ+0.684π 0λ+0.342π 0 38.7 30 24.6 1.5π π 0.5π 0 30 30 30 0.75λ+0π 0.5λ+0π 0.25λ+0π 0 53.5 40 32.4 1.926π 1.284π 0.642π 0 42.7 40 38.3 0.75λ+0.426π 0.5λ+0.284π 0.25λ+0.142π 0 − − − − − − − 49.4 45 42.7 0.75λ+0.621π 0.5λ+0.414π 0.25λ+0.207π 0 − − − − − − − 73.2 60 53.6 0.75λ+1.098π 0.5λ+0.732π 0.25λ+0.366π 0 表 2 6位数字移相器设计参数

Unit Cell/(°) M1/μm M2/μm M3/μm M4/μm L1/nH L2/nH C1/pF C2/pF C3/pF C4/pF 5.625 6×55 6×45 − − 0.19 − 2.7 − − − 11.25 6×70 6×60 6×20 − 0.034 4.18 − − − − 22.5 8×80 8×55 6×75 − 0.138 1.65 − − − − 45 8×45 2×20 8×45 2×20 0.5 1.39 0.033 2.98 − − 90 6×55 2×25 6×55 2×30 0.66 1.38 0.12 0.75 − − 180 6×70 2×20 6×70 2×20 0.75 1.25 0.07 0.24 0.82 0.33 表 3 衰减量及回波损耗与电阻R1的关系

IL/dB R1/Ω RL/dB 0.5 425 −25 1 205 −19.3 2 96 −13.7 4 43.6 −8.6 表 4 6位数字衰减器设计参数

Unit Cell/dB M1/μm M2/μm M3/μm M4/μm R1/Ω R2/Ω 0.5 2×25 2×25 − − 431 − 1 2×25 2×25 − − 105 − 2 4×80 4×25 − − 7.2 170 4 6×50 2×25 − − 11.6 65 8 6×50 4×25 4×45 4×25 8.3 32.8 16 6×45 4×50 4×50 4×50 33.6 15.6 表 5 2位数字延时器设计参数

Unit Cell/ps M1/μm M2/μm M3/μm M4/μm L1/nH C1/pF 25 4×80 2×25 4×80 2×25 − 0.284 50 4×60 2×25 4×50 2×30 − 0.206 表 6 多功能芯片性能对比

文献 频率

/GHzATT/PHS/

TTD位数

/bitRX/TX

增益

/dBRX/TX

输出

P1dB/dBmRMS衰减

误差/dB

(ATT)RMS寄生

调相/(°)

(ATT)RMS移相

误差/(°)

(PHS)RMS寄生

调幅/dB

(PHS/TTD)时延误差

/ps (TTD)移相范围

(deg)+时延

范围 (λ)功耗

/mW通道数/

尺寸/mm2工艺 [4] 8.5~10.5 5/6/− 3.5/3.5 6.5/6.5 0.33 7.4 4.3 0.8/− − 360/− 154 1T1R/1.2 0.13-µm CMOS [5] 8~10.5 6/6/− 3.7/3.7 5.1/5.1 0.5 8 4 0.9/− − 360/− 170 1T1R/9.6 65-nm CMOS [6] 8.5~10 6/6/− 12/11 11/11.5 0.5 9 2 0.5/− − 360/− 670 1T1R/12.8 0.18-µm CMOS [9] 8.5~11.5 5/6/− 27/− 13/19 − 3 5.5 −/− − 360/− 1200 1T1R/20 0.25-µm GaAs [10] 8.5~11 5/6/− 21/19 17.5/23.5 0.4 5 4 0.5/− − 360/− 2100 1T1R/20 GaAs pHEMT [11] 8.5~10.5 6/6/− 14/22 −/19 0.5 3.5 2.5 0.5/− − 360/− 1000 1T1R/22 0.5-µm GaAs [20] 8~12 6/6/− 5/5 11/11 0.6 − 5 −/− − 360/− 360 1T1R/17.9 0.18-µm GaAs [21] 8~12 6/6/− 11.5/22 16.5/− 0.6 4 4 0.4/− − 360/− 1750 1T1R/22.6 0.25-µm GaAs 本文 8~12 6/6/2 3/7 5/7.5 0.4 2.5 3.5 0.3/0.3 1.5 360/0.75 165 1T1R/17.5 0.5-µm GaAs -

[1] COHEN E, JAKOBSON C, RAVID S, et al. A bidirectional TX/RX four element phased-array at 60 GHz with RF-IF conversion block in 90-nm CMOS process[J]. IEEE Transactions on Microwave Theory and Techniques, 2010, 58(5): 1438-1446. doi: 10.1109/TMTT.2010.2042902 [2] KANG D W, KIM J G, MIN B W, et al. Single and four-element Ka-band transmit/receive phased-array silicon RFICs with 5-bit amplitude and phase control[J]. IEEE Transactions on Microwave Theory and Techniques, 2009, 57(12): 3534-3543. doi: 10.1109/TMTT.2009.2033302 [3] LOHMILLER P, REBER R, SCHUH P, et al. SiGe BiCMOS X-band transceiver-chip for phased-array systems[C]//2017 European Radar Conference. [S.l.]: IEEE, 2017: 405-408. [4] SIM S, JEON L, KIM J G. A compact X-band bi-directional phased-array T/R chipset in 0.13 μm CMOS technology[J]. IEEE Transactions on Microwave Theory and Techniques, 2013, 61(1): 562-569. doi: 10.1109/TMTT.2012.2227786 [5] NGUYEN V V, NAM H, CHOE Y J, et al. An X-band bi-directional transmit/receive module for a phased array system in 65-nm CMOS[J]. Sensors, 2018, DOI: 10.3390/nano8060371. [6] GHARIBDOUST K, MOUSAVI N, KALANTARI M, et al. A fully integrated 0.18-μm CMOS transceiver chip for X-band phased-array systems[J]. IEEE Transactions on Microwave Theory and Techniques, 2012, 60(7): 2192-2202. doi: 10.1109/TMTT.2012.2195020 [7] LIU Chao, LI Qiang, LI Yi-hui, et al. A fully integrated X-band phased-array transceiver in 0.13-μm SiGe BiCMOS technology[J]. IEEE Transactions on Microwave Theory and Techniques, 2016, 64(2): 575-584. doi: 10.1109/TMTT.2015.2504977 [8] 李健康, 沈宏昌, 陈亮, 等. K波段SiGe幅相多功能芯片设计[J]. 固体电子学研究与进展, 2017, 37(1): 15-20. LI Jian-kang, SHEN Hong-chang, CHEN Liang, et al. Design of Ku-band SiGe muti-function chip with phase and amplitude control[J]. Research & Progress of SSE, 2017, 37(1): 15-20. [9] HEIJNINGEN M V, BOER A D, HOOGLAND J A, et al. Multi function and high power amplifier chipset for X-band phased array frontends[C]//Proceedings of the 1st European Microwave Integrated Circuits Conference. [S.l.]: IEEE, 2006: 237-240. [10] M/A-COM. XZ1002-BD Datasheet, 8.5-11.0 GHz GaAs MMIC core chip[EB/OL]. [2019-03-21]. http://www.digchip.comydatasheets/search.php?pn=XZ1002_BD. [11] JEONG J C, KWAK C, YOM I B, et al. Life test of an X-band MMIC muti-function chip for active phased array radar applications[J]. Microelectronics Reliability, 2015, 55(5): 815-821. doi: 10.1016/j.microrel.2015.02.002 [12] 张光义. 相控阵雷达系统[M]. 北京: 国防工业出版社, 2006. ZHANG Guang-yi. Principles of phased array radar[M]. Beijing: Nation Defense Industry Press, 2006. [13] WANG Zeng-qi, LI Nan, LIU Wei-tian, et al. A fully integrated S-band 1-Watt phased array T/R IC in 0.13μm SOI-CMOS technology[C]//2019 IEEE MTT-S International Microwave Symposium. [S.l.]: IEEE, 2019: 1237-1240. [14] 谢媛媛, 赵子润, 刘文杰, 等. 一种超小型7~8.5 GHz GaAs多功能芯片[J]. 微纳电子技术, 2016, 53(5): 281-286. XIE Yuan-yuan, ZHAO Zi-run, LIU Wen-jie, et al. A microminiature 7-8.5 GHz muti-function chip[J]. Micronanoelectronic Technology, 2016, 53(5): 281-286. [15] XIONG Yi-tong, WANG Guo-qiang. An X-band 6-bits highly-accurate digital-stepped phase shifter MMIC for phased array system[C]//2017 3rd IEEE International Conference on Computer and Communications. [S.l.]: IEEE, 2017: 826-829. [16] ZHENG Qin, WANG Zhi-yu, WANG Kang-rui, et al. Design and performance of a wideband Ka-band 5-b MMIC phase shifter[J]. IEEE Microwave and Wireless Components Letters, 2017, 27(5): 482-484. doi: 10.1109/LMWC.2017.2690828 [17] YUAN Ye, MU Shan-xiang, GUO Yong-xin. 6-bit step attenuators for phased-array system with temperature compensation technique[J]. IEEE Microwave and Wireless Components Letters, 2018, 28(8): 690-692. doi: 10.1109/LMWC.2018.2849224 [18] WANG Kang-rui, WANG Zhi-yu, WANG Gang, et al. Design of a low insertion phase shifter MMIC attenuator intergrated with a serial-to-parallel converter[J]. IEICE Electronics Express, 2017, 14(20): 1-7. [19] JEONG J C, YOM I B, KIM J D, et al. A 6-18 GHz mutifunction chip with 8-bit true time delay and 7-bit amplitude control[J]. IEEE Transactions on Microwave Theory and Techniques, 2018, 66(5): 2220-2230. doi: 10.1109/TMTT.2017.2786698 [20] OMMIC. CGY2170YUH-C1 Datasheet, 6-bit X-band corechip[EB/OL]. [2019-03-22]. http://www.ommic.com/datasheets/OMMIC_DATASHEET_CORECHIP_CGY2170YUH-C1.pdf. [21] UMS. CHC3014-99F Datasheet, X-band core chip[EB/OL]. [2019-03-22]. http://www.ums-gaas.com/wp-content/uploads/2017/01/CHC3014-99F-Full-0293.pdf. -

ISSN

ISSN

下载:

下载: