-

2020年3月4日,我国政府提出加快5G网络、特高压、大数据中心、城际高速铁路和城市轨道交通、新能源汽车充电桩、人工智能、工业互联网等新型基础设施建设进度[1],简称“新基建”。新基建本质上是信息数字化的基础设施建设,这些设施都需要应用大量功率半导体器件和设备,尤其是在智能电网、高速动车牵引、工业级电源、舰载武器等领域,需要功率更大、速度更快、功能更丰富、效率更高的功率半导体器件。尽管体硅基或者基于绝缘衬底上的硅功率器件目前仍然是功率器件市场的主力军[2],但由于材料特性的限制,硅功率器件在耐压、工作频率以及转换效率等方面已经逼近器件性能极限,往大功率、高频化发展的局限性越来越显现。碳化硅(SiC)半导体材料以其高临界击穿电场、高热导率以及高饱和电子漂移率等优势,在超高压大功率电力电子应用领域表现出很大潜力。纵观国内外整个产业,商业化的SiC功率器件额定电压等级目前仍集中在650~3 300 V中高压领域,类型包括二极管和MOSFET等。尽管Si器件通过串联形式可以将模块电压做到10 kV以上,但是元器件数量众多,系统结构繁杂,寄生效应多。10 kV碳化硅器件无需复杂的串并联结构,减少了系统元器件数目,简化了电路拓扑结构,提高了电能转换效率。目前10 kV以上的超高压功率器件,仍处于研发试制阶段。2004年,文献[3]在110 μm/6×1014 cm−3的4H-SiC外延衬底上设计并制备出世界第一个超高压10 kV SiC MOSFET,常温下器件的比导通电阻为236 mΩ·cm2@VGS=25 V,阈值电压为10 V,泄漏电流为70 μA@VDS=10 kV。2011年,美国Cree公司、Powerex公司、GE公司和美国NIST联合基于4英寸的120 μm/6×1014 cm−3的4H-SiC外延衬底上研制出10 kV SiC MOSFET用于功率为1 MW的固态变电站[4],该芯片面积为8.1 mm×8.1 mm,比导通电阻为123 mΩ·cm2,阈值电压为3 V。当漏源电压为4 V,该MOSFET获得导通电流为10A@VGS=20 V。2017年,日本先进功率电子研究中心在150 μm/6.7×1014 cm−3的4H-SiC外延衬底上研制出一种在JFET区具有逆向掺杂分布的13.1 kV的超高压SiC MOSFET[5],其漏电流为10 μA/cm2,芯片面积为5 mm×5 mm。室温下,该器件比导通电阻为169 mΩ·cm2@VGS=20 V,VDS=1 V。对于10 kV量级的功率MOSFET,当器件处于第三象限工作时,由于MOSFET的体二极管存在,第三象限的开启电压一般会高于2.5 V,导致器件第三象限导通时的损耗加大。为了解决这个问题,行业内开始研究集成二极管的MOSFET,目前多数采用的是单片集成MOSFET和结势垒肖特基二极管(JBS)或肖特基势垒二极管(SBD)[6-7]。然而,肖特基接触会导致反向泄漏电流的增加和高温性能的下降[8]。

本文提出了一种集成低势垒二极管的10 kV SiC MOSFET器件新结构(low barrier diode-MOSFET, LBD-MOSFET)。通过二维TCAD仿真工具Silvaco进行设计和研究,器件击穿电压为13.5 kV。在第三象限工作时,低的电子势垒使LBD以更低的源漏电压开启,避免了体二极管开启导致的双极退化效应。传统平面型10 kV SiC MOSFET第三象限的开启电压为2.5 V,而LBD-MOSFET的开启电压仅1.3 V,相比降低了48%,可有效降低器件第三象限导通损耗。LBD-MOSFET的栅漏交叠面积相比传统平面型结构有所减小,可有效降低器件的栅漏电容,从而降低器件开关损耗。

-

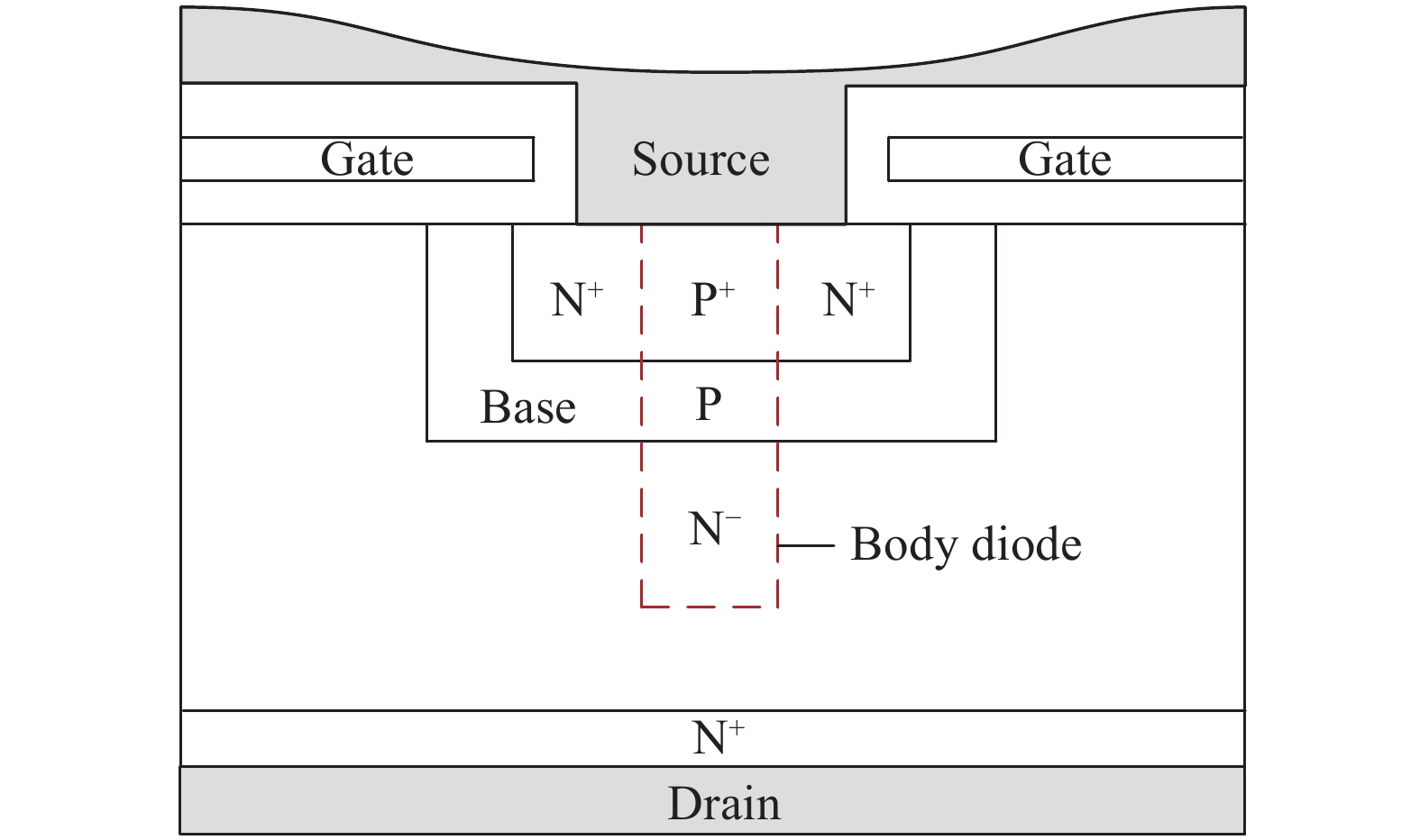

图1为常规平面型SiC MOSFET结构示意图,由P+区、P_base区和N-漂移区形成寄生体PiN二极管。当SiC MOSFET在第三象限工作时,电流从MOSFET的源端经过体二极管P+PN−流向漏端。由于SiC宽禁带、低本征载流子的特性,其体二极管开启电压远大于Si MOSFET,导致SiC MOSFET在第三象限的导通损耗比Si MOSFET更高。基平面位错(BPD)是SiC晶圆普遍存在的缺陷,当传统SiC MOSFET在第三象限工作,作为双极型器件的体二极管P+PN−导通,电子和空穴的复合释放的能量导致堆垛层错在BPD处蔓延[9-11],这种现象就是双极退化效应。双极退化效应导致SiC MOSFET的导通电阻增大,体二极管P+PN−的开启电压增大,SiC MOSFET第三象限的导通损耗增加,器件反向漏电流也会增加。

-

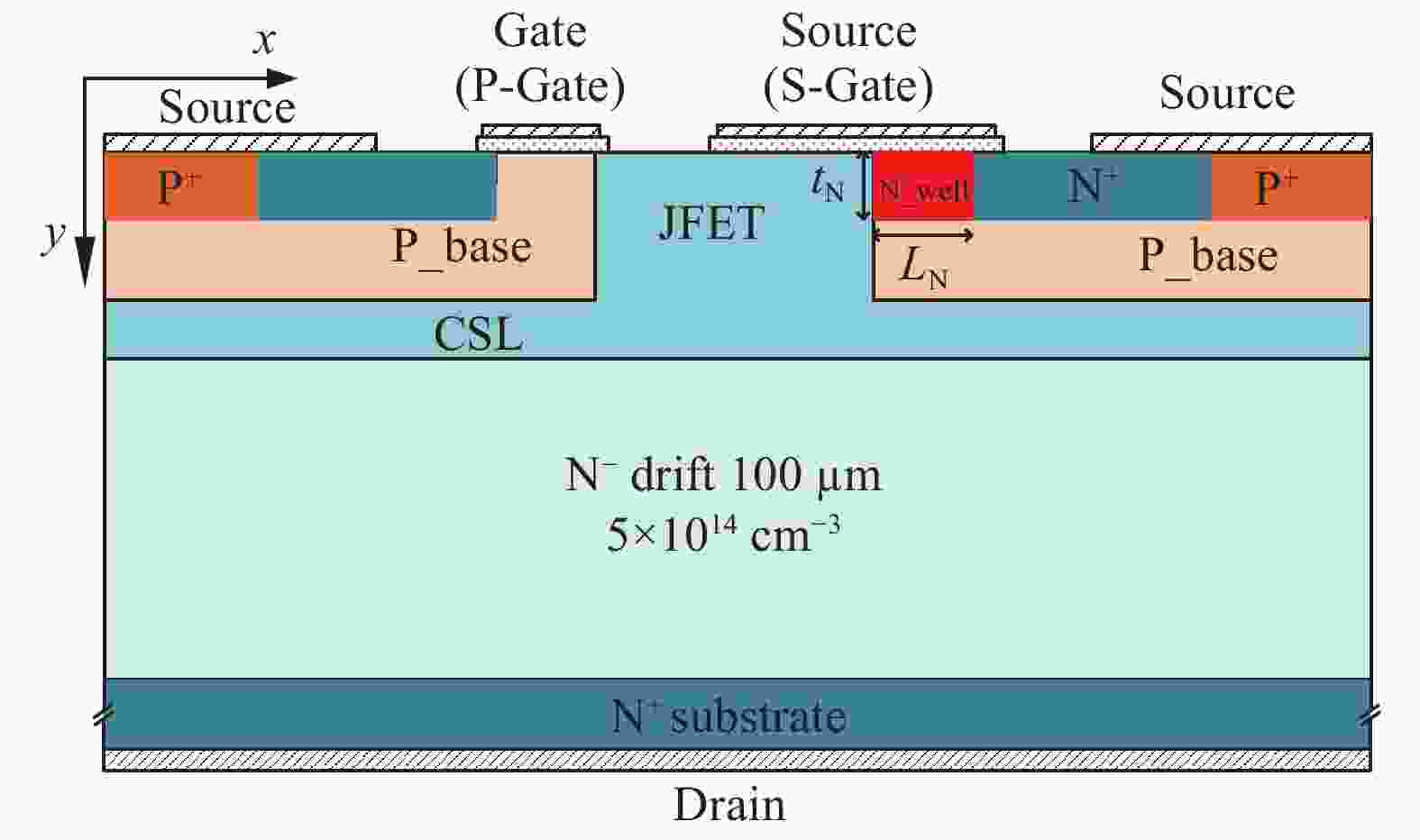

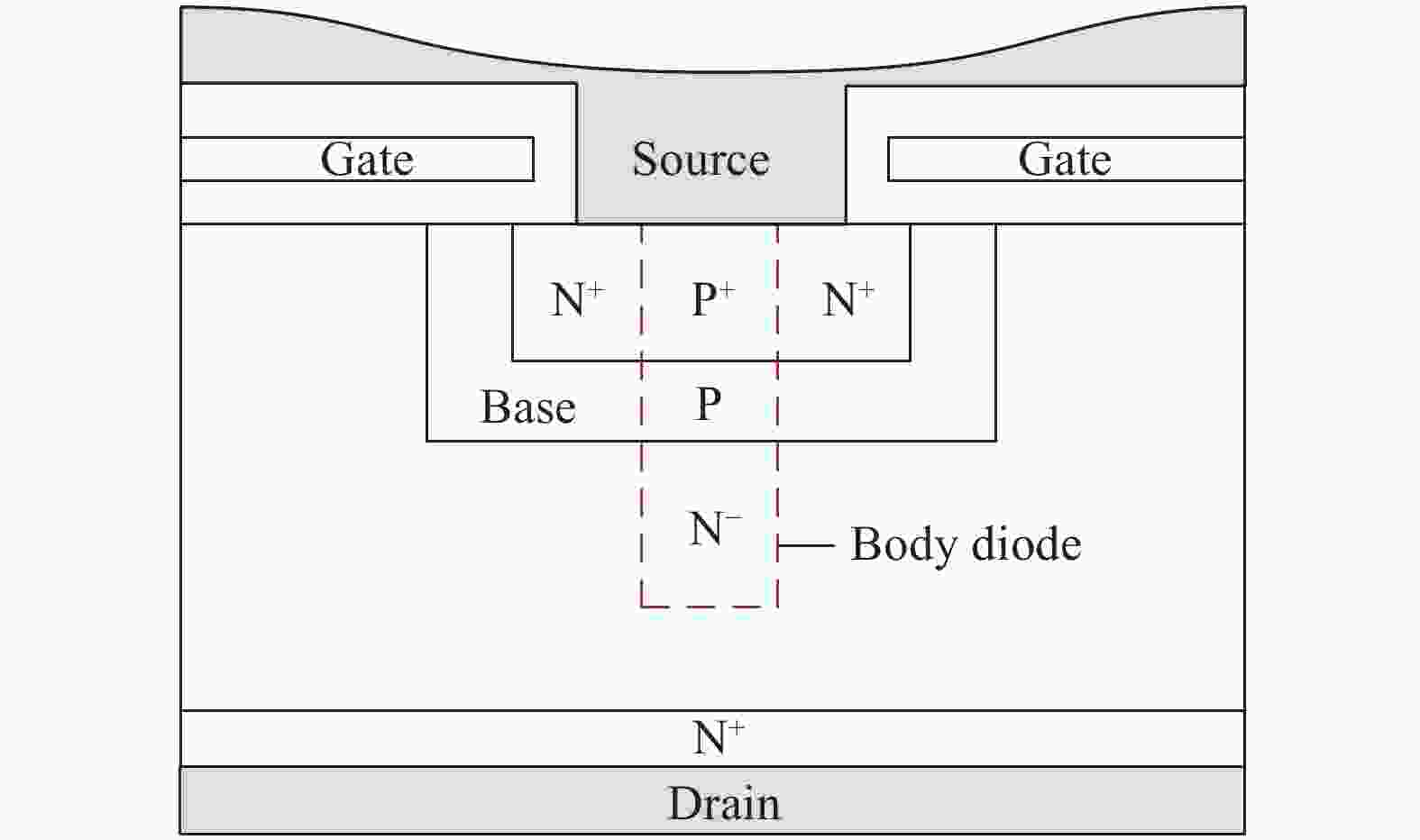

为了解决传统SiC MOSFET第三象限开启电压高,避免双极退化效应,本文提出10 kV SiC LBD-MOSFET,其截面结构如图2所示。N_well上方的多晶硅与源极短接,简称为S-Gate。引入N_well可以降低第三象限开启电压。N_well在N_well/P_base结的内建电势作用下完全耗尽,表现为常关型特性。导通状态,LBD-MOSFET由左侧P_base反型单沟道导通,虽然牺牲了一侧导电沟道,但仍有效利用了JFET区和漂移区的导电通路。反向阻断状态,器件仍主要由N− drift区承担阻断电压VDS。当器件工作在第三象限,随着VSD增大,电子在N_well表面积累,形成沟道,电流ISD的路径是从N+经过N_well、JFET区流向漏极。因此集成的LBD可以降低第三象限开启电压,消除双极退化效应。

图3标出了SiC LBD-MOSFET在不同源漏电压下,导带能级(EC)沿SiO2/SiC表面的分布。纵坐标“0”是费米能级的位置,当源漏电压为0时,N+区作为重掺杂区域,其导带位置低,趋近于零,而JFET区掺杂轻,其导带位置相比N+区更高。LBD的势垒高度随着VSD增加而降低,而低的电子势垒会使LBD以更低的源漏电压开启,当第三象限VDS达到−1.3 V时,LBD的势垒消失,单极型传导开始。

基于泊松方程,LBD势垒高度的一维表达式为:

$${V_{{\rm{LBD}}}} = \dfrac{{{\varphi _{_{{\rm{Si}}\mid {\rm{SiC}}}}} - \dfrac{{q{N_{{\rm{Nwell}}}}t_{\rm{N}}^2}}{{2{\varepsilon _{{\rm{SiC}}}}}}}}{{\dfrac{{{\varepsilon _{{\rm{ox}}}}{t_{\rm{N}}}}}{{{\varepsilon _{{\rm{SiC}}}}{t_{{\rm{ox}}}}}} + 1}} + {\chi _{_{{\rm{Si}}\mid {\rm{SiC}}}}}$$ (1) 式中,VLBD是势垒高度;

$ {\varphi _{_{{\rm{Si}}\mid {\rm{SiC}}}}} $ 和χSi|SiC分别是Si和SiC的功函数之差和电子亲和能之差;NNwell和tN分别是N_well区的浓度和厚度;q是单位电子电荷;εox和εSiC分别是SiO2和SiC的介电常数。SiC LBD-MOSFET相比平面型SiC MOSFET,具有不同的第三象限开启机制。新结构利用集成的低势垒二极管抑制了体二极管的开启,进而避免了体二极管开启导致的双极退化效应。因此,SiC LBD-MOSFET的第三象限特性可获得较大提升。 -

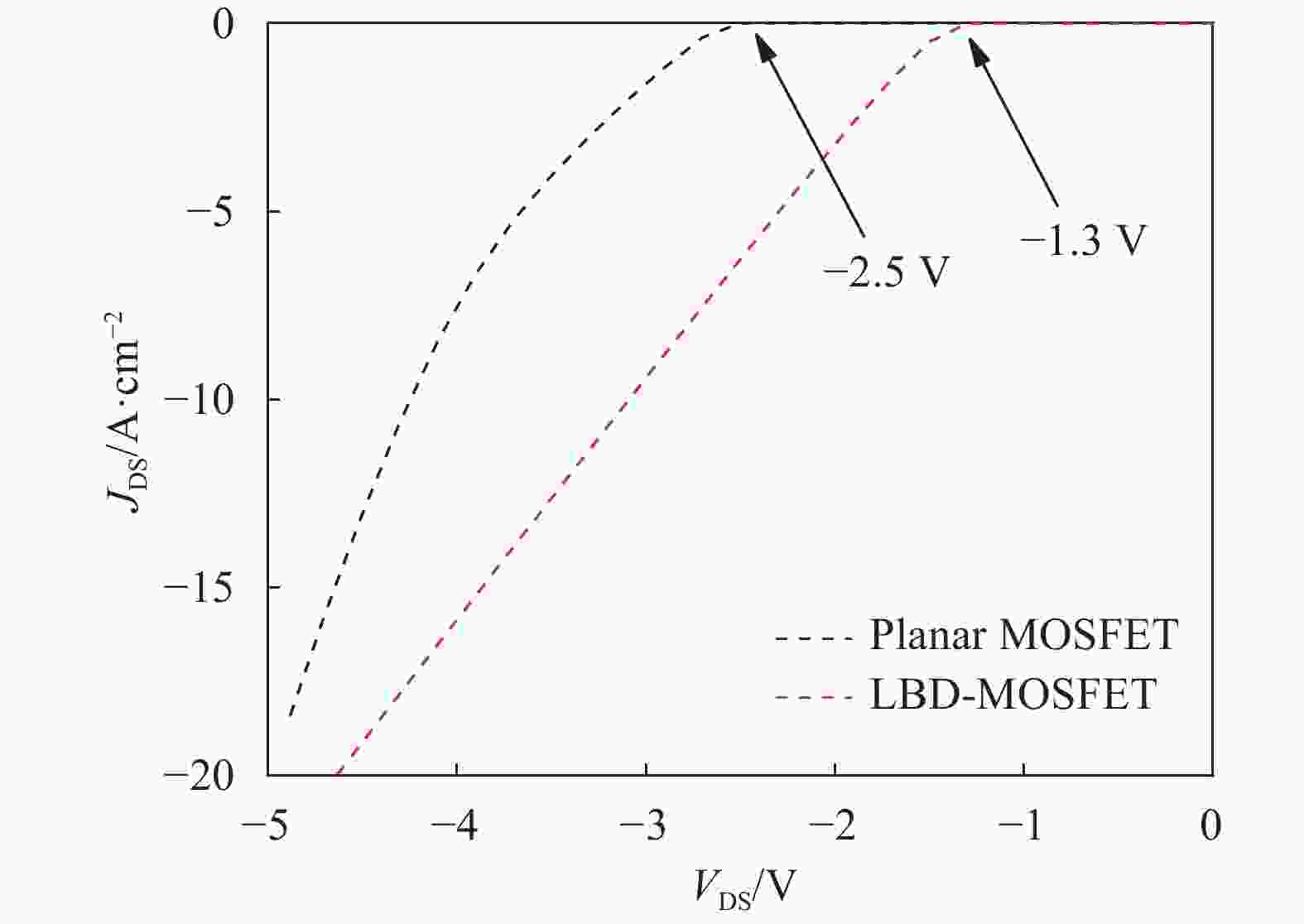

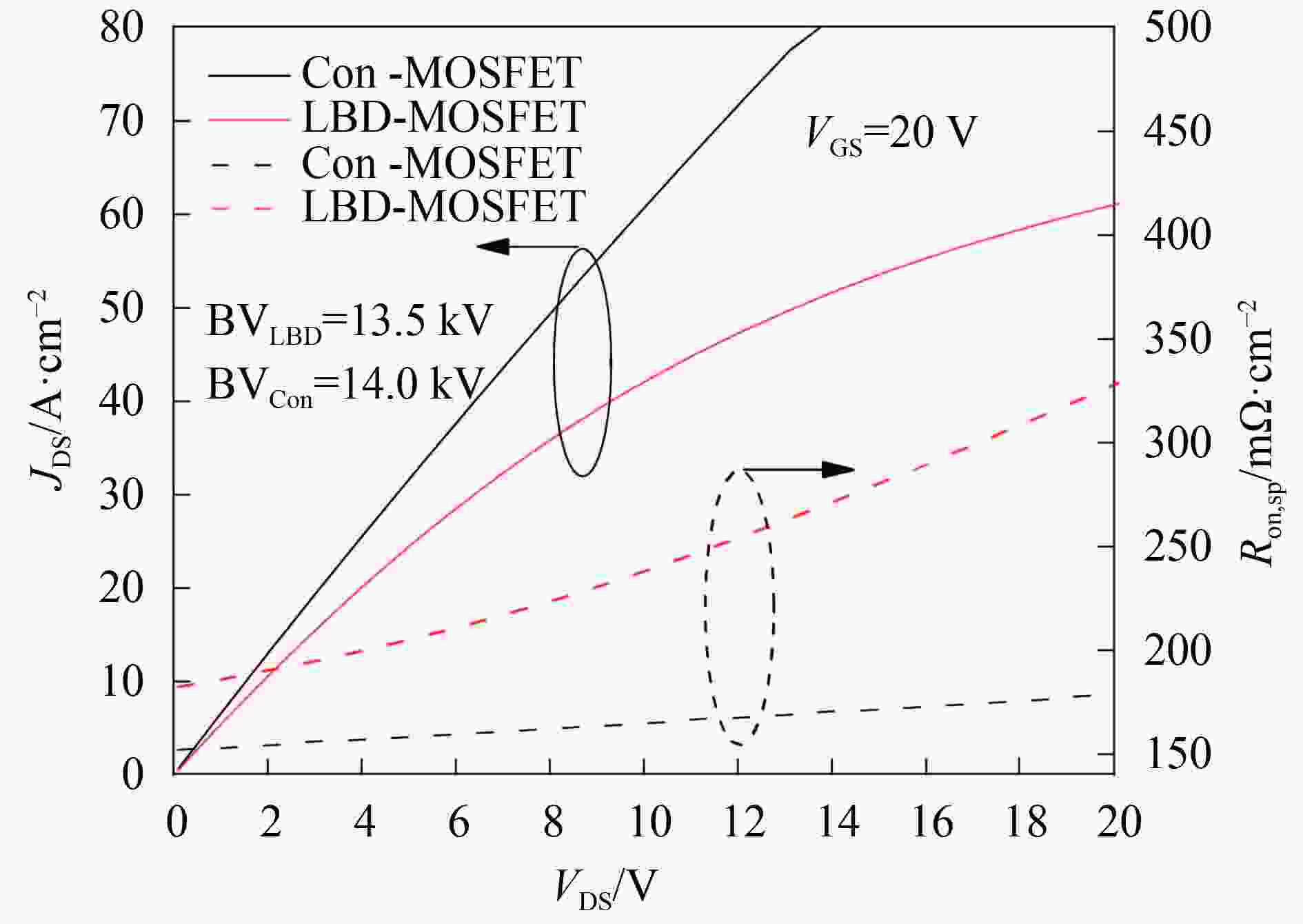

本文设计的10 kV LBD-MOSFET结构参数如下:N_well浓度为5×1016 cm−3;N_well厚度tN=0.2 μm;N_well长度LN=0.5 μm;栅氧化层厚度tox=60 nm;JFET宽度WJFET=2.2 μm。作为比较的传统MOSFET,其结构参数与LBD-MOSFET一致。两种结构的第三象限特性对比如图4所示。LBD-MOSFET由于低的电子势垒而提前导通,从而抑制体二极管开启,拥有更优的第三象限特性。LBD-MOSFET的第三象限开启电压Von为1.3 V,相比传统平面型MOSFET的开启电压Von为2.5 V,下降了48%,可以有效降低器件在第三象限的导通损耗。

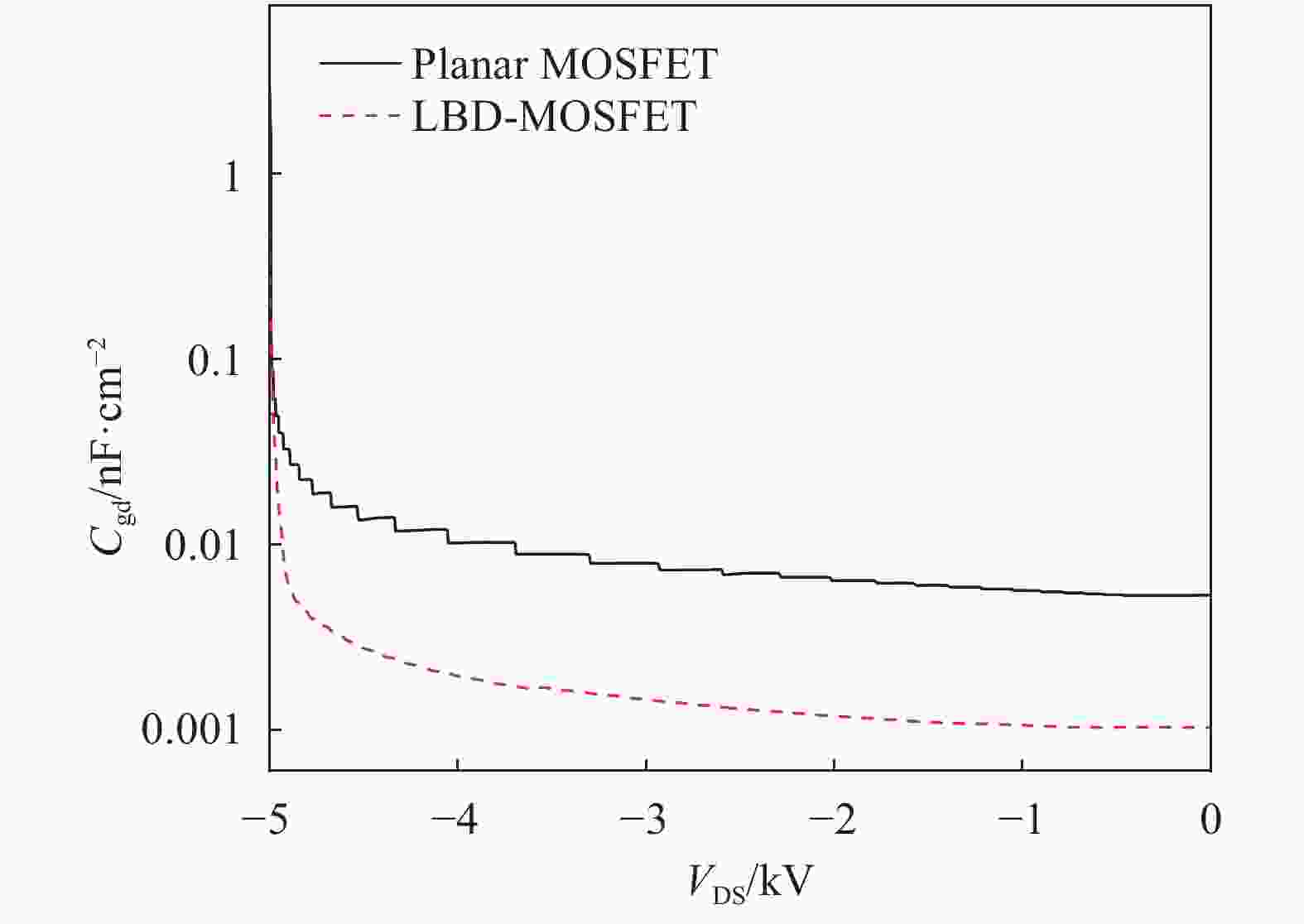

LBD-MOSFET与传统MOSFET的电容特性对比如图5所示。由于LBD-MOSFET的栅漏两极交叠面积更小,对应栅漏电容Cgd明显小于平面型MOSFET。当VDS=5 kV时,传统平面型MOSFET的栅漏电容Cgd为5.2 pF/cm2,LBD-MOSFET的Cgd为1.0 pF/cm2,降低了81%。传统平面型的高频优值(Ron×Cgd)为806 mΩ·pF,LBD-MOSFET的高频优值为194 mΩ·pF,降低了76%,因此LBD-MOSFET更适用于高频应用。

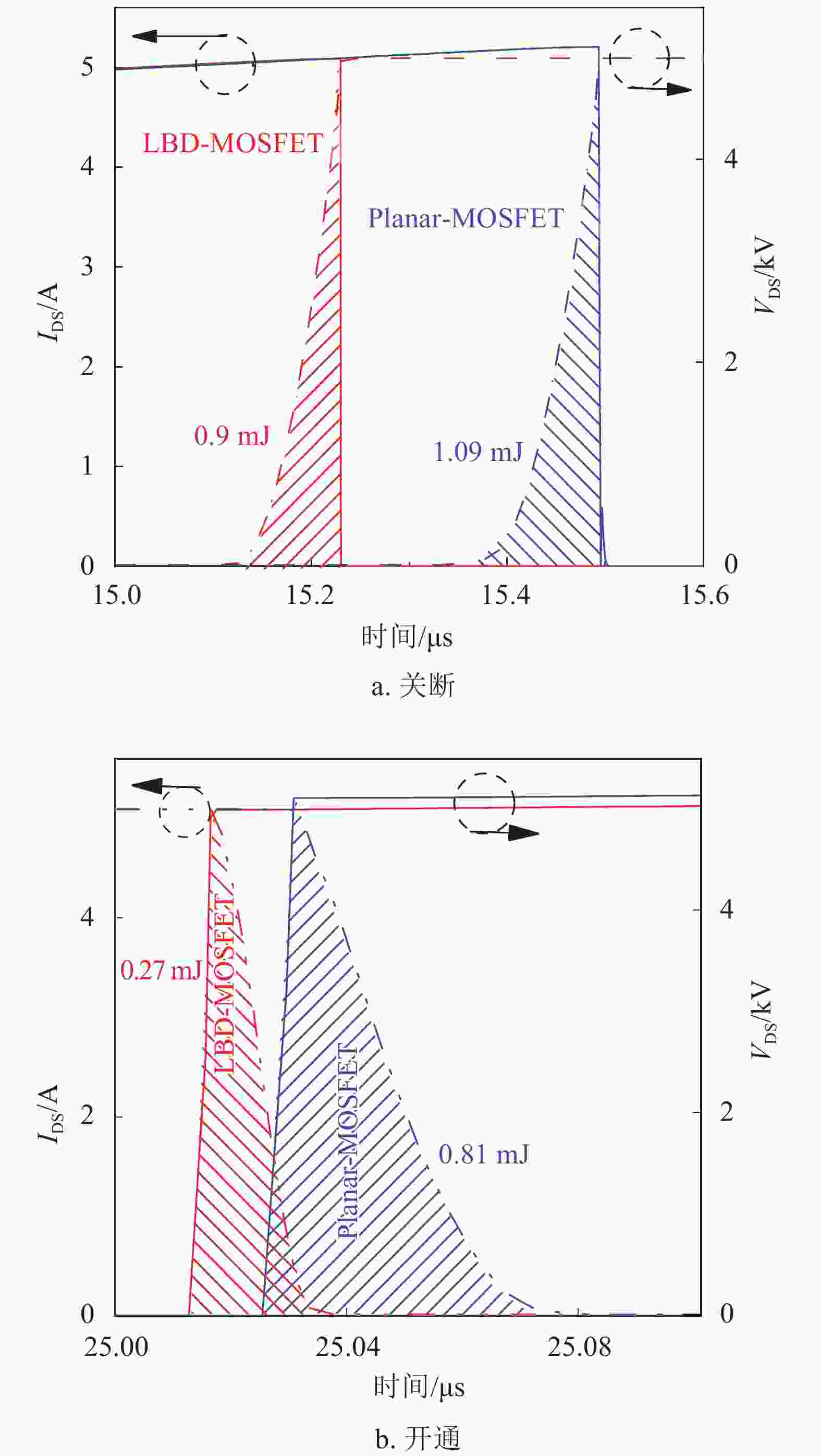

LBD-MOSFET和传统平面型MOSFET的开关波形如图6所示。传统平面型MOSFET的开启损耗为0.81 mJ,LBD-MOSFET的开启损耗为0.27 mJ,相比降低了66.7%。传统平面型MOSFET的关断损耗为1.09 mJ,LBD-MOSFET的关断损耗为0.90 mJ,相比降低了17.4%。

LBD-MOSFET与传统MOSFET的击穿电压和正向导通特性对比如图7所示。LBD-MOSFET击穿电压为13.5 kV,达到传统平面型SiC MOSFET击穿电压的96%,达到理论平行平面结构的95.7%。由于缺少一个正向导通沟道,因此LBD-MOSFET的正向特性略差于平面型MOSFET。器件虽然牺牲了一侧导电沟道,但仍有效利用了JFET区和漂移区的导电通路,因此在线性区,VGS=20 V,VDS=3 V,LBD-MOSFET比导通电阻Ron,sp=194 mΩ·cm2,是传统MOSFET比导通电阻155 mΩ·cm2的1.25倍。

-

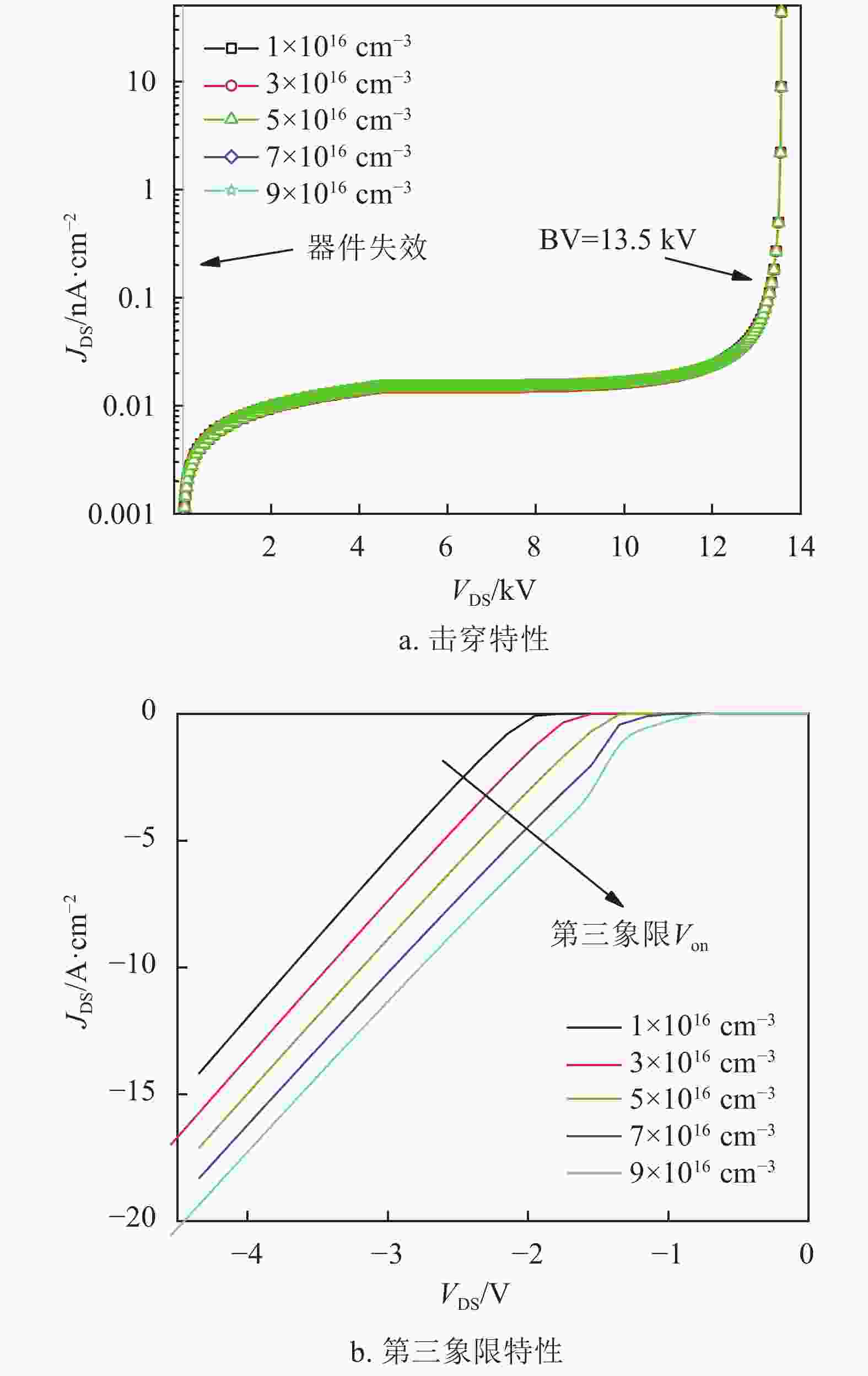

N_well浓度越低,器件阻断时,N_well区越容易在N_well/P_base内建电势作用下发生耗尽,N_well区没有电子沟道形成,有助于提升器件第一象限的阻断能力。但是N_well浓度降低,会造成LBD的势垒升高,导致N_well表面形成积累电子层所需的源漏电压增大,造成第三象限导通损耗增加。因此,N_well浓度需要进行折中优化。不同N_well浓度下器件的击穿特性和第三象限特性分别如图8a和图8b所示。随着N_well浓度的增加,器件的阻断特性迅速退化,当浓度高于7×1016 cm−3后,N_well在PN结内建电势作用下无法全耗尽,存在电子沟道,器件无法阻断。设定ISD=0.1 A/cm2对应第三象限开启,当N_well浓度从1×1016 cm−3增加到9×1016 cm−3,与之对应的第三象限开启电压分别为1.95、1.60、1.30、1.14、0.86 V。N_well浓度越大,器件第三象限开启电压降低,终其原因是N_well势垒降低。器件结构基本参数如下:漂移区厚度为100 μm,漂移区掺杂浓度为5×1014 cm−3,JFET区宽度为2.2 μm,JFET浓度为2×1016 cm−3,沟道长度为0.5 μm,P_base浓度为2.1×1018 cm−3,P_base深度为1.5 μm。

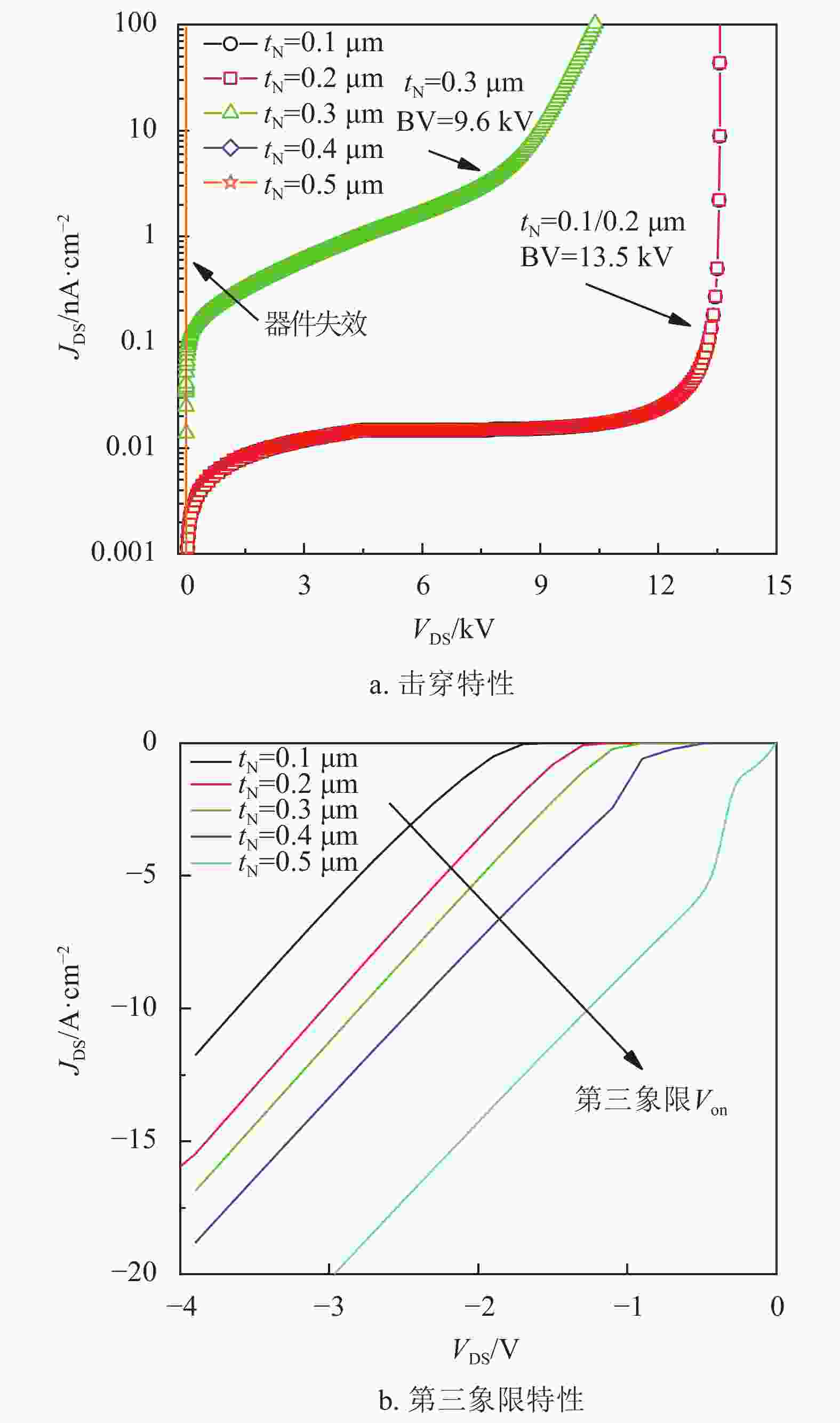

N_well厚度tN如果太大,N_well在PN结内建电势作用下可能发生不完全耗尽。器件处于阻断状态时,在靠近SiC/SiO2表面仍有可动电子,造成器件阻断时N_well发生漏电流,器件提前击穿。当器件工作在第三象限,根据式(1)的分析,tN越大,LBD的势垒降低,导致第三象限开启电压降低,进而减小器件在第三象限的导通损耗。因此N_well厚度需要折中考虑。不同N_well厚度tN对器件阻断特性和第三象限特性分别如图9a和图9b,其中N_well浓度为5×1016 cm−3。当tN=0.1 μm或0.2 μm,击穿电压达到13.5 kV,当tN=0.3 μm,击穿电压退化为9.6 kV,当tN高于0.4 μm,N_well在器件阻断态时无法完全耗尽,在N_well表面存在电子沟道,器件阻断能力失效。考虑有效击穿电压,当tN从0.1 μm增加到0.3 μm,与之对应的第三象限开启电压分别为1.72、1.30、0.98 V。

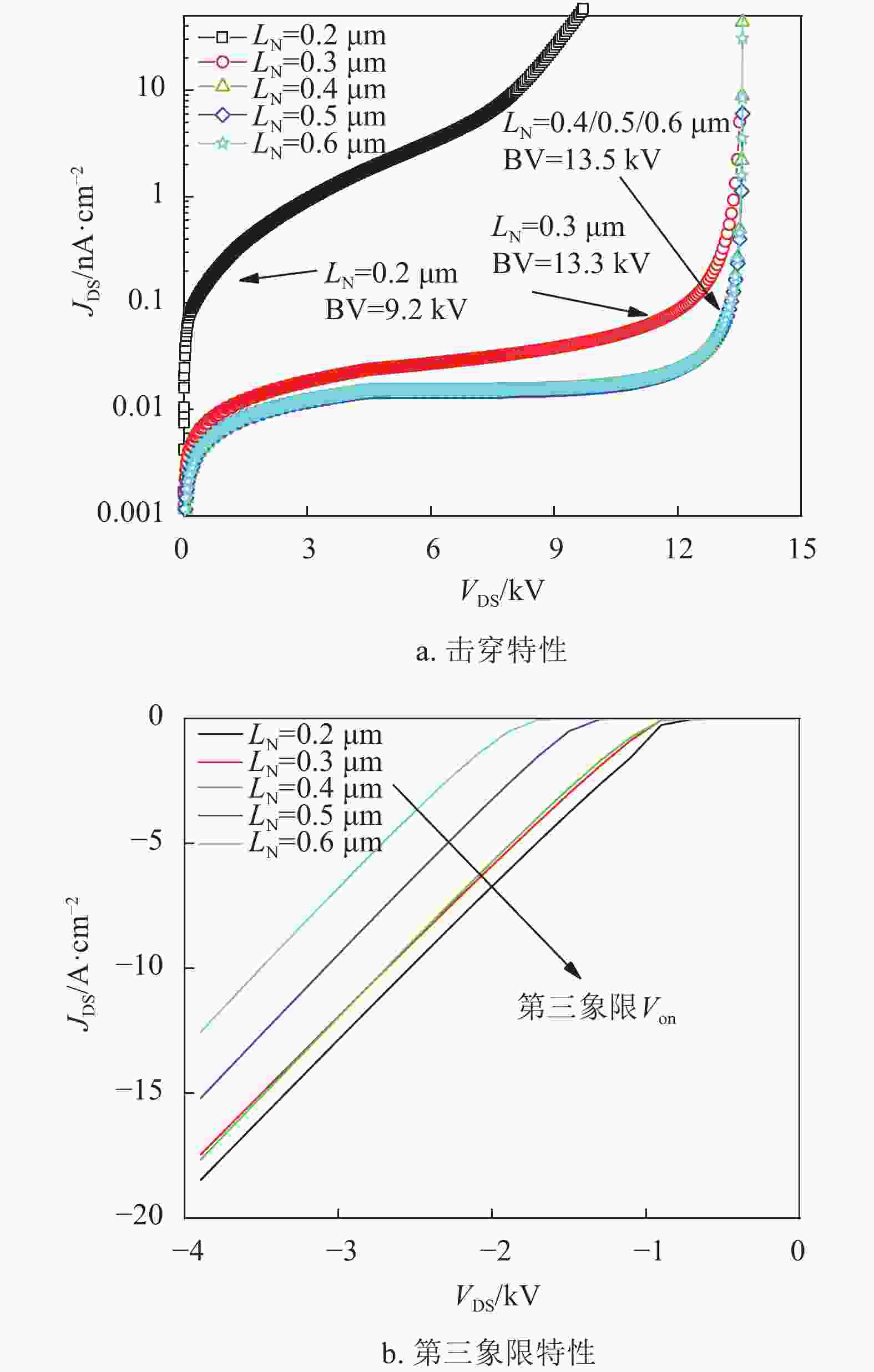

式(1)从一维上对LBD势垒进行了描述,实际上,N_well长度也会对集成二极管的势垒高度有影响。N_well长度LN对LBD-MOSFET的击穿特性和第三象限特性影响如图10a和图10b所示,其中N_well浓度为5×1016 cm−3。N_well基于横向尺寸LN对器件的性能影响相对纵向尺寸较小。击穿特性方面,当LN=0.1 μm,击穿电压低于9.2 kV,LN=0.3 μm,击穿电压增加到13.3 kV,当LN≥0.4 μm,击穿电压维持在13.5 kV。考虑到有效击穿电压,当LN从0.3 μm增加到0.6 μm,与之对应的第三象限开启电压分别为0.91、0.92、1.30、1.73 V。

-

不同栅氧厚度tox对应LBD-MOSFET的阈值电压如图11所示。LBD-MOSFET的N_well在正向导通时N_well全耗尽,正向电流通过P_base沟道流经JFET区,阈值电压与传统MOSFET几乎一致,当tox低于60 nm,阈值电压Vth均低于5 V,考虑到器件容易受环境干扰导致误开启,tox=60 μm对应阈值电压Vth=5.5 V较合适。

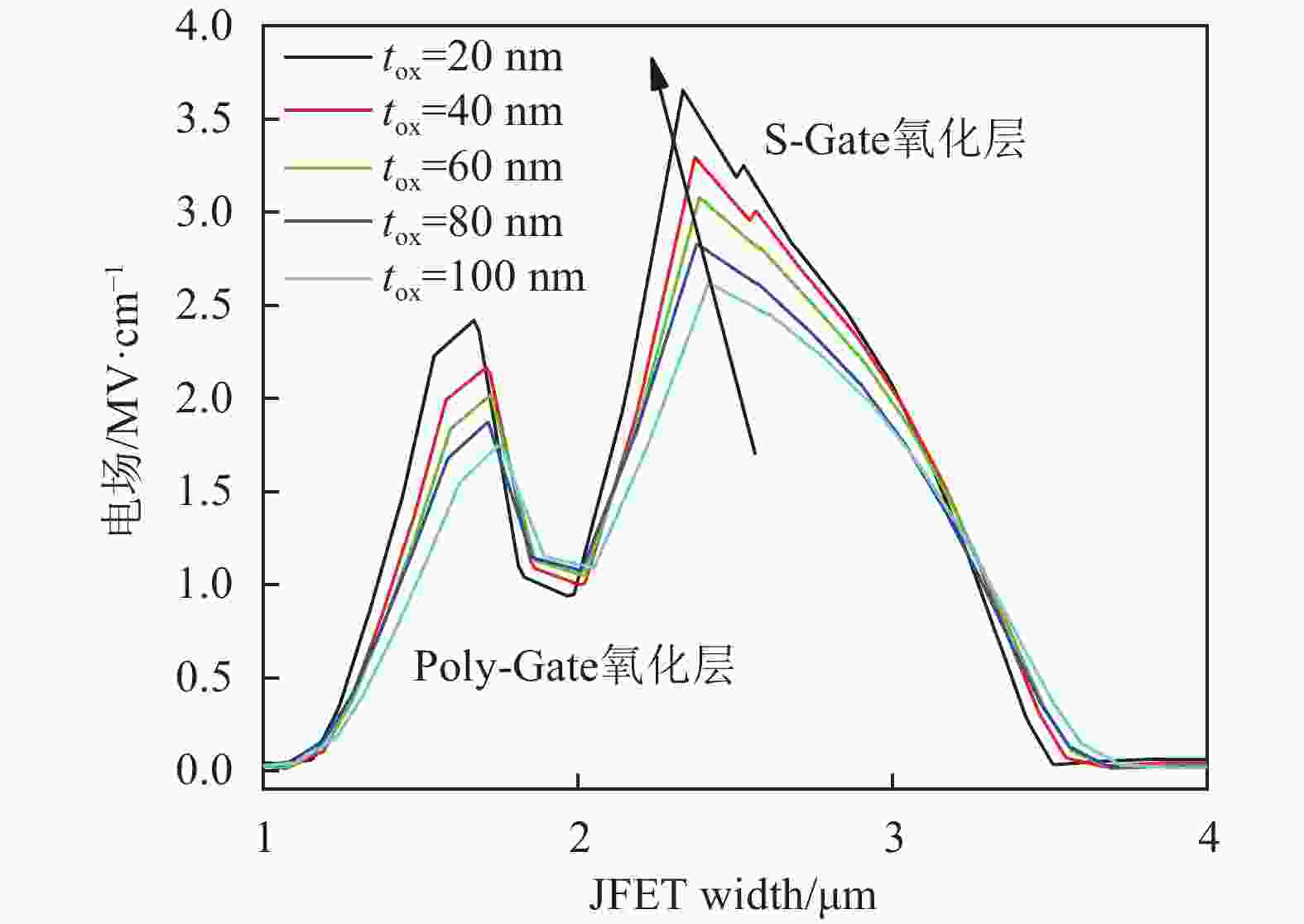

tox降低将伴随栅氧化层电场的增加,当tox低于60 nm时,阻断状态下S-Gate下氧化层电场已经超过3 MV/cm,长期工作可能带来栅氧可靠性问题。不同tox对应器件栅氧化层中的电场分布如图12所示。

若tox过大,器件在第三象限时LBD的导通电压大,造成第三象限通损耗增大;若tox过小,除了引起栅氧电场过大导致可靠性问题外,根据LBD势垒高度式(1)可知,LBD势垒将减小,在器件导通时,N_well可能耗尽不充分,在N_well处发生漏电。tox对于器件第三象限特性影响如图13所示。设定ISD=0.1 A/cm2对应第三象限开启,当tox从20 nm增加到100 nm,与之对应的第三象限开启电压分别为0.63、1.06、1.30、1.46、1.52 V。

-

本文提出一种集成低势垒二极管的10 kV LBD-MOSFET新结构,通过形成一个低势垒二极管(LBD),降低器件第三象限的开启电压,从而有效避免体二极管开启所导致的双极退化效应。LBD-MOSFET击穿电压为13.5 kV,在第三象限工作时,开启电压为1.3 V,相比传统平面型SiC MOSFET 2.5 V的开启电压,降低了48%,可有效降低器件第三象限导通损耗。同时,LBD-MOSFET的栅漏电容Cgd仅为1.0 pF/cm2,相比传统平面型SiC MOSFET的Cgd为5.2 pF/cm2,降低了81%。LBD-MOSFET的开启损耗为0.27 mJ,关断损耗为0.90 mJ,相比传统结构分别降低了66.7%和17.4%,因此更适用于高频应用。

Design and Characteristics of a Novel 10 kV SiC MOSFET Embedding Low Barrier Diode

-

摘要: 针对SiC MOSFET体二极管双极退化效应,该文提出了一种集成低势垒二极管的10 kV SiC MOSFET器件新结构(LBD-MOSFET)。该结构通过在一侧基区上方注入N阱,降低了漏源间的电子势垒,从而在元胞中形成一个低势垒二极管(LBD)。当LBD-MOSFET在第三象限工作时,低的电子势垒使LBD以更低的源漏电压开启,有效避免了体二极管开通所导致的双极退化效应。二维数值分析结果表明,SiC LBD-MOSFET的击穿电压达13.5 kV,第三象限开启电压仅为1.3 V,相比传统结构降低48%,可有效降低器件第三象限导通损耗。同时,由于LBD-MOSFET具有较小的栅漏交叠面积,其栅漏电容仅为1.0 pF/cm2,器件的高频优值为194 mΩ·pF,性能相比传统结构分别提升了81%和76%。因此,LBD-MOSFET适用于高频高可靠性电力电子系统。Abstract: In this paper, a novel 10 kV SiC MOSFET embedding low barrier diode (LBD-MOSFET) is proposed and researched to solve the bipolar degradation effect in SiC MOSFET. The low barrier diode (LBD) in the cell is formed by introducing an N_well above the P_base region on one side, which reduces the electron barrier between the drain and the source. When the LBD-MOSFET works in the third quadrant, the low electronic barrier makes the LBD turn on with a lower source-drain voltage, thus effectively avoiding the bipolar degradation effect caused by the turn-on of the body diode. 2D numerical analysis results show that the breakdown voltage of the SiC LBD-MOSFET reaches 13.5 kV. In the third quadrant, the turn-on voltage is only 1.3 V, which is 48% lower than the traditional structure and effectively reduces the conduction loss of the device. At the same time, since the gate-drain overlap area of the LBD-MOSFET is reduced compared to the traditional MOSFET, the Cgd is only 1.0 pF/cm2 and the high-frequency merit value of the device is 194 mΩ·pF, which are reduced by 81% and 76% compared with the traditional MOSFET, respectively. Therefore, the LBD-MOSFET is suitable for high-frequency and high-reliability power electronic systems.

-

Key words:

- breakdown voltage /

- gate-source capacitance /

- low barrier diode /

- SiC /

- The third quadrant

-

[1] 盘和林, 胡霖, 杨慧. 新基建-中国经济新引擎[M]. 北京: 中国人民大学出版社, 2020. PAN He-lin, HU Lin, YANG Hui. New infrastructure-the new engine of the economy of China[M]. Beijing: China Renmin University Press, 2020. [2] BALIGA B J. Fundamentals of power semiconductor devices[M]. [S.l.]: Springer, 2010. [3] RYU S H, AGARWAL A K, KRISHNASWAMI S, et al. Development of 10 kV 4H-SiC power DMOSFETs[C]//Materials Science Forum. [S.l.]: Trans Tech Publications, 2004: 1385-1388. [4] GRIDER D, DAS M, AGARWAL A, et al. 10 kV/120 A SiC DMOSFET half H-bridge power modules for 1 MVA solid state power substation[C]//2011 IEEE Electric Ship Technologies Symposium. [S.l.]: IEEE, 2011: 131-134. [5] KITAI H, HOZUMI Y, SHIOMI H, et al. Low on-resistance and fast switching of 13-kV SiC MOSFETs with optimized junction field-effect transistor region[C]//2017 29th International Symposium on Power Semiconductor Devices and IC's (ISPSD). Sapporo: IEEE, 2017: 343-346. [6] SAITO K, MIYOSHI T, KAWASE D, et al. Simplified model analysis of self-excited oscillation and its suppression in a high-voltage common package for Si-IGBT and SiC-MOS[J]. IEEE Transactions on Electron Devices, 2018, 65(3): 1063-1071. doi: 10.1109/TED.2018.2796314 [7] TOMINAGA T, HINO S, MITSUI Y, et al. Superior switching characteristics of SiC-MOSFET embedding SBD[C]//2019 31st International Symposium on Power Semiconductor Devices and IC's (ISPSD). [S.l.]: IEEE, 2019: 27-30. [8] SUNG W, BALIGA B J. On developing one-chip integration of 1.2 kV SiC MOSFET and JBS diode (JBSFET)[J]. IEEE Transactions on Industrial Electronics, 2017, 64(10): 8206-8212. doi: 10.1109/TIE.2017.2696515 [9] AIBA R, OKAWA M, KANAMORI T, et al. Experimental demonstration on superior switching characteristics of 1.2 kV SiC SWITCH-MOS[C]//2019 31st International Symposium on Power Semiconductor Devices and IC's (ISPSD). [S.l.]: IEEE, 2019: 23-26. [10] RYU S H, HUSNA F, HANEY S K, et al. Effect of recombination-induced stacking faults on majority carrier conduction and reverse leakage current on 10 kV SiC DMOSFETs[C]//Materials Science Forum. [S.l.]: Trans Tech Publications, 2009: 1127-1130. [11] PETERS D, SIEMIENIEC R, AICHINGER T, et al. Performance and ruggedness of 1200V SiC - Trench - MOSFET[C]//2017 29th International Symposium on Power Semiconductor Devices and IC's (ISPSD). Sapporo: IEEE, 2017: 239-242. -

ISSN

ISSN

下载:

下载: