-

空间辐照环境中的等离子体、俘获粒子、太阳粒子和宇宙射线等辐射离子入射到半导体器件材料时,会产生大量的电子空穴对[1-4],造成载流子浓度梯度和器件电场分布的暂时紊乱,导致集成电路内部发生单粒子效应(single event effect, SEE)。因此,应用于卫星通信、空间站、空间探测器等空间飞行器的集成电路需要进行辐照加固设计。单粒子翻转(single event upset, SEU)是一种常见的单粒子效应,可能导致集成电路内部触发器、锁存器和存储单元状态发生改变,引起电路功能失效。

在采用先进工艺制造的超大规模集成电路应用辐照环境中,由于其工作电压降低、器件尺寸减小、阈值电压变小、工作频率升高、器件密度增加等多重因素的综合作用,单粒子翻转效应越来越严重[5-7]。先进工艺节点的新结构、新工艺、新材料表现出的单粒子效应新现象、新机理得到众多学者的研究,如电荷共享效应、脉宽压缩效应等[8-10],进一步揭示了先进工艺节点单粒子瞬态脉冲和单粒子翻转形成的过程,深入分析了单粒子入射过程中载流子电荷产生、运输、收集和脉冲形成的机理。目前,针对触发器单粒子翻转加固,在电路级采取的主要措施包括采用加固型触发器,如双互锁触发器(dual interlocked storage cell, DICE)、whitaker型触发器、muller-c型触发器等[11-13];另一种途径则是采用三模冗余(triple modular redundancy, TMR)加固方式,如空间三模冗余(spatial TMR)和时间三模冗余(temporal TMR) [14-16]。

本文基于65 nm体硅CMOS超深亚微米工艺,针对普通触发器、2种DICE触发器、普通触发器空间三模冗余、2种普通触发器时间三模冗余这6种结构,采用移位寄存器链方式分别进行单粒子翻转试验评估,并结合各种加固方式的面积、性能、晶体管数量和抗单粒子翻转性能进行综合分析,为后续先进工艺超大规模集成电路触发器单粒子翻转效应加固提供一定的指导性建议。

-

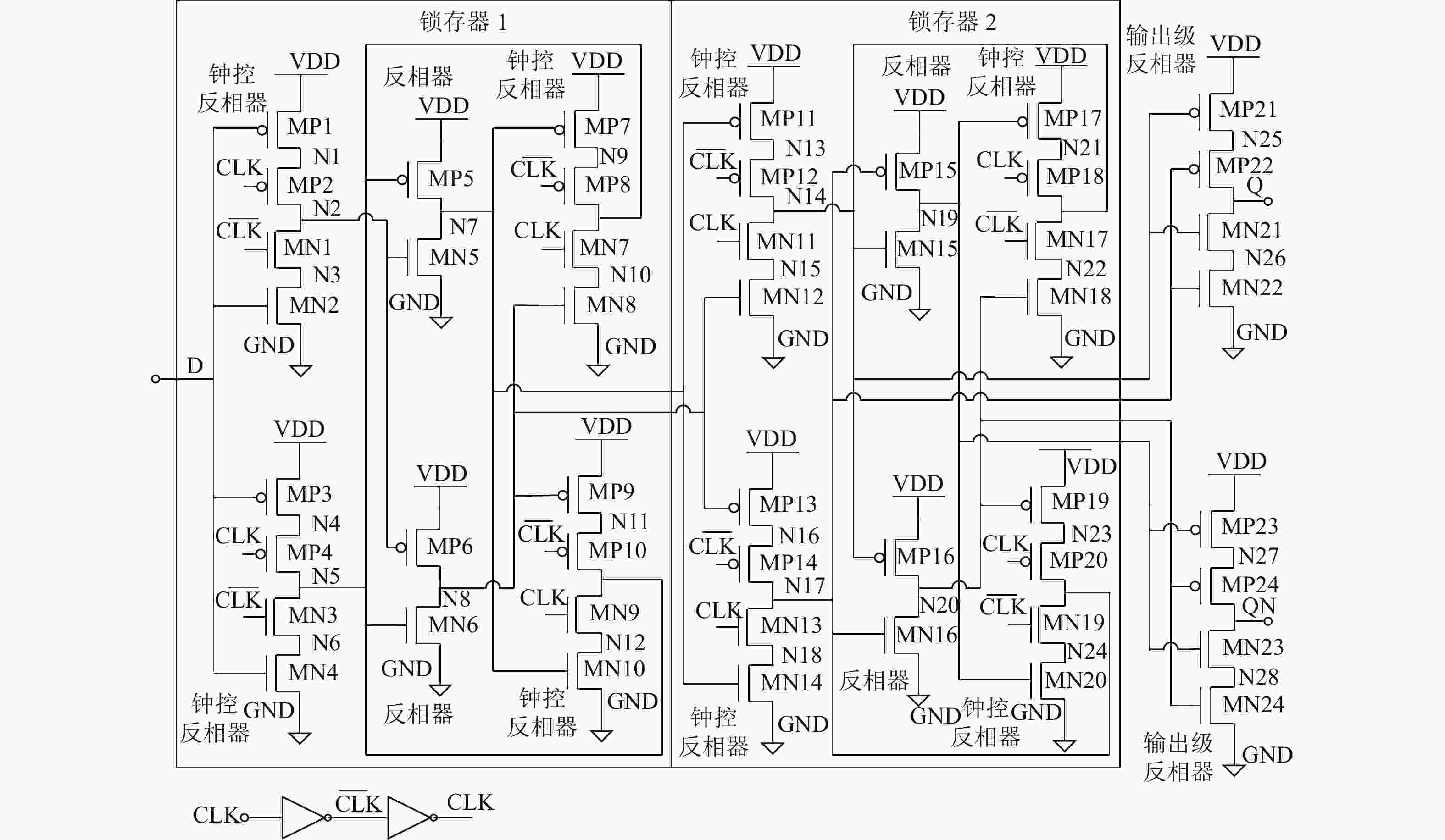

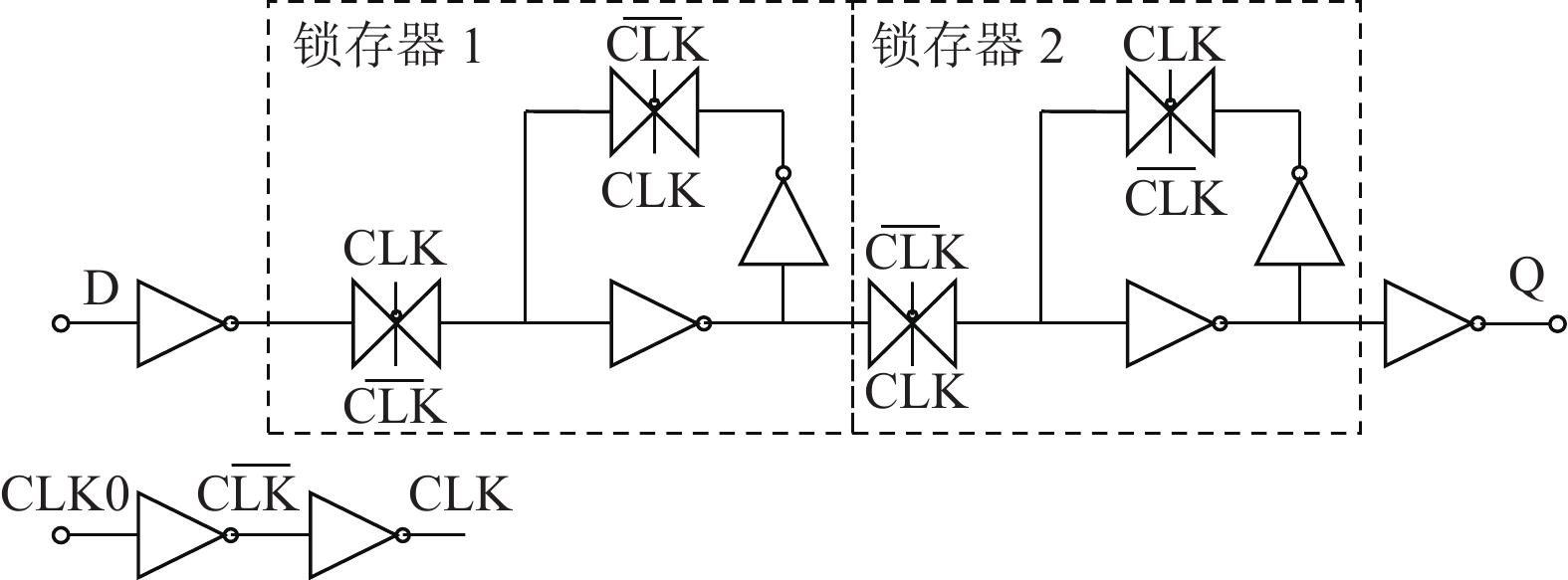

普通触发器电路结构如图1所示,由两级锁存器构成,包含8个反相器和4个传输门,当时钟信号CLK由“0”跳变为“1”时,触发器输出端信号Q随输入端信号“D”发生改变。若采用该触发器,当锁存器中的节点发生单粒子翻转时,触发器输出端Q会输出错误的状态。

-

DICE触发器电路结构如图2所示,包括两级锁存器,内部反相器、钟控反相器和输出驱动反相器采用muller-C结构设计,为上升沿跳变型DICE触发器。针对该触发器结构,当锁存器内部仅有一个节点发生单粒子翻转时,由于此时muller-C结构单元输出为高阻态,避免了DICE触发器输出错误状态。为评估辐照环境下电荷共享效应对单粒子翻转的影响,基于该DICE触发器电路,设计两种不同的版图方案:1)版图设计简便,但相关敏感节点距离较近,间距约为2.5 μm,如N2和N5是一对相关敏感节点;2)版图设计较复杂,相关敏感节点距离较远,间距约为5.7 μm。

-

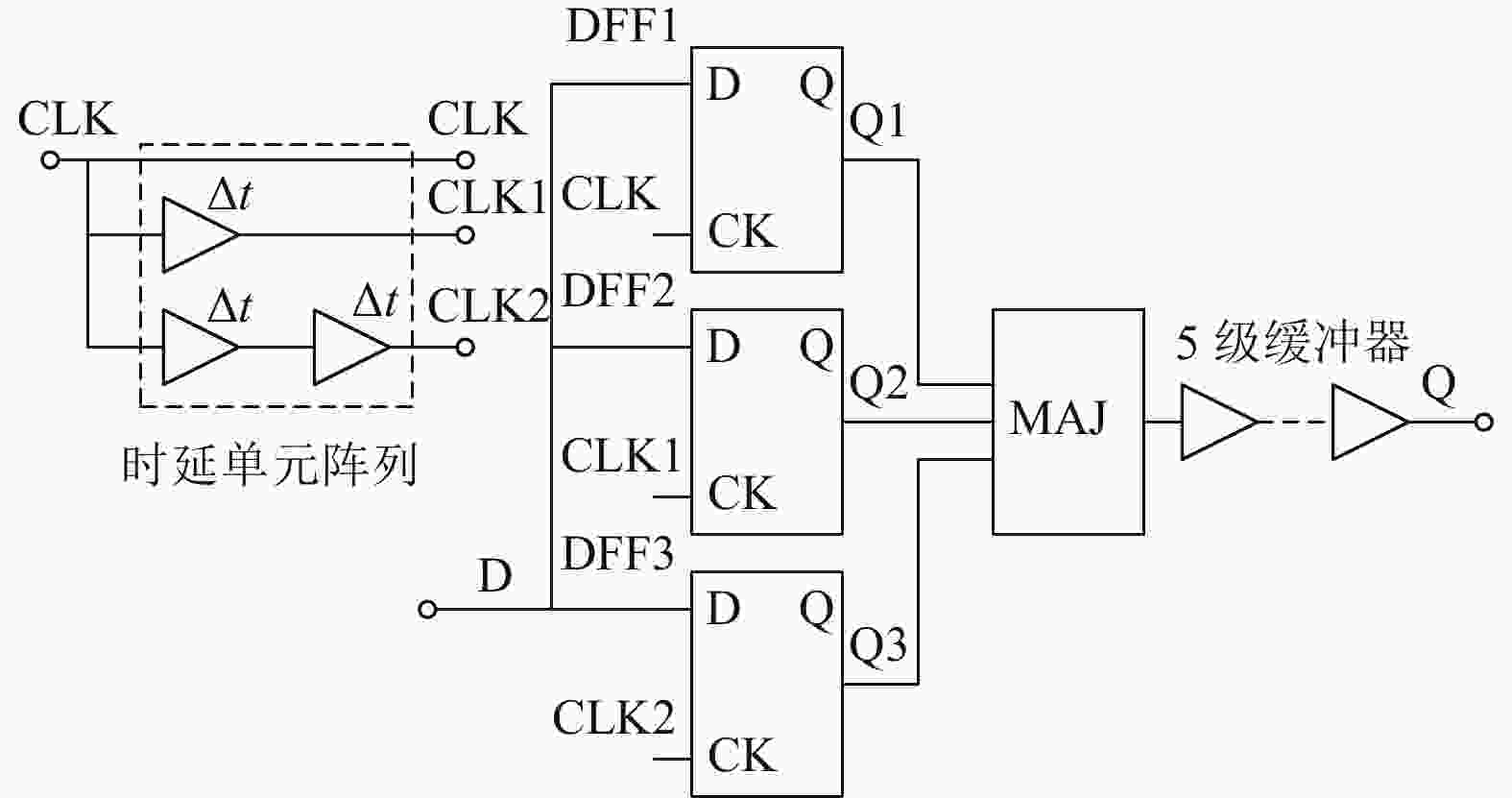

普通触发器空间三模电路结构如图3所示,包含3个普通触发器、1个三选二多路判决器和五级缓冲器,五级缓冲器的作用是模拟实际电路中触发器单元之间的组合逻辑。当DFF1、DFF2和DFF3这3个触发器中任意一个发生单粒子翻转时,由于其他两个触发器仍然保持正确的输出状态,所以判决器MAJ的输出信号Q仍然正确,实现触发器的单粒子翻转加固设计。但当判决器和5级缓冲器产生单粒子瞬态脉冲时,下一级空间三模电路结构无法纠正该错误。

-

普通触发器时间三模电路结构如图4所示,包括1个时延单元阵列、3个普通触发器、1个三选二判决器和五级缓冲器,其中时延单元阵列产生时间间隔为

$ \Delta t$ 的三路时钟信号,分别控制3个触发器。首先,当触发器DFF1、DFF2和DFF3中的任意一个发生单粒子翻转时,判决器MAJ保持正确状态输出;其次,判决器和5级缓冲器产生单粒子瞬态脉冲时,若其脉冲宽度小于$ \Delta t $ ,下一级判决器MAJ仍可以正确输出状态。本文主要针对$ \Delta t $ 分别等于300 ps和600 ps两种情况进行单粒子翻转试验与分析。 -

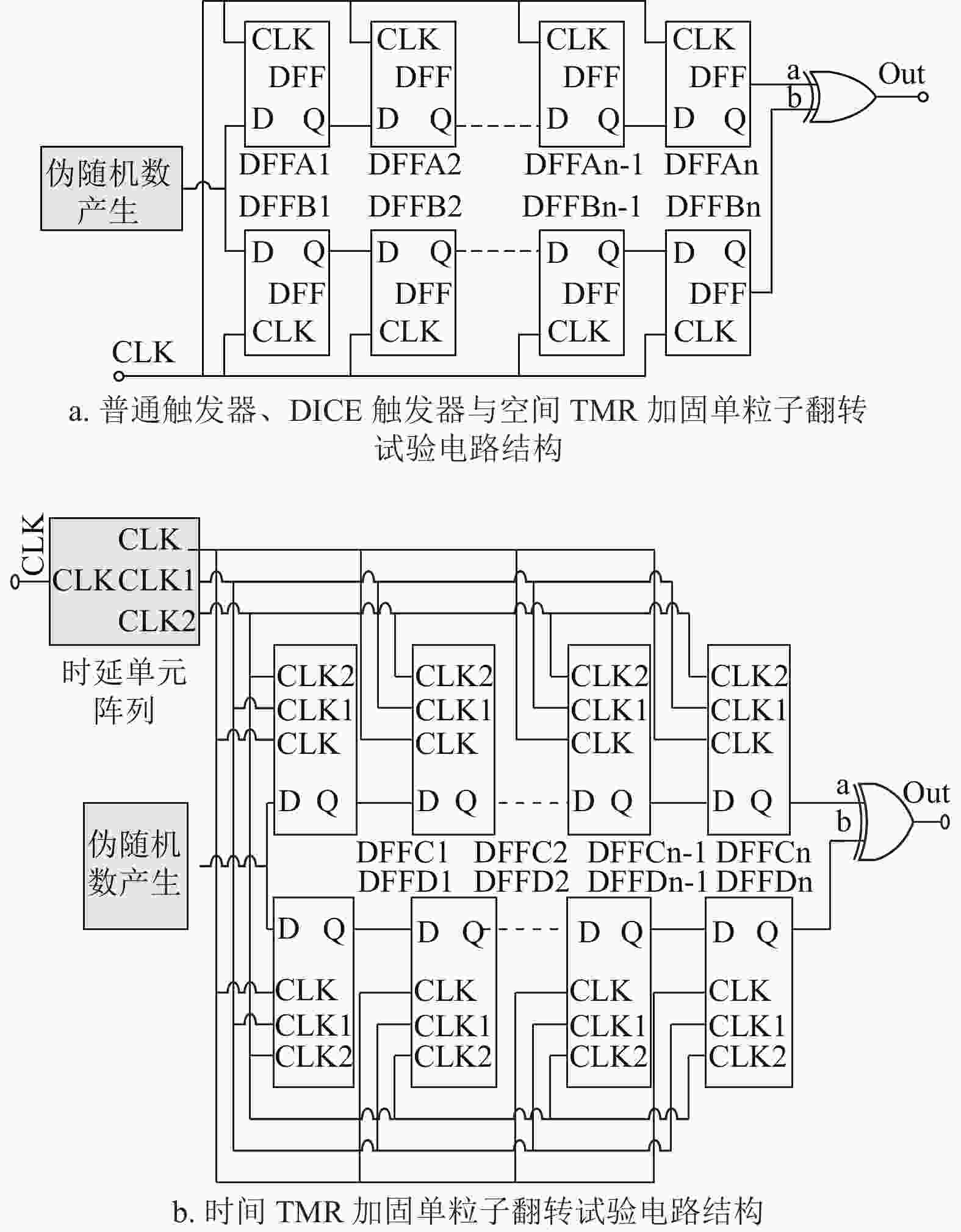

普通触发器、DICE触发器与空间TMR加固单粒子翻转试验电路结构如图5a所示,主要包括伪随机数产生、两个移位寄存器链和一个异或门;时间TMR加固单粒子翻转试验电路结构如图5b所示,主要包括时延单元阵列、伪随机数产生、两个移位寄存器链和一个异或门。

伪随机数产生电路作为激励信号发生器,给移位寄存器输入周期性变化的信号源“0010111”,工作频率为10 MHz。采用两路500级移位寄存器链,用于评估不同触发器结构的抗单粒子翻转性能。异或门比较两路移位寄存器链的输出信号,当移位寄存器链未发生单粒子翻转时,异或门输入端a和输入端b状态相同,输出低电平;当移位寄存器链发生单粒子翻转时,异或门输入端a和输入端b状态不同,输出高电平。通过对异或门输出状态的监控,可以获取不同触发器结构的单粒子翻转次数。时延单元阵列用于产生三路不同相位的时钟信号,分别控制时间TMR触发器的3个时钟信号。采用移位寄存器链评估触发器单粒子翻转效应的具体分析见文献[17]。

-

在实验室对上述触发器单粒子翻转试验电路进行评估,包括普通触发器(DFF)、DICE触发器(DICE-DFF)、相关敏感节点远离DICE触发器(FDICE-DFF)、空间三模触发器(TMR-DFF)、相差300 ps时间三模触发器(TTMR-DFF300)和相差600 ps时间三模触发器(TTMR-DFF600)6种被测触发器结构。共采用Ti(150 MeV)、Cu(200 MeV)、Br(218 MeV)、I(240 MeV)、Au(280 MeV)和Bi(923 MeV)这6种离子对被测电路进行轰击。6种离子的等效LET值分别是22.5 MeV·cm2/mg,32.5 MeV·cm2/mg,42 MeV·cm2/mg,63 MeV·cm2/mg,79.5 MeV·cm2/mg和99.8 MeV·cm2/mg;6种离子的入射深度分别是31 μm,30.2 μm,31.5 μm,27 μm,26.2 μm和53.7 μm。被测电路共3只,每只被测电路的各种入射离子的总注量都是107个离子。单粒子试验装置如图6所示。

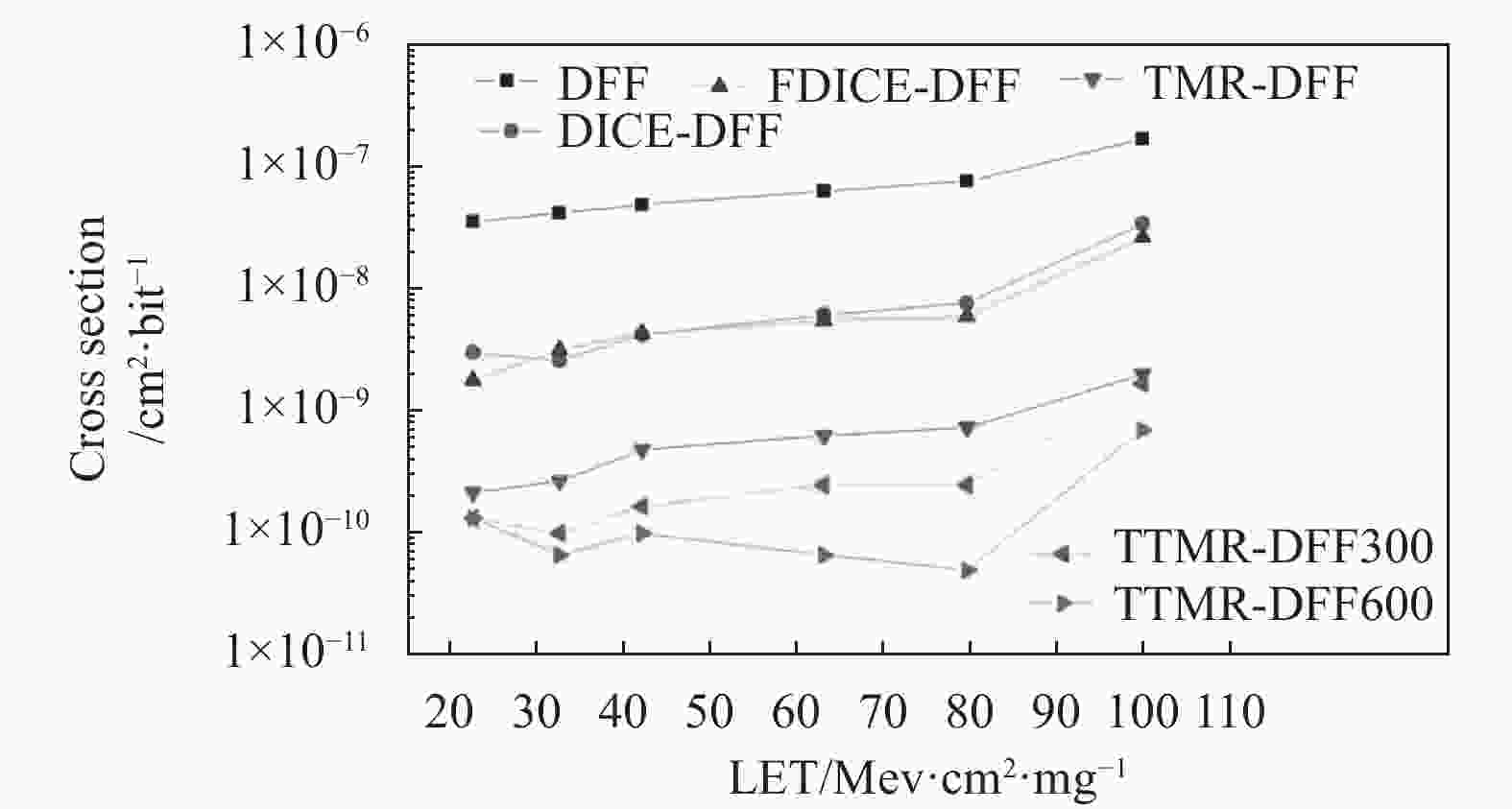

6种被测触发器结构的单粒子翻转截面如图7所示,试验结果表明随着入射离子LET的增加,6种被测触发器结构的单粒子翻转截面均呈上升趋势,尤其是LET值与入射深度均比较大的Bi离子,其单粒子翻转截面较Au离子提升2.2~14.0倍。主要是由于在高LET值与大入射深度的共同作用下,入射离子在衬底产生了大量的电子空穴对,单粒子效应影响半径远大于其他种类的离子,诱发的电荷共享效应更加明显,导致Bi离子的单粒子翻转截面增速猛然增加。

对于Ti、Cu、Br、I和Au这5种离子,DICE结构触发器单粒子翻转截面降低为普通触发器的6.2%~10.0%;对于Bi离子,DICE结构触发器单粒子翻转截面降低为普通触发器的20%。这是由于Ti、Cu、Br、I和Au这5种离子的入射深度相近,呈现的单粒子翻转截面降低程度相似。而Bi离子的入射深度相比5种离子增加了75%以上,单粒子翻转效应更加严重,导致加固措施的提升效果相比其他离子明显下降。同时,由于超深亚微米工艺单位面积器件密度的增加,入射离子的电荷共享效应更加明显,致使DICE结构触发器仍发生较多单粒子翻转,且DICE-DFF与FDICE-DFF的单粒子翻转截面接近。

TMR-DFF结构触发器单粒子翻转截面降低为普通触发器的0.6%~1.2%,下降约两个数量级。相比DICE结构触发器,三模冗余触发器结构抗单粒子翻转效果更加具有优势,单粒子翻转率约下降一个数量级。这主要是由于三模冗余结构的3个触发器具有更远的物理距离,电荷共享效应的影响进一步缩小。TMR-DFF结构触发器链产生的SEU主要是由于MAJ单元和缓冲器单元发生的单粒子瞬态脉冲,然后下一级触发器俘获从而形成单粒子翻转。

对于Ti、Cu、Br、I和Au这5种离子,TTMR-DFF300结构触发器单粒子翻转截面降低为普通触发器的0.2%~0.4%,相对于TMR-DFF结构触发器,单粒子翻转截面进一步降低。其主要原因是,MAJ单元和缓冲器单元发生的单粒子瞬态脉冲大部分被时间三模结构的滤波作用消除,但是对于单粒子瞬态脉冲大于300 ps的信号,仍可能被下级触发器俘获而形成单粒子翻转。对于Bi离子,TTMR-DFF300结构触发器单粒子翻转截面降低为普通触发器的1%,单粒子翻转截面相对于TMR-DFF结构触发器下降不明显,仅下降15.8%。其主要原因是由于Bi离子的高LET值与大入射深度特征,产生的大多数单粒子脉冲宽度均大于300 ps。

TTMR-DFF600结构触发器单粒子翻转截面降低为普通触发器的0.07%~0.4.0%。相对于TTMR-DFF300结构触发器,单粒子翻转截面进一步降低;尤其是对于Bi离子,其SEU概率仅为TTMR-DFF300结构触发器的41.6%。这是由于TTMR-DFF600结构触发器具有更好的单粒子脉冲滤波效果,但这需要牺牲时序性能为代价。TTMR-DFF600结构触发器产生的单粒子翻转主要包括3点原因:1)由于文中三模冗余(空间三模冗余和时间三模冗余)结构触发器,3个触发器物理距离较近,因此仍存在电荷共享效应引发两个触发器同时翻转的情况;2)个别离子在被测电路中产生了大于600 ps的瞬态脉冲,且被触发器俘获形成了SEU;3)触发器链经异或门比较和IO单元输出时,可能引入错误单粒子脉冲,并被测试系统错误记录。针对3个触发器物理距离较近的问题,可以在实际产品设计中,通过增大3个相关触发器的物理距离,进一步降低产品的单粒子翻转截面。

6种被测触发器结构地球同步轨道单粒子翻转概率如表1所示,DFF、DICE-DFF、FDICE-DFF、TMR-DFF、TTMR-DFF300和TTMR-DFF600这6种被测触发器结构GEO轨道单粒子翻转概率分别为7.72×10−9 error/(day·bit),7.70×10−11 error/(day·bit),5.56×10−11 error/(day·bit),3.13×10−13error/(day·bit),3.72×10−14 error/(day·bit),7.61×10−16 error/(day·bit)。对比可知,TTMR-DFF600结构具有最低的翻转概率,相比于普通触发器结构,其单粒子翻转概率降低了7个数量级。

表 1 6种被测触发器结构地球同步轨道单粒子翻转概率

被测触发器结构 单粒子翻转概率(GEO轨道)/error·(day·bit)−1 DFF 7.72×10−9 DICE-DFF 7.70×10−11 FDICE-DFF 5.56×10−11 TMR-DFF 3.13×10−13 TTMR-DFF300 3.72×10−14 TTMR-DFF600 7.61×10−16 -

6种被测触发器结构ck->q时延、面积、晶体管数量以及GEO轨道单粒子翻转概率对比情况如表2所示。普通触发器具有最快的速度、最小的面积和最少的晶体管个数,但是单粒子翻转性能最差。TTMR-DFF600触发器结构延时最大、面积最大且晶体管个数最多,分别是普通触发器的19.6倍、3.7倍和3.5倍,但是拥有最好的单粒子翻转性能,GEO同步轨道单粒子翻转概率相比普通触发器降低了7个数量级。因此,超大规模集成电路的辐射加固设计,需要针对其内部不同模块的性能采取合适的加固策略,针对时序余量较大的模块可以采用TTMR-DFF600触发器结构进行单粒子效应加固,对于时序余量紧张的模块应选择TMR-DFF结构触发器或DICE-DFF结构触发器,确保目标电路在满足其他指标要求的前提下,单粒子效应加固效果达到最优。

触发器单元单粒子辐射效应加固性能与速度、面积以及晶体管数量之间存在矛盾,需要针对集成电路的具体架构和应用情况进行折中选择,制定出最合适的单粒子翻转加固方案。

表 2 6种被测触发器结构性能对比表

被测触发器结构 ck->q时延/ps 面积/μm2 晶体管数量/个 单粒子翻转概率(GEO轨道)/error·(day·bit)−1 DFF 67 7.4×5 36 7.72×10−9 DICE-DFF 63 17.2×5 88 7.70×10−11 FDICE-DFF 65 17.4×5 88 5.56×10−11 TMR-DFF 103 27.2×5 126 3.13×10−13 TTMR-DFF300 705 27.2×5 126 3.72×10−14 TTMR-DFF600 1311 27.2×5 126 7.61×10−16 -

本文系统分析了DFF、DICE-DFF、FDICE-DFF、TMR-DFF、TTMR-DFF300和TTMR-DFF600这6种触发器单元的电路结构,采用移位寄存器链结构分别设计了相应的单粒子翻转效应验证电路,并基于65 nm工艺进行流片。利用Ti、Cu、Br、I、Au和Bi这6种离子分别对验证电路进行单粒子翻转试验,对试验结果进行深入分析,对比了6种触发器结构的翻转截面和GEO轨道翻转概率,TTMR-DFF600触发器单粒子翻转概率相比普通触发器降低了7个数量级,具有最好的单粒子翻转加固性能。最后,从速度、面积、晶体管数量以及抗SEU性能多角度对6种触发器单元进行全面分析,为后续超大规模集成电路抗SEU设计提供了一定的理论指导。

Analysis of SEU Radiation-Hardened Method About DICE-DFF and TMR-DFF Based on 65 nm Bulk CMOS Technology

-

摘要: 基于65 nm体硅CMOS工艺,采用移位寄存器链方式对普通触发器(DFF)、2种双互锁触发器(DICE-DFF,FDICE-DFF)、普通触发器空间三模冗余(TMR-DFF)和2种普通触发器时间三模冗余(TTMR-DFF300,TTMR-DFF600)这6种结构进行单粒子翻转(SEU)性能试验评估。利用Ti、Cu、Br、I、Au和Bi这6种离子对被测电路进行轰击,试验结果表明,普通触发器单粒子翻转截面最大,约为3.5×10−8~1.7×10−7 cm2/bit;时钟间隔时间600 ps的时间三模冗余结构触发器单粒子翻转截面最小,约为5×10−11~7×10−10 cm2/bit,仅为普通触发器的0.1%左右。同时,针对6种触发器单元,从速度、面积、晶体管数量以及抗SEU性能多方面进行综合分析,为后续超大规模集成电路抗SEU设计提供了一定的指导意义。Abstract: Based on 65 nm bulk CMOS technology, six kinds of DFFs including common DFF, DICE-DFF, FDICE-DFF, TMR-DFF, TTMR-DFF300 and TTMR-DFF600 were tested and analyzed by the shift register structure. Ti, Cu, Br, I, Au, Bi were used to impact the DFFs circuit. The results show common DFF has the worst cross section, which is 3.5×10−8 cm2/bit to 1.7×10−7 cm2/bit, while TTMR-DFF600 has the best cross sectionof 5×10-11 cm2/bit to 7×10-10 cm2/bit, which is only 0.1% of common DFF’s cross section. The six DFF structures were analyzed from speed, area, number of transistors and performance of SEU-hardened. Some meaningful suggestions have been provided for the design of SEU-hardened VLSI circuits.

-

Key words:

- cross section /

- DFF /

- DICE-DFF /

- SEU /

- TMR

-

表 1 6种被测触发器结构地球同步轨道单粒子翻转概率

被测触发器结构 单粒子翻转概率(GEO轨道)/error·(day·bit)−1 DFF 7.72×10−9 DICE-DFF 7.70×10−11 FDICE-DFF 5.56×10−11 TMR-DFF 3.13×10−13 TTMR-DFF300 3.72×10−14 TTMR-DFF600 7.61×10−16 表 2 6种被测触发器结构性能对比表

被测触发器结构 ck->q时延/ps 面积/μm2 晶体管数量/个 单粒子翻转概率(GEO轨道)/error·(day·bit)−1 DFF 67 7.4×5 36 7.72×10−9 DICE-DFF 63 17.2×5 88 7.70×10−11 FDICE-DFF 65 17.4×5 88 5.56×10−11 TMR-DFF 103 27.2×5 126 3.13×10−13 TTMR-DFF300 705 27.2×5 126 3.72×10−14 TTMR-DFF600 1311 27.2×5 126 7.61×10−16 -

[1] RATHORE P, NAKHATE S. Development of radiation hardened by design (RHBD) of NAND gate to mitigate the effects of single event transients (SET)[C]//2016 IEEE 1st International Conference on Power Electronics, Intelligent Control and Energy Systems (ICPEICES). Delhi: IEEE, 2016, [2] TRIVEDI R, DEVASHRAYEE N M, MEHTA U S, et al. Development of radiation hardened by design (RHBD) primitive gates using 0.18μm CMOS technology[C]//2015 19th International Symposium on VLSI Design and Test (VDAT). Ahmedabad: IEEE, 2015, [3] LI H S, WU L S, YANG B, et al. Analysis of single event transient pulse-width in 65nm commercial radiation-hardened logic cell[J]. Journal of Semiconductors, 2017, 38(8): 100-104. [4] CAO T J, WU L S, LI H S, et al. A new SET-tolerant radiation-hardened DLL design with lock detector[J]. Microelectronics and Computer, 2017, 34(9): 77-81. [5] JIANG S, LIU S B, GUO C, et al. The application of TMR on the high performance and anti radiation DSP[J]. Microelectronics and Computer, 2019, 36(3): 58-60. [6] LOVELESS T D, REISING D R, CANCELLERI J C, et al. Analysis of single-event transient SETs using machine learning ML and ionizing radiation effects spectroscopy IRES[J]. IEEE Transactions on Nuclear Science, 2021, 68(8): 1600-1606. doi: 10.1109/TNS.2021.3050879 [7] ANTON B, MAXIM G, ARTUR G. Design-stage hardening of 65-nm CMOS standard cells against multiple events[J]. IEEE Transactions on Nuclear Science, 2021, 68(8): 1712-1717. doi: 10.1109/TNS.2021.3077443 [8] LEONARDO B, ALEXANDRA Z, CRISTINA M, et al. Impact of process variability and single event transient on FinFET technology[C]//IFIP/IEEE 27th International Conference on Very Large Scale Integration. [S.l.]: IEEE, 2019: 249-250. [9] FUMA M, MITSUNORI E, YUTO T, et al. Intrinsic vulnerability to soft errors and a mitigation technique by layout optimization on DICE flip flops in a 65-nm bulk process[J]. IEEE Transactions on Nuclear Science, 2021, 68(8): 1727-1734. doi: 10.1109/TNS.2021.3075176 [10] ANDREW T, DENNIS B, GYORGY V, et al. Impact of surface recombination on single-event charge collection in an SOI technology[J]. IEEE Transactions on Nuclear Science, 2021, 68(3): 305-311. doi: 10.1109/TNS.2021.3056898 [11] ZHAO Y F, WANG L, YUE S G, et al. SEU and SET of 65 bulk CMOS flip-flops and their implications for RHBD[J]. IEEE Transactions on Nuclear Science, 2015, 62(6): 2666-2672. doi: 10.1109/TNS.2015.2490552 [12] WANG H B, LI Y Q, CHEN L, et al. An SEU-tolerant DICE latch design with feedback transistors[J]. IEEE Transactions on Nuclear Science, 2015, 62(2): 548-554. doi: 10.1109/TNS.2015.2399019 [13] WHITAKER S, CANARIS J, LIU K. SEU hardened memory cells for a CCSDS reed-solomon encoder[J]. IEEE Transactions on Nuclear Science, 1991, 38(6): 1471-1477. doi: 10.1109/23.124134 [14] EVANS A, COSTENARO E, BRAMNIK A. Flip-flop SEU reduction through minimization of the temporal vulnerability factor (TVF)[C]//2015 IEEE 21st International on-Line Testing Symposium (IOLTS). Halkidiki: IEEE, 2015, [15] AKIFUMI M, HIROYUKI S, TSUKASA E, et al. DICE-based flip-flop with SET pulse discriminator on a 90 nm bulk CMOS process[J]. IEEE Transactions on Nuclear Science, 2010, 57(6): 3602-3608. [16] HU K Y, HU H S, LIU X M. The application of TMR on the high performance and anti radiation DSP[J]. Microelectronics and Computer, 2019, 36(3): 58-60. [17] LI H S, JIANG Y H, YANG B, et al. SEE evaluation method for DFF cell based CMOS/SOI technology[J]. Transactions of Beijing Institute of Technology, 2018, 38(1): 63-67. -

ISSN

ISSN

下载:

下载: