-

现代信息化战争中,战场边界空前扩展,渗透于陆海空天网电磁等六大领域,同时态势瞬息万变,争夺信息权的战法和范式推陈出新,未来新一代卫星载荷需要同时具备搜索、发现、识别、对抗与打击等多种不同的功能,并在轨自主运行与处理,以满足战场态势瞬息万变、任务不断变化的短时间应对需求[1-4]。

传统卫星载荷系统,天线、射频通道和信号及数据处理设备研制采取定制化方式,将载荷按照功能分类划分,依据任务需求,分解细化天线分系统增益、波束覆盖、等效全向辐射功率(effective isotropic radiated power, EIRP)、射频通道频率、带宽和增益、信号及数据处理逻辑计算、存储和I/O资源等指标,对各分机进行独立供电以及控制。各分系统间没有形成标准化接口,硬件设备层与软件功能层紧密耦合,几乎无法实现在轨功能重构,系统研制周期和成本居高不下,通过地面上注指令完成同种功能波形的简单配置,灵活性自主性不足,系统不具备开放性。通过硬件资源的堆砌实现功能的叠加,对于卫星资源造成极大的浪费,且导致严重的电磁互扰效益,同时使得卫星成本和尺寸、重量和功耗比(cost-size, weight and power, C-SWaP)性能下降,难以实现在轨升级和设计复用[5-8]。

面向多功能、软件化、可定制和可更新的卫星装备需求,需要改变目前卫星载荷通信、遥感、导航增强、电子侦察及干扰等装备独立设计的理念,使卫星同时具备以上能力,基于孔径一体、通道一体、处理一体设计理念,实现多种功能电磁信号统一发射、接收及处理。本文采用基于紧耦合机理和电磁超材料加载的超宽带阵列天线,实现超宽带宽角扫描,极化模式可随任务需要重构,完成对电磁空间多种功能信号的统一发射接收。基于射频全链路可重构架构及硅基微机电(micro-electro mechanical system, MEMS)和射频硅通孔(RF through Silicon Via, RF TSV)工艺,通过多层硅转接板堆叠将射频前端和射频通道进行三维异构集成,实现工作频率、带宽、增益和输出功率灵活重构和最高工作频率对应半波长尺度内的高密度三维集成[9],最终实现综合射频系统全谱覆盖、可重构复用、信号数字化和微系统化。本文采用实时总线与实时中间件,进行异构式射频资源抽象,实现孔径和射频资源的统一管理、调度和控制。基于三维异构集成技术,实现多核中央处理器CPU、多核数字信号处理器DSP和高性能现场可编程门阵列FPGA异构高效的芯片及软件化综合处理微系统,完成多种功能波形的统一部署和能力重构。

-

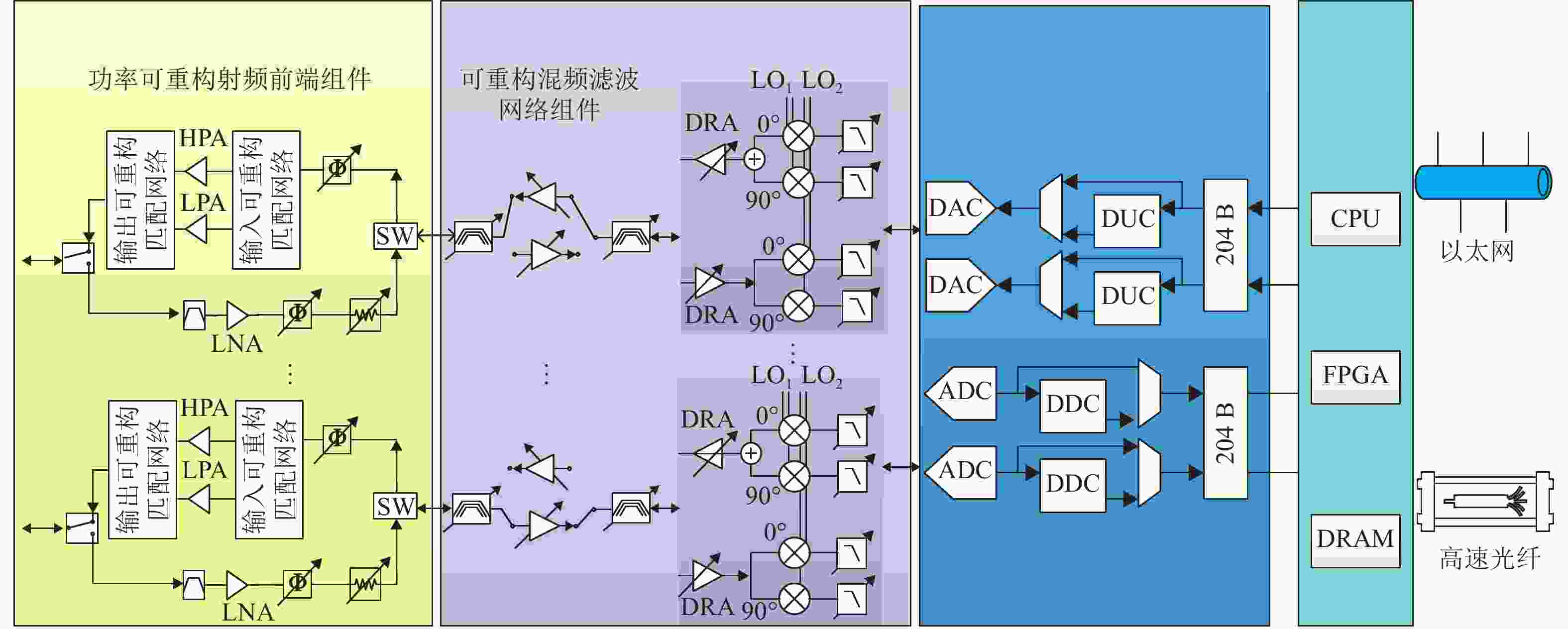

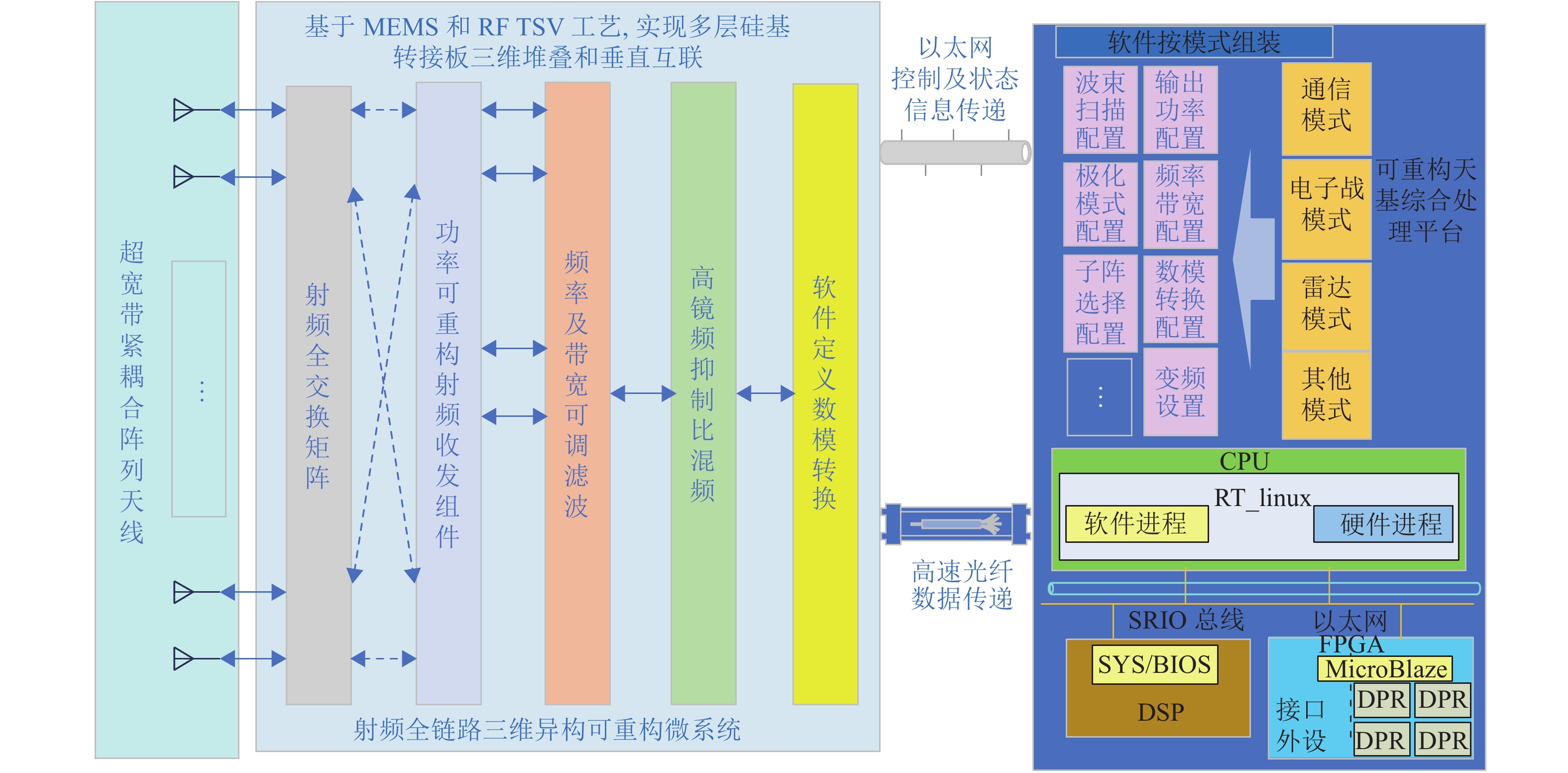

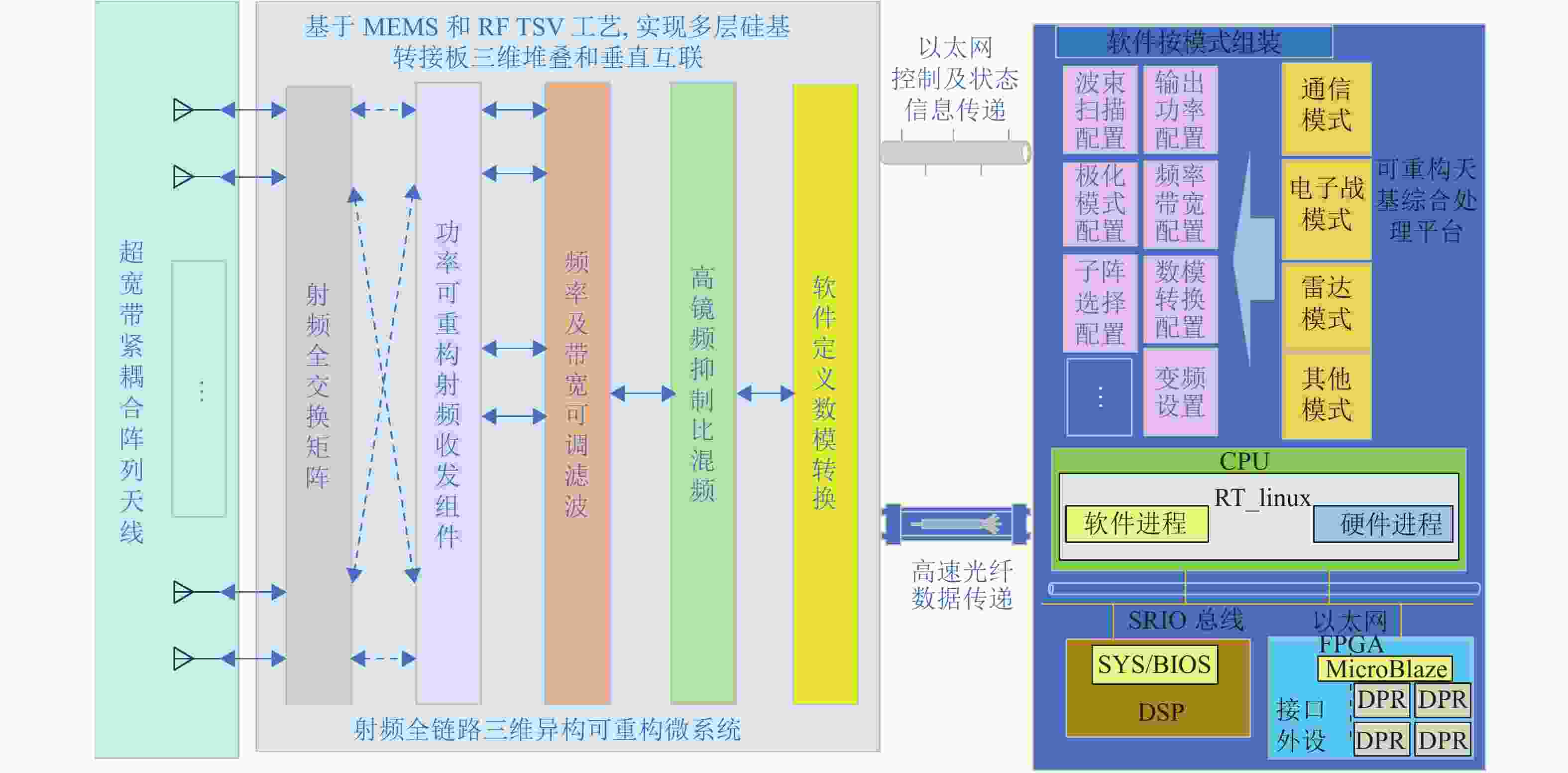

多功能可重构电磁信号发射接收及处理架构如图1所示,主要包括超宽带宽角扫描极化可重构阵面、三维异构宽带可重构射频微系统和可重构天基综合处理平台。超宽带宽角扫描极化可重构阵面,基于紧耦合机理和电磁超材料加载,采用多层PCB板加工技术实现,用于电磁空间多种功能信号统一发射接收,可实现跨3~10倍频程、扫描角度≥±60°,结合极化合成电路,极化方式可配置成水平、垂直、左旋和右旋模式,剖面高度小于等于高频波长,可满足导通探干侦多种功能对于共享孔径轻量化、一体化、低剖面和易共形的需求。

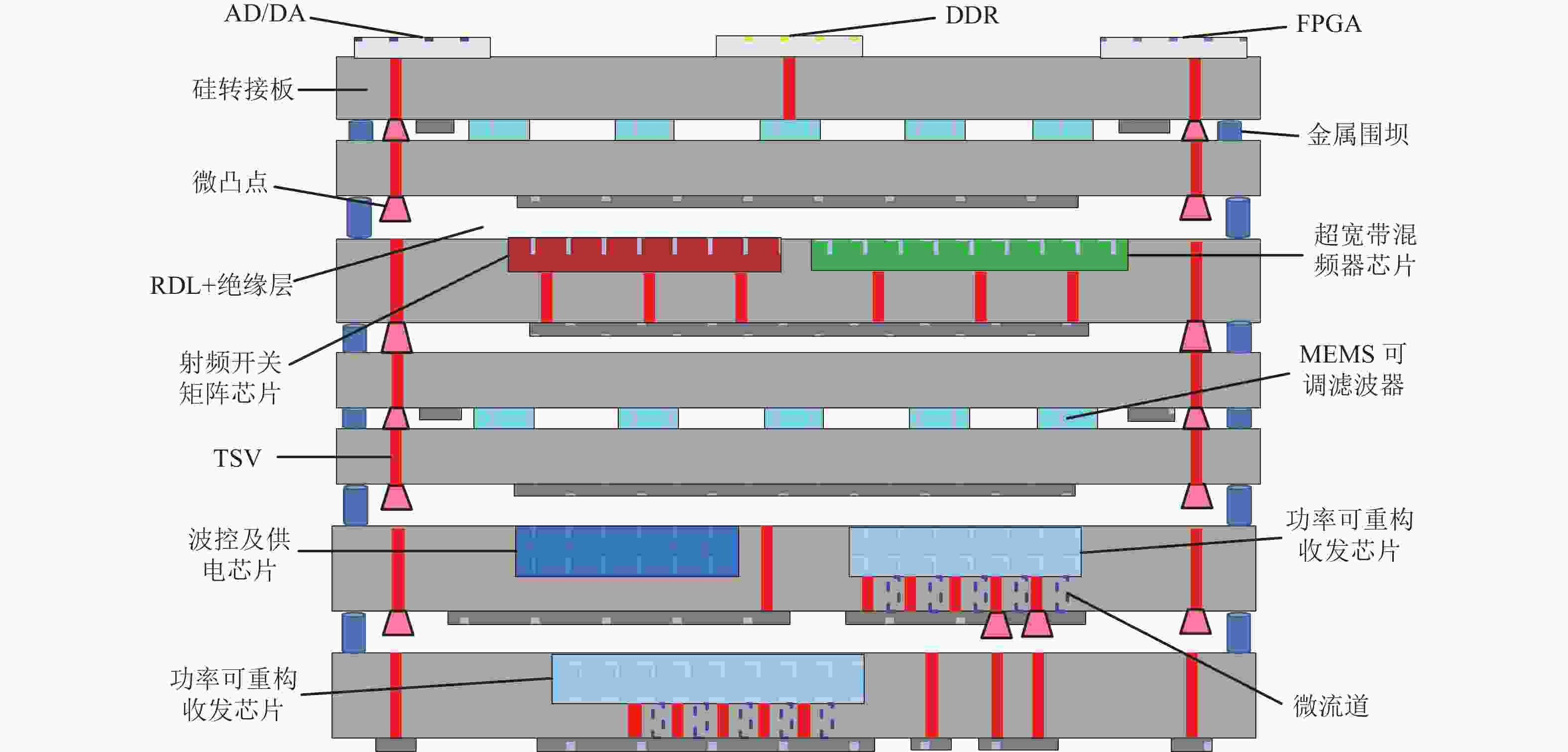

三维异构宽带可重构射频微系统,主要包括射频全交换矩阵层、宽带功率可重构T/R微组件层、频率及带宽可调滤波层、超宽带高镜频抑制比混频层、软件定义数模转换层、电源管理和射频芯片控制层。综合采用RF TSV、集成无源器件(integrated passive device, IPD)、重布线(redistribution layer, RDL)和微凸点(microbump bonding)互联等技术,实现硅基三维堆叠集成封装。硅转接板既为封装提供一定强度的结构,又可在上面加工腔体、过孔和走线,并集成电阻、电容、电感和滤波器等无源器件。通过倒装焊或导电胶粘接埋置多种参数可配置的异质异构射频芯片,通过绝缘层和重布线层实现同层信号互联,通过RF TSV实现多层硅转接板间信号的垂直互联传输。根据任务能力需求,对综合孔径和射频资源在时域、频域、空域、极化和能量域进行统一调度和管理,通过射频资源的智能访问控制,实现射频模式的动态调整,以及射频系统频谱、时间、空间、能量等资源利用最优化。

可重构天基综合处理微系统综合采用硅转接板、3D-SiP和3D-TSV技术,将CPU、DSP、FPGA各个处理核心和DDR内存资源封装成单芯片系统。以FPGA局部动态可重构为基础,采用硬件进程、硬件上下文和软硬件进程混合调度的理念,实现功能可动态重构、资源可高度复用、任务可同时服务。实现了多核、异构、并行、高效的芯片级软件化微系统综合处理,统一部署通信、遥感、导航增强、电子侦察及干扰功能波形,实现异构处理资源的虚拟、灵活调度和管理。

-

通过故意增强传统超宽带天线阵的不利设计因素互耦,研究微型化馈电巴伦设计、轻量化低剖面阵元结构设计、电阻性电抗性超材料加载方法,最终突破天线阵低剖面轻量化阵元结构设计、极化控制和超宽带宽角扫描等关键技术,设计出超宽带宽角扫描、低剖面极化可重构的阵列天线[8-13]。

超宽带紧耦合单元馈电结构采用指数渐变微带巴伦进行阻抗匹配,通过偶极子臂重叠部分增强了电容耦合,巴伦和偶极子臂进行了一体集成,在偶极子单元上方合适的位置加入两层特定厚度的介质层用作阻抗匹配层,降低天线单元到自由空间的阻抗失配。这里主要限制带宽的因素是地板的高度,单元工作频段的上限频率会受到地板高度的限制,因此需要仔细调节地板高度使天线工作带宽最大化,进而实现超宽工作频带与宽角扫描。对于极化可重构要求,采用将两个重叠偶极子天线单元正交放置的方案,分别实现垂直和水平极化。

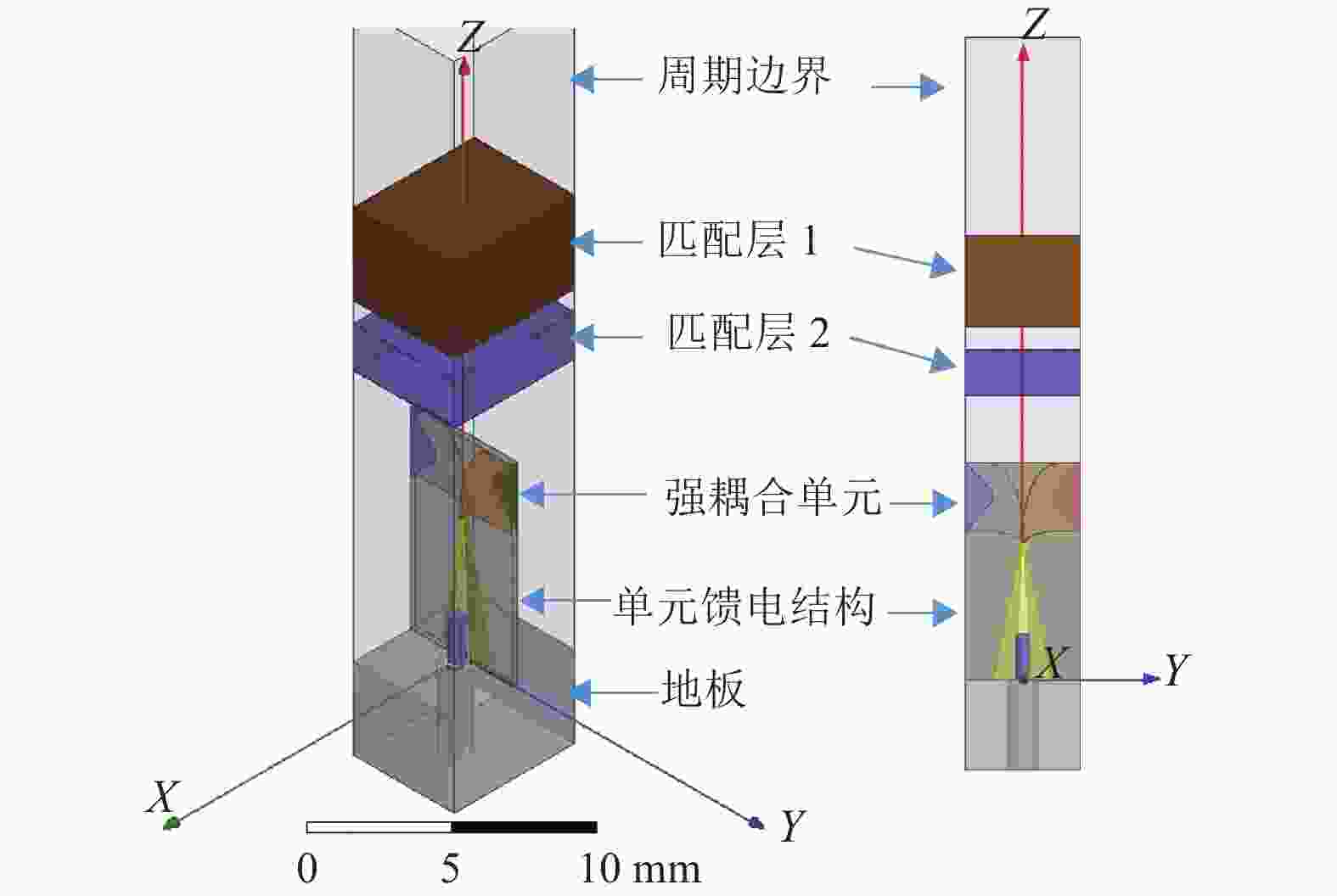

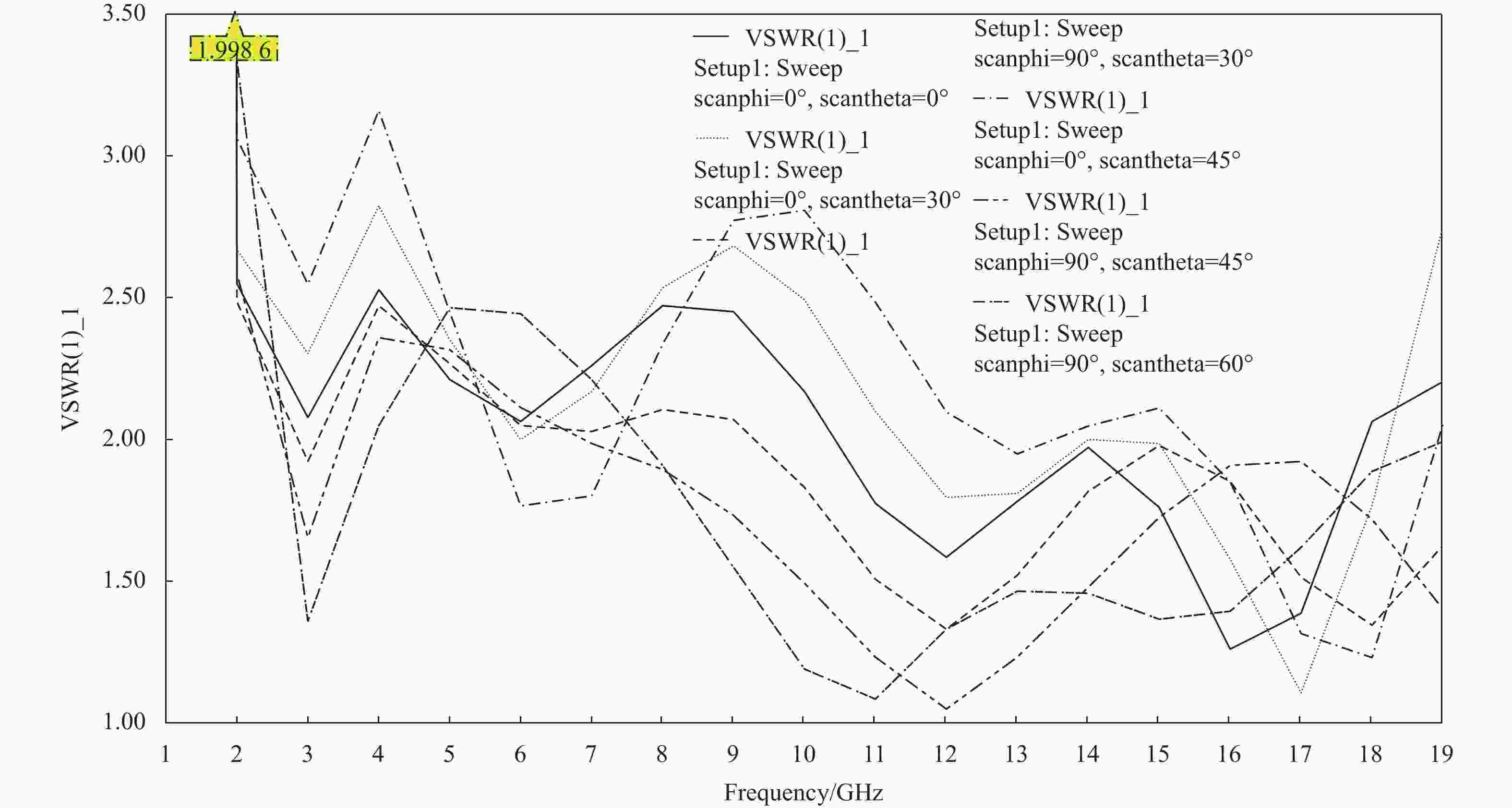

如图2所示,超宽带紧耦合单元采用了正方形栅格,栅格大小为d=5 mm,该参数取决于高频波束扫描时会不会出现栅瓣,在两个匹配层中间以及匹配层2与偶极子之间的空气层,可以用泡沫填充。在单元末端添加电容耦合的印刷偶极子结构,并通过对基本偶极子末端进行切割,最终形成叠层偶极子模型,单元剖面高度约为16.5 mm。如图3所示,在2~18 GHz工作频段,在E面波束扫描到±60°时,单元有源驻波比低于2.5,因此该单元的宽角扫描效果良好。

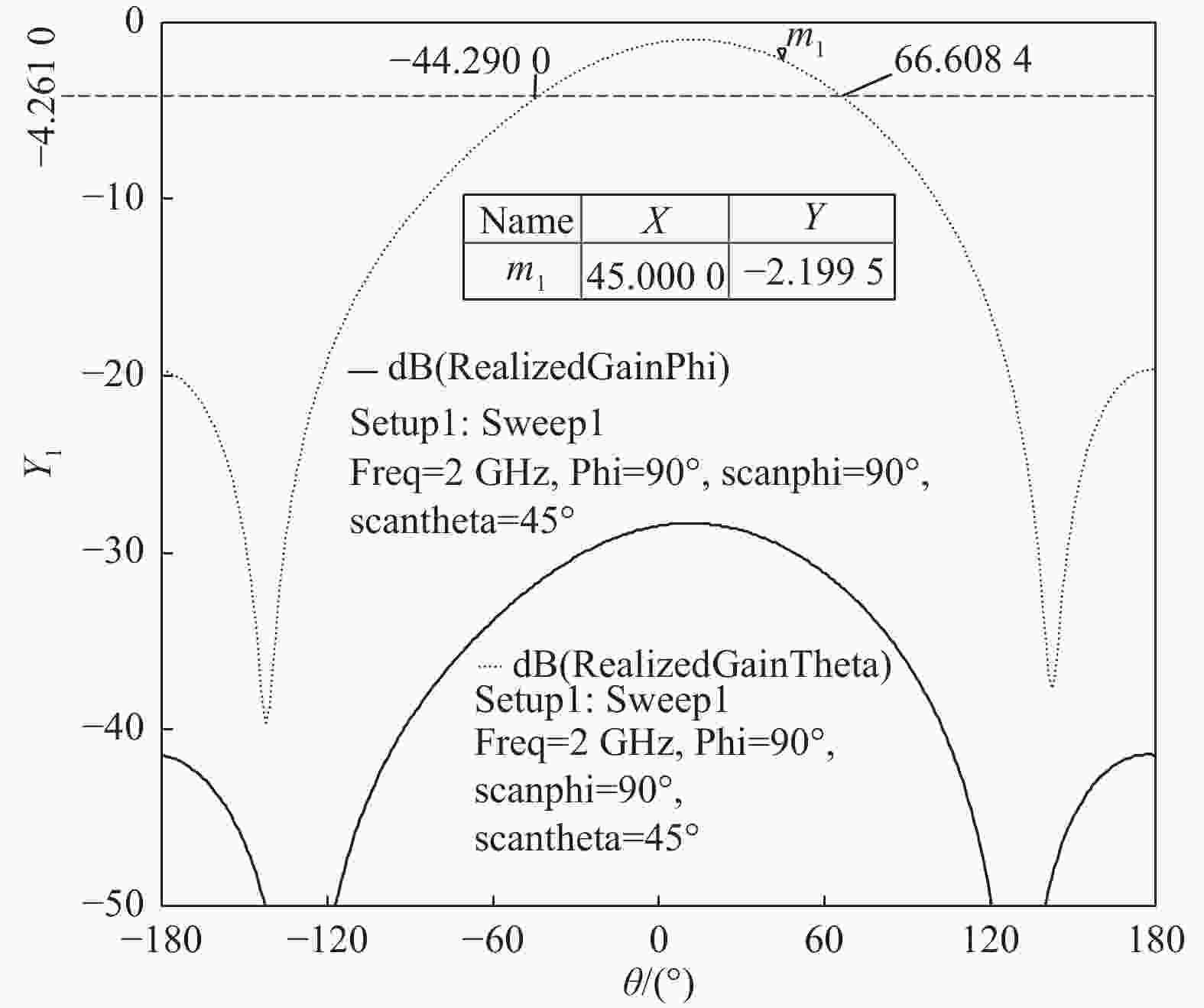

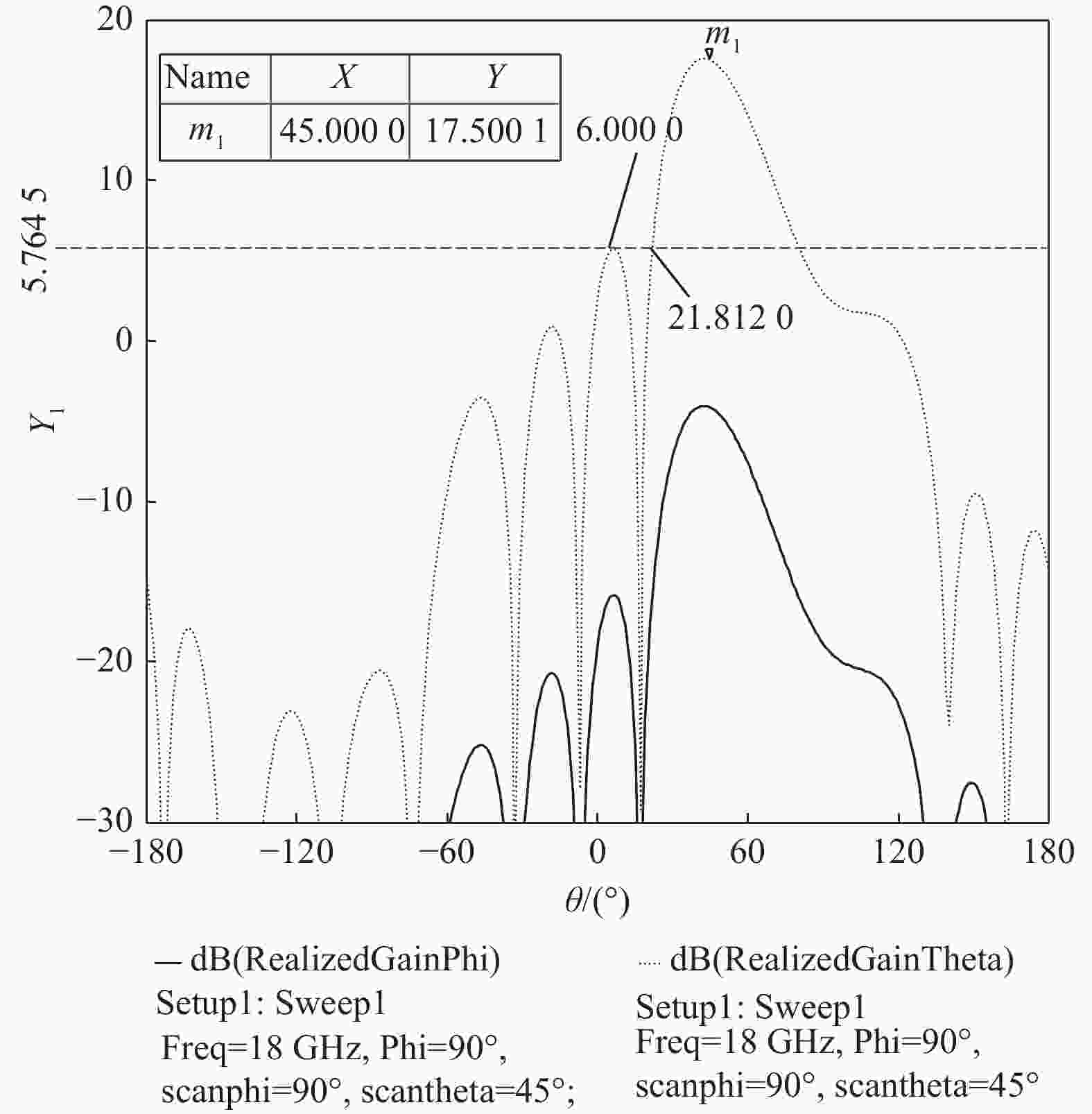

如图4和图5所示可以看出,在2 GHz、18 GHz情况下,8×8阵列E面45°扫描时,波束形状正常,指向正常,增益水平正常,副瓣水平正常,表明紧耦合超宽带一体化阵列在超宽带宽角扫描时具有优良的性能。

-

如图6所示,基于射频全链路可重构架构,通过多层硅转接板堆叠进行三维异构集成,既能够实现超宽工作频段覆盖,又能实现工作频率、带宽、增益和输出功率的灵活重构,内建射频直采数模转换器,实现射频到数字信号的转换,为后端信号和数据处理提供更高的灵活度。三维异构集成指在硅基板上,通过综合采用TSV、RDL、Micro-Bump等手段,实现异质(不同材料)异构(不同工艺节点)化合物半导体、CMOS、MEMS芯片等的高密度封装集成,充分发挥材料、器件与结构的优势,使射频电路最优化获得高频、高速、宽带、低功耗、小体积和高性能等特性,推进射频前端高度集成化、多功能化和智能化。

功率可重构射频前端组件由超宽带高效率功率可重构功放芯片和超宽带低功耗高线性低噪放芯片组成,实现发射功率重构。可重构混频滤波网络组件用于实现射频信号频率、带宽和增益重构。软件定义数模转换芯片实现中频或基带信号的数模转换、采样率变换和数字滤波能力。通过射频全交换矩阵连接实现功率可重构射频前端收发组件、频率及带宽可调滤波、高镜频抑制比混频和软件定义数模转换之间的灵活连接,并基于多层硅转接板进行三维异构片式集成[14-26]。三维异构宽带可重构综合射频微系统和后端可重构天基综合处理平台之间通过高速光纤进行信号和数据交互,通过千兆以太网进行控制和状态监测信息的传递。

三维异构宽带可重构综合射频微系统结构截面图如图7所示,将多种参数可配置的异质异构射频芯片,采用水平错位排布,内嵌于多层电阻率在1000 Ohm·cm以上的高阻硅转接板,单层硅转接板的厚度为100~300 μm,相邻两层硅转接板的基板之间间隔缝隙为10~20 μm。硅转接板通过设于其表面的绝缘层和重布线层实现同层信号的水平互联,通过穿透基板的RF TSV实现异层信号的垂直互联,最底部的基板设有接地散热硅通孔以实现接地和散热,各层硅转接板四周通过设置金属围坝实现气密[25]。

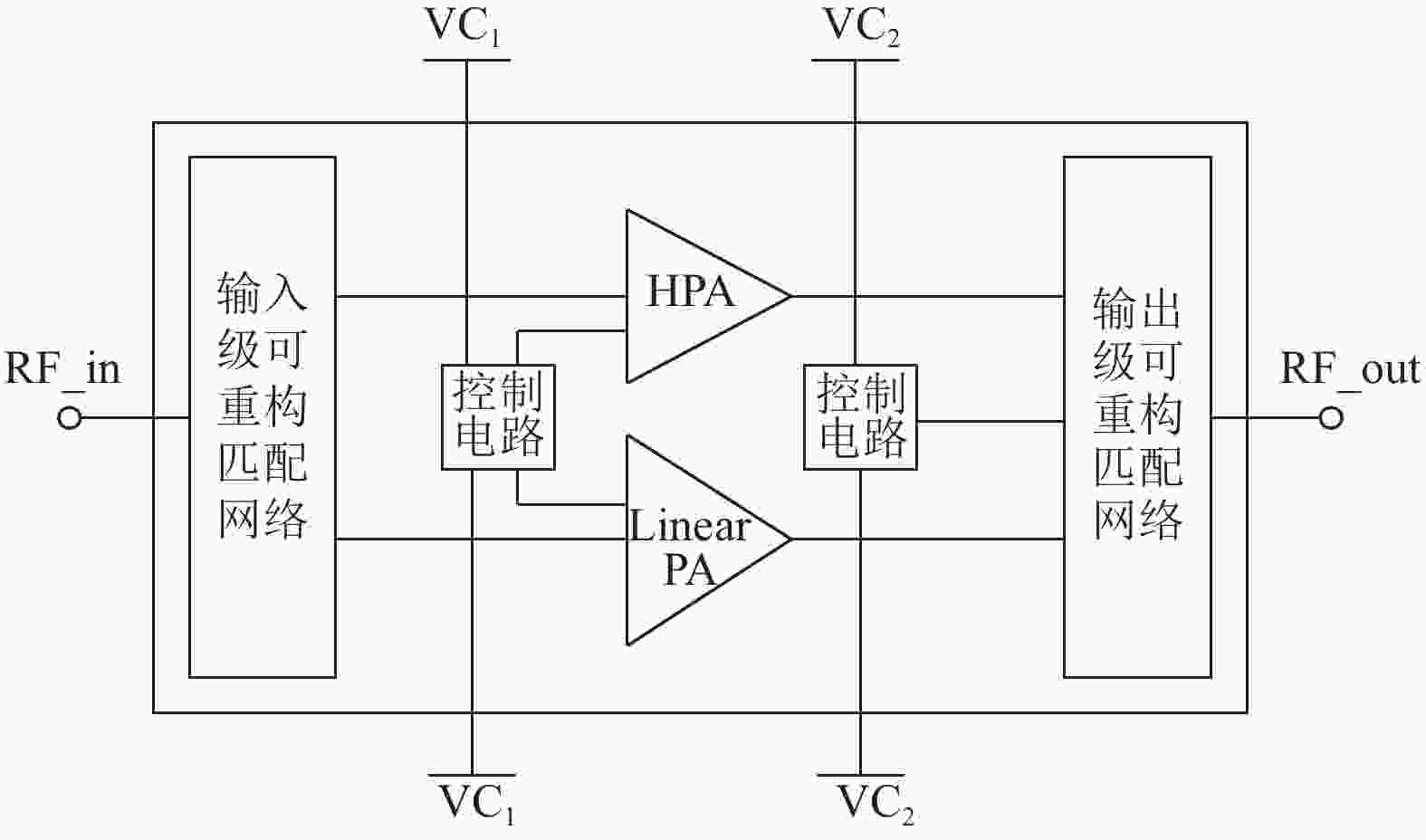

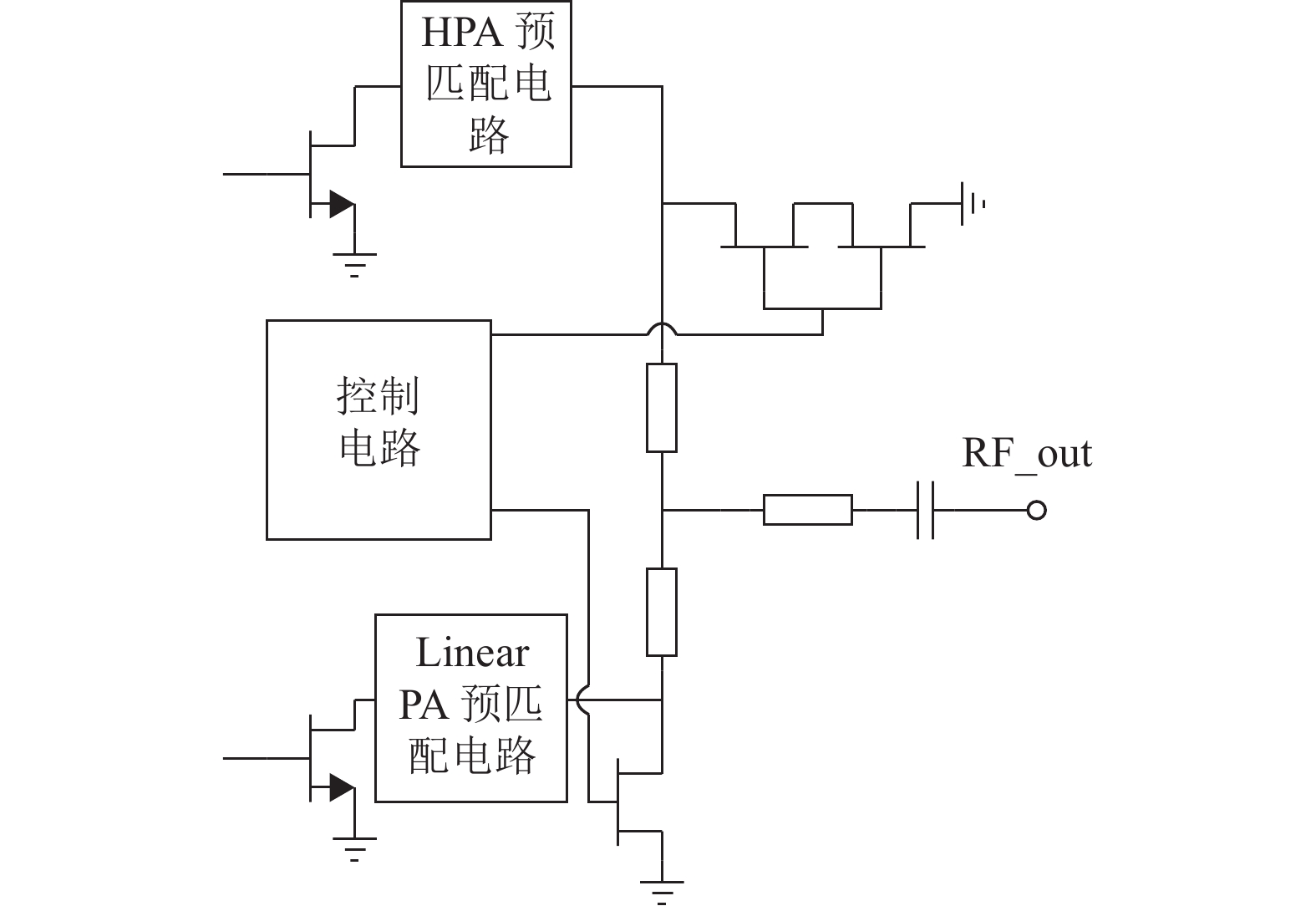

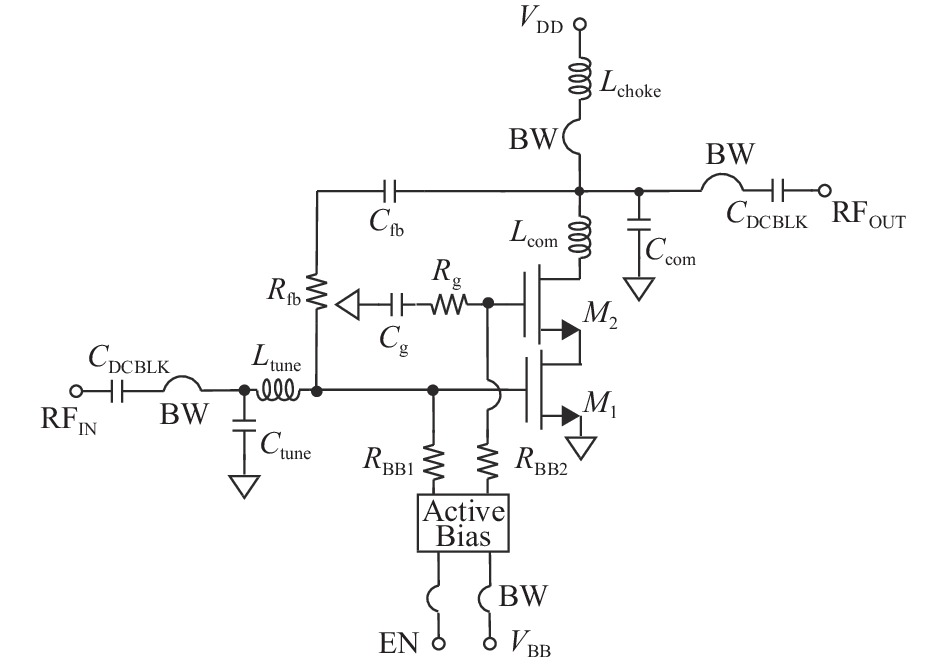

功率可重构放大器总体结构示意图如图8所示,针对超宽带高效率功率可重构功放芯片设计,采用基于可重构输入输出匹配网络技术,将一款宽带线性放大器(linear-power amplifier, LPA)和窄带宽高功放大器(high-power amplifier, HPA)集成在单片上,在输入和输出匹配网络上采用电调谐可重构设计,通过片内集成的控制电路进行切换,从而实现输出功率的灵活重构;通过对器件的二三次谐波进行负载阻抗的相位牵引仿真,找出针对特定频率的最佳相位点,抑制高次谐波信号,减小谐波功率损耗,从而较大幅度的提高功放效率。

可重构输出匹配网络拓扑结构示意图如图9所示。为了实现在控制电路信号下的放大器切换,需要对整体功放的输出级进行可重构设计。采用可重构器件直接作为放大器输出级匹配电路的一部分进行设计,在实现阻抗变换网络的基础上能够利用其中的可重构单元对匹配网络状态进行控制,从而切换输出支路,实现可重构效果。

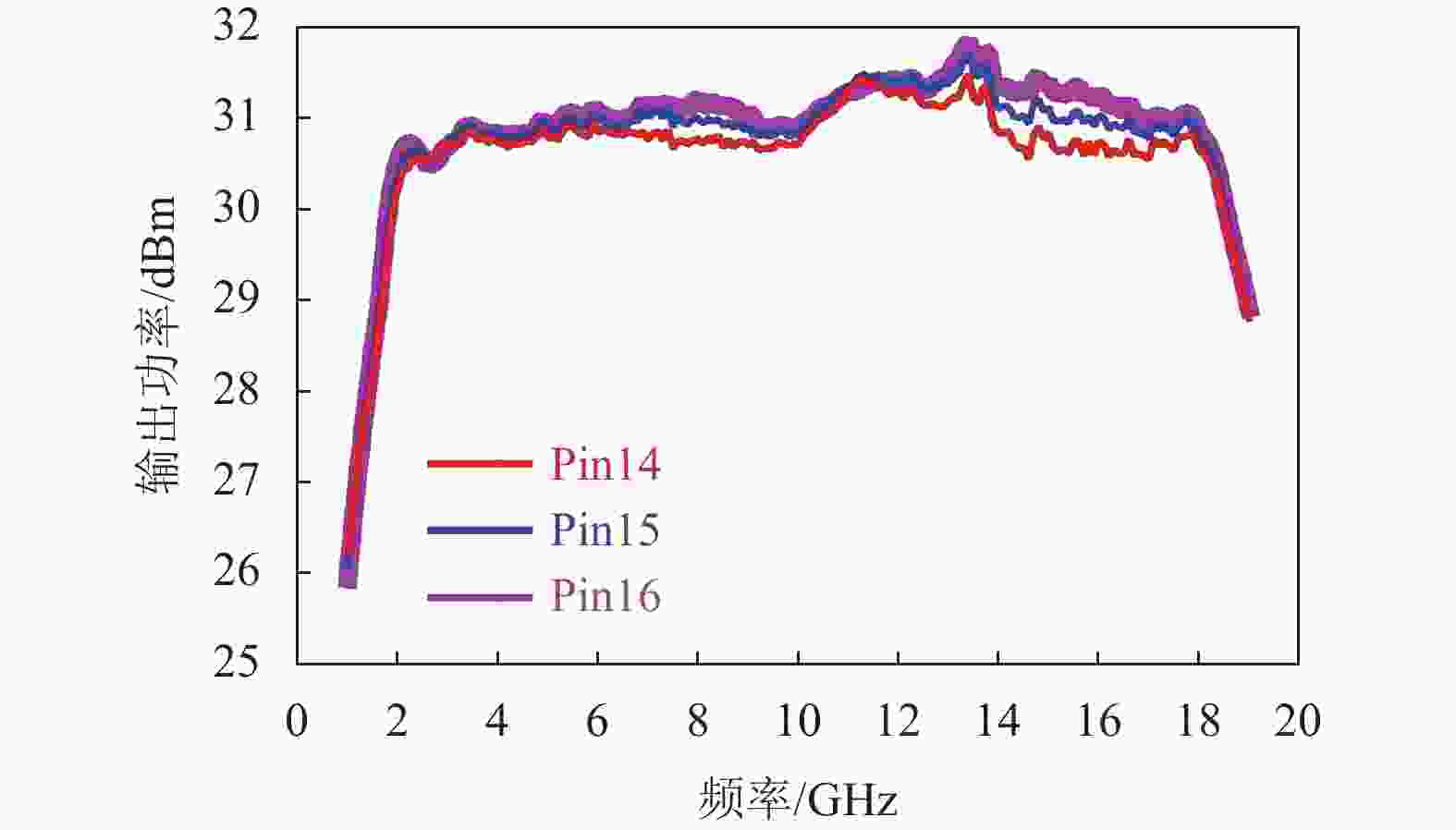

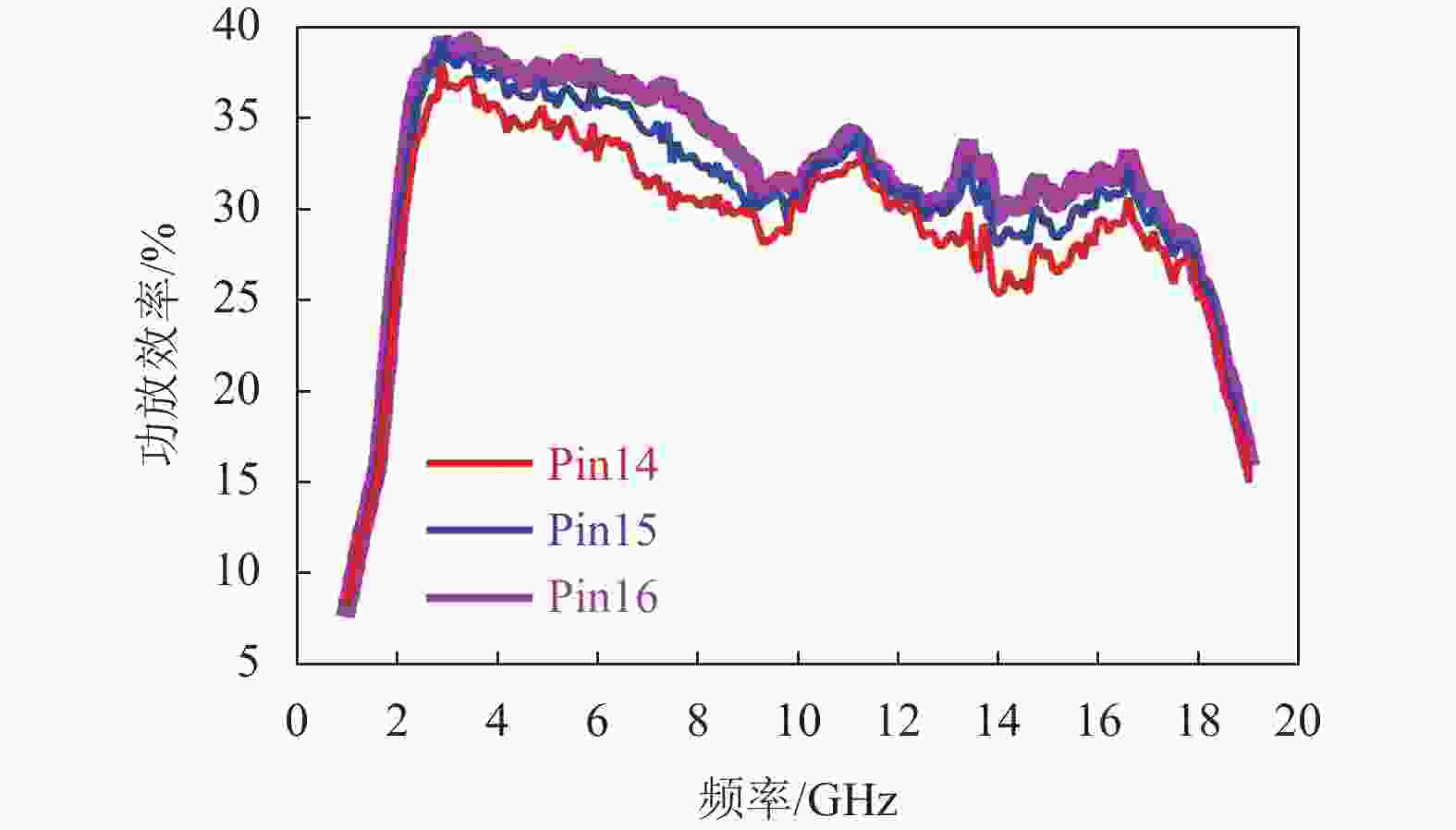

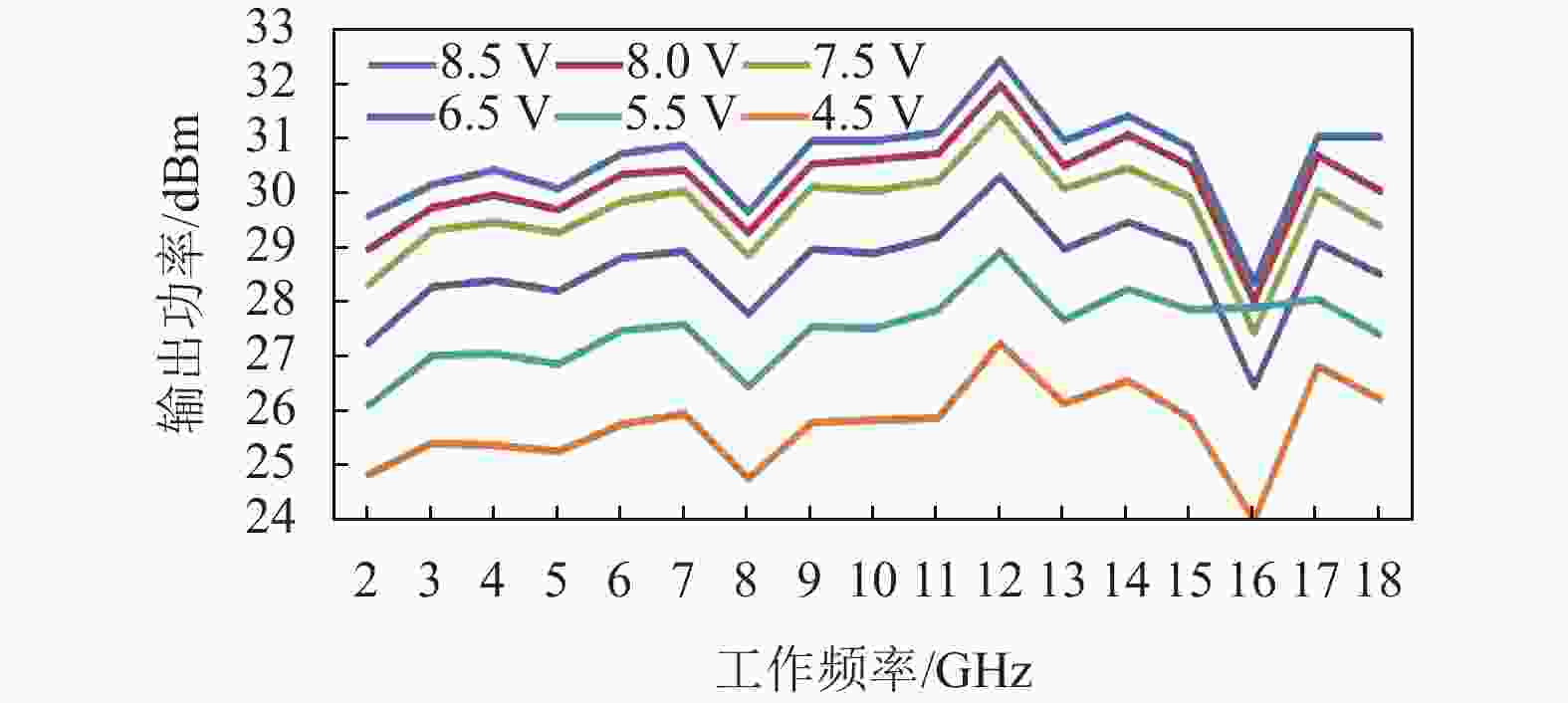

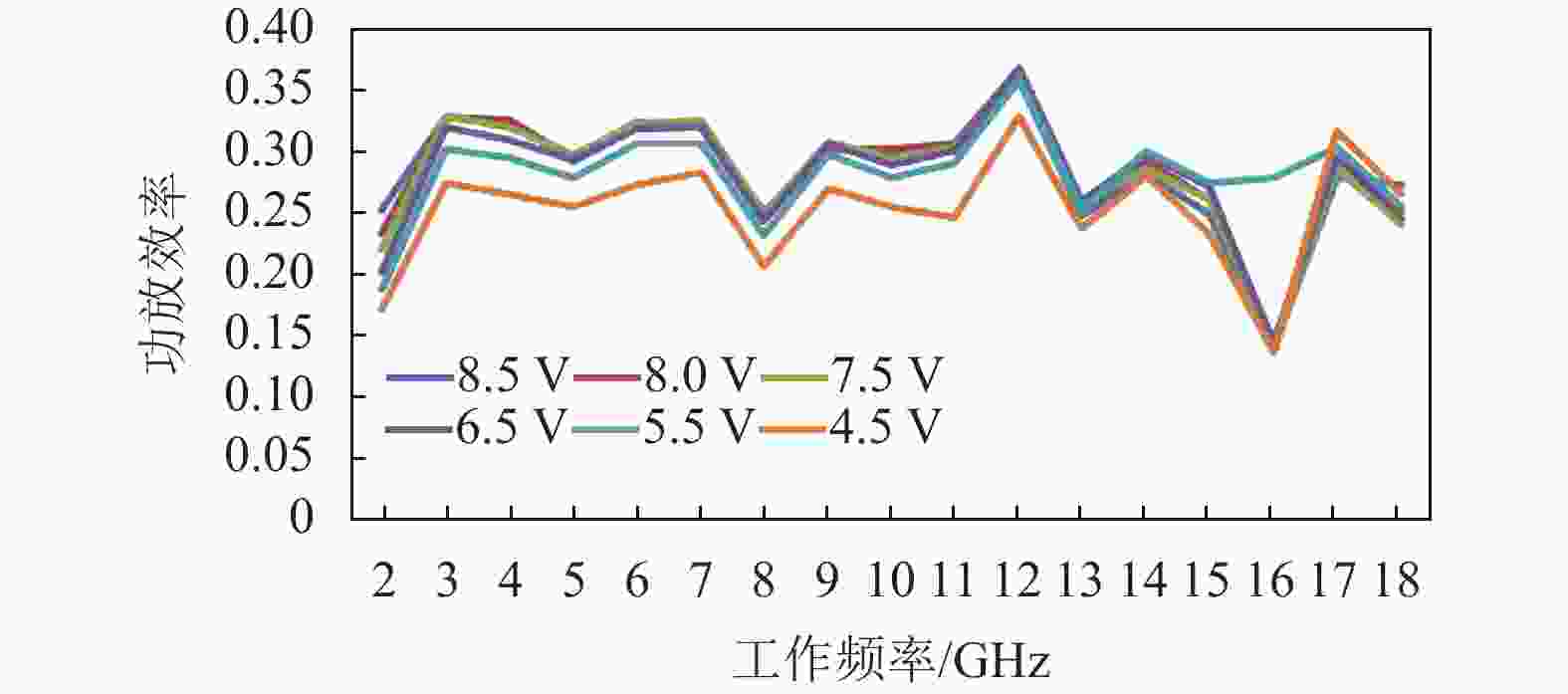

如图10~图13所示,设计的超宽带高效率功率可重构功放芯片在2~18 GHz频带内,输出功率≥29.8 dBm,平均效率≥25%,Pin14、Pin15和Pin16分别指代功放源极输入激励功率分别为14、15、16 dBm。当漏极电压从8.5 V调整至4.5 V时,功放芯片的输出功率将从31 dBm回退至25 dBm,功率重构能力大于等于6 dB,且平均效率均高于25%。

针对超宽带低功耗高线性低噪放芯片设计,采用基于带栅极补偿负载网络的改进型Cascode电路架构,如图14所示,极大提升了低噪放芯片的工作带宽。同时采用有源偏置技术,如图15所示,通过环路补偿实现芯片静态工作点的动态平衡,显著提升了低噪放芯片在三温条件下的增益稳定性。

设计的超宽带低功耗高线性低噪放芯片在2~18 GHz频带内,回波损耗优于10 dB,IIP3为7 dBm,当供电电压为12 V时,接收增益大于19 dB,噪声系数小于2 dB。

通过级联两个以上频率可重构滤波器单元,并在相邻的频率可重构滤波器单元之间引入增益可重构放大器单元,解决了多级滤波器单元的级间匹配问题;通过改变两个频率可重构滤波器单元的谐振频率,可以大幅度地改变中心频率和带宽;通过改变中间级可重构放大器单元的增益,可以大幅度地改变增益,实现了频率、带宽和增益都可重构的带通滤波器。滤波器单元设置有频率可重构的谐振器及用于改变滤波器单元频率的MEMS开关,通过一体化加工设于两层硅转接板之间,形成夹层结构[16-19]。

-

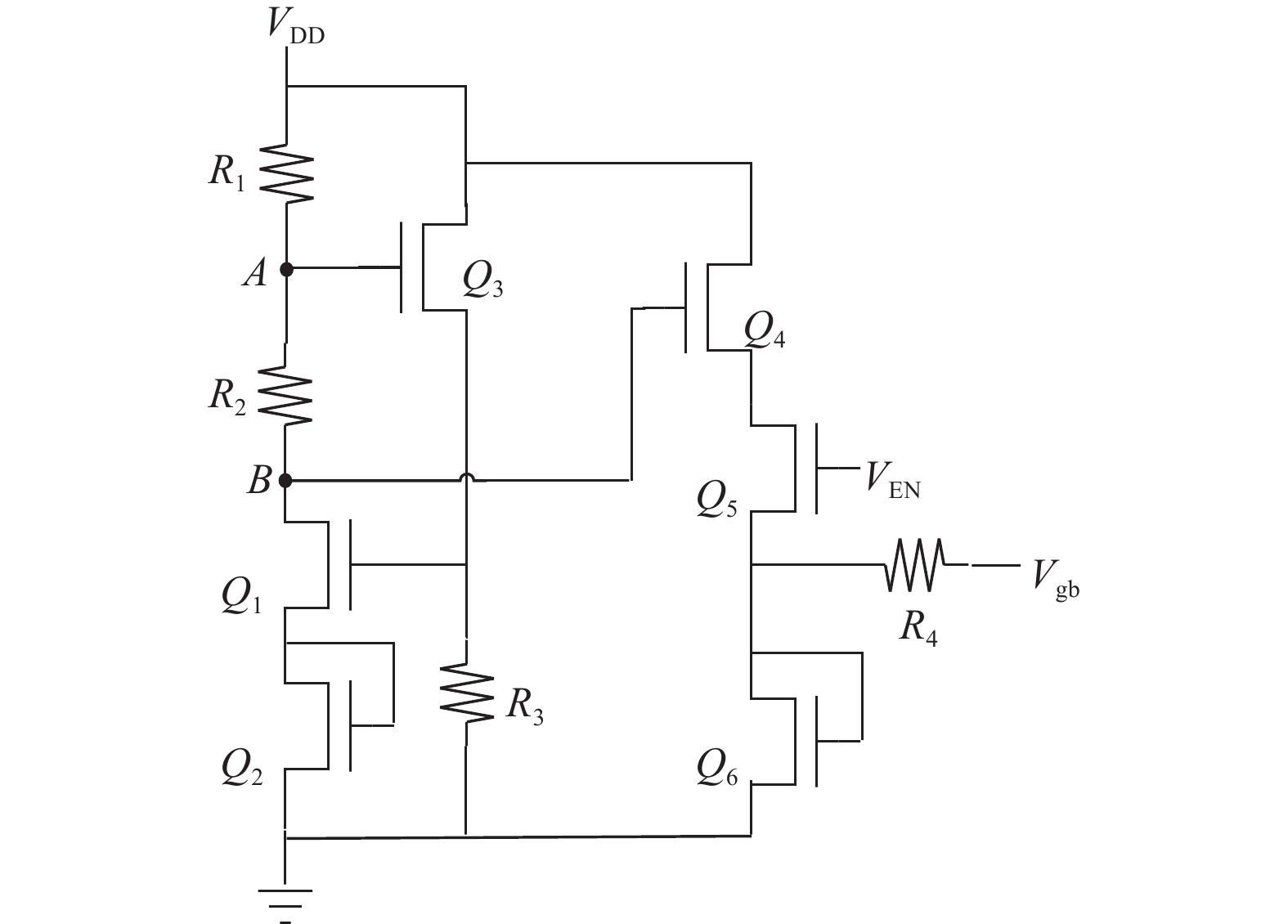

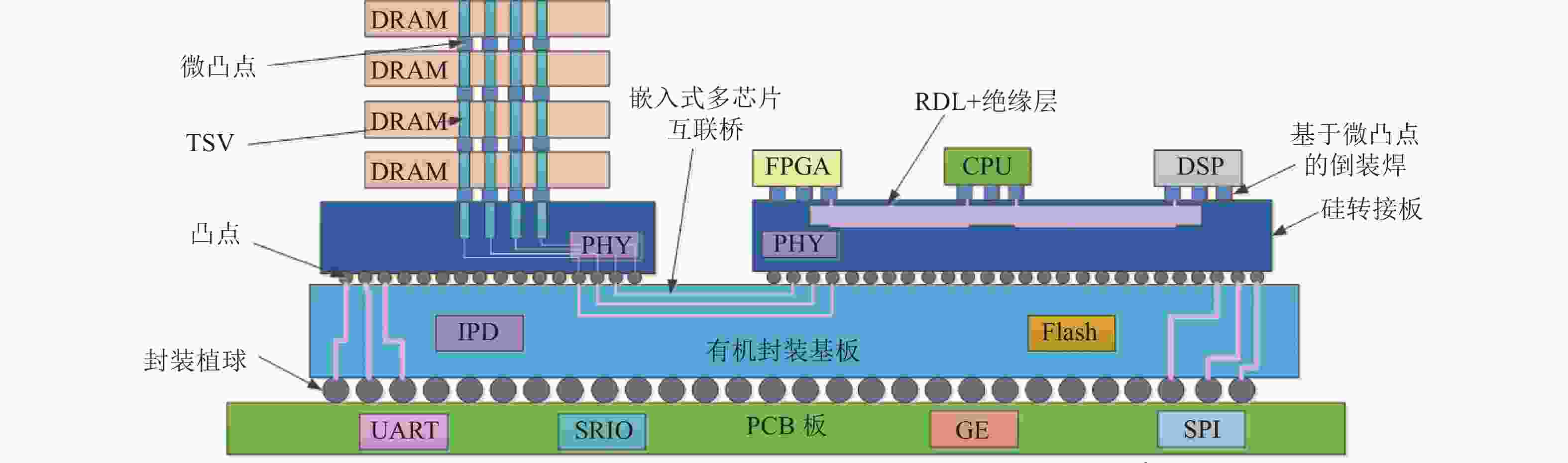

为满足雷达、通信、电子战及导航增强等功能波形组件的动态部署与灵活重构,构建性能可弹性扩展、资源可高度复用、任务可同时服务的混合异构处理微系统,综合采用硅转接板、3D-SiP和3D-TSV技术将CPU、DSP、FPGA各个处理核心和DDR内存资源封装成单芯片系统。芯片级的系统集成使体积减小、功耗降低,可靠性、稳定性和抗干扰性大为提高,信号的传输延迟降低,使得系统可运行在更高的频率上,最大限度实现多核、异构、并行、高效的执行效率,实现小型化、轻量化、高度集成化和高可靠性,有效提升软件化多功能综合处理器的C-SWaP性能[26-37]。

混合异构可重构天基综合处理微系统架构图如图16所示,采用有机基板和硅基板混合集成,在有机基板上埋嵌硅基板实现高密度互连。多片DRAM基础颗粒芯片进行三维堆叠,通过3D-TSV技术实现垂直互联,形成HBM存储器,大幅提高内存容量和数据传输速率。CPU、DSP和FPGA等异构计算芯片,通过微凸点以倒装焊的方式堆叠集成在硅转接板上,通过绝缘层和RDL层实现同层信号水平互联,嵌入式多芯片互联桥与HBM存储器等进行高密度的水平互连。Flash及IPD等元器件集成到有机基板,PCB板上集成对内对外GE、SPI和UART等接口芯片[30-31, 34]。

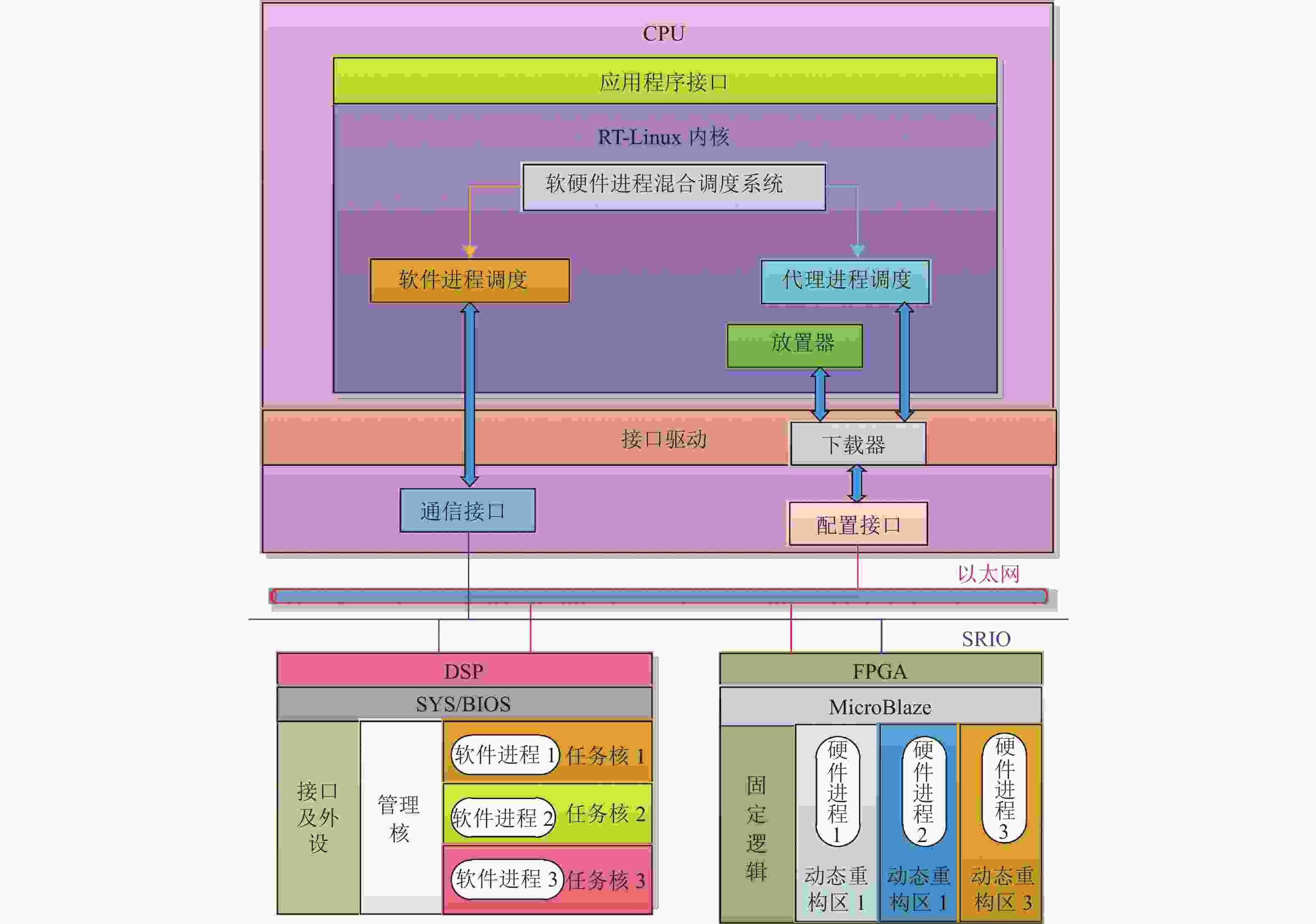

混合异构处理资源动态管理与调度架构图如图17所示,同时基于FPGA局部动态可重构技术,通过将FPGA可重构区域划分成几个硬件任务槽,可以在运行的过程中动态改变逻辑功能,使得多个不同的任务可在同一时间的不同区域运行。仿照操作系统中针对资源的管理方法,提出了以硬件任务的方式在混合系统中管理可重配置资源的思路,把硬件任务抽象为硬件进程的方式,其含有硬件任务运行的相关信息,当硬件任务被抢占时,重构模块将当前正在运行的模块内部寄存器的值保存在代理进程,当模块通过局部重构重新运行时,能够恢复到之前被打断的运行状态(即恢复模块内部各个寄存器的值)。操作系统通过调度硬件进程,可间接地调度硬件任务,实现混合异构多处理器资源的管理、调度和分配。硬件进程不在CPU上运行而是在可重配置硬件结构上运行,对于上层应用来说,通过这种方式能够屏蔽软件进程和硬件进程的实现差异,为应用程序提供统一的编程接口[38-44]。

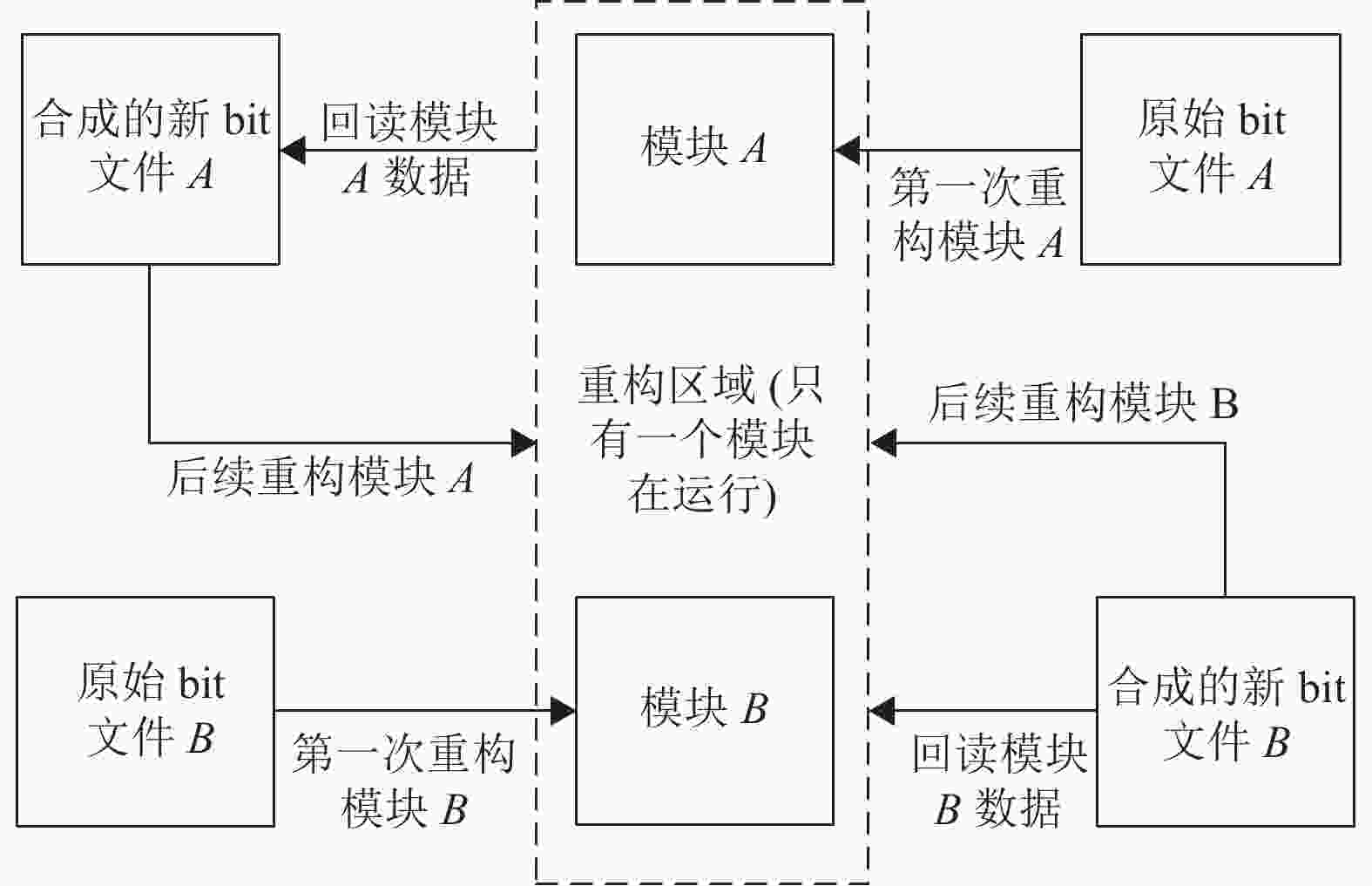

FPGA硬件上下文寄存器备份与恢复如图18所示,FPGA是基于SRAM的查找表技术,其中的逻辑功能和布线资源的状态都依赖于配置电路中SRAM存储的值,通过该数值来构造逻辑运算的真值表或充当线路的开关和连接点。当硬件任务A执行时,遭遇硬件任务B抢占执行,可将FPGA当前SRAM中存储的数值保存至CPU或DDR中,当硬件任务B执行完毕时,回读寄存器状态值,采用合成算法合成新的bit文件利用ICAP接口下载到FPGA重构区中,硬件任务A将在被中断执行的地方继续执行。

-

本文提出了导航增强、通信、雷达探测、电子侦察和干扰综合多功能载荷系统孔径一体、通道一体、处理一体的系统架构和关键技术。基于超宽带紧耦合理念,设计了2~18 GHz超宽带收发、±60°超宽角扫描、剖面高度仅为高频波长且支持极化模式可切换的综合孔径。基于射频全链路可重构架构和硅基MEMS和RF TSV工艺,采用宽带可重构匹配和电调谐可重构设计,实现了2~18 GHz超宽带收发、大动态、高线性度、频率、带宽和功率等射频参数可在线重构的三维异构综合射频微系统。综合采用硅转接板、3D-SiP和3D-TSV技术,将CPU、DSP、FPGA各个处理核心和DDR内存资源封装成单芯片系统,以FPGA局部动态可重构为基础,采用硬件上下文、硬件进程和软硬件进程混合调度的理念,实现了多核、异构、并行、高效的芯片级软件化综合处理微系统,支持雷达、通信、电子战及导航增强等功能波形组件的动态部署与重构,灵活调度和管理计算及存储资源。为未来分布式多域智能网联电子系统的软件化、虚拟化和智能化奠定技术基础。

Multifunctional Reconfigurable Electromagnetic Signal Transmitting Receiving and Processing Technology

-

摘要: 针对导航增强、通信、雷达探测、电子侦察和干扰综合多功能一体化载荷系统对硬件通用化、功能软件化和资源虚拟化的需求,实现最大限度资源复用与共享,提出了低剖面、超宽带宽角扫描、极化可重构的综合孔径技术,基于射频全链路可重构架构和三维异构集成的综合射频微系统技术;基于硬件进程实现超异构计算资源灵活调度和动态管理技术。该文提出的综合多功能一体化电磁信号发射接收处理架构和关键技术,为未来分布式多域智能网联电子系统的软件化、虚拟化和智能化提供技术基础。Abstract: In radar communication and electronic warfare, multifunctional integrated load system needs hardware generalization, functions based on software and resource virtualization, so as to realize resource reuse and sharing to the maximum extent. In this paper, we design a polar-reconfigurable antenna array with low profile, ultra-wideband and wide angle scanning, a comprehensive RF microsystem with reconfigurable RF performances, and a high-performance heterogeneous computing platform for flexible resource scheduling and dynamic management. The multifunctional integrated architecture and its key technologies proposed in this paper lay the technical foundation for the function based on software, virtualization and intelligentization of distributed multi-domain intelligent networked electronic systems in the future.

-

[1] 赵军锁, 吴凤鸽, 刘光明. 软件定义卫星技术发展与展望[J]. 卫星与网络, 2017(12): 46-50. doi: 10.3969/j.issn.1672-965X.2017.12.010 ZHAO J S, WU F G, LIU G M. Development and prospect of software defined satellite[J]. Satellite and Network, 2017(12): 46-50. doi: 10.3969/j.issn.1672-965X.2017.12.010 [2] 周渊, 张询颖, 智永锋, 等. 软件定义卫星有效载荷技术研究[J]. 西北工业大学学报, 2020, 38(S1): 96-101. ZHOU Y, ZHANG X Y, ZHI Y F, et a1. Research on software defined satellite payload technology[J]. Journal of Northwestern Polytechnical, 2020, 38(S1): 96-101. [3] 吴启星. 软件定义卫星研究现状与技术发展展望[J]. 中国电子科学研究院学报, 2021, 16(4): 333-337. doi: 10.3969/j.issn.1673-5692.2021.04.005 WU Q X. State of the art and development analysis of software defined satellites[J]. Journal of China Academy of Electronics and Information Technology, 2021, 16(4): 333-337. doi: 10.3969/j.issn.1673-5692.2021.04.005 [4] 徐帆江, 周鑫, 赵军锁, 等. 软件定义卫星技术概念及发展[EB/OL]. [2021-12-01]. https://doi.org/10.13700/j.bh.1001-5965.2021.0562. XU F J, ZHOU X, ZHAO J S, et al. Rethinking of software-defined satellite technology[EB/OL]. [2021-12-01]. https://doi.org/10.13700/j.bh.1001-5965.2021.0562. [5] 朱伟强, 王克让, 许华健, 等. 多功能综合一体化技术发展综述[J]. 航天电子对抗, 2020, 36(3): 1-10. ZHU W Q, WANG K R, XU H J, et al. Development of multifunctional integration technology[J]. Aerospace Electronic Warfare, 2020, 36(3): 1-10. [6] 梁兴东, 李强, 王杰, 等. 雷达通信一体化技术研究综述[J]. 信号处理, 2020, 36(10): 1615-1627. LIANG X D, LI Q, WANG J, et al. Joint wireless communication and radar sensing: Review and future prospects[J]. Journal of Signal Processing, 2020, 36(10): 1615-1627. [7] 马丁友, 刘祥, 黄天耀, 等. 雷达通信一体化: 共用波形设计和性能边界[J]. 雷达学报, 2022, 11(2): 198-212. doi: 10.12000/JR21146 MA D Y, LIU X, HUANG T Y, et al. Joint radar and communications: Design of shared waveforms and performance bounds[J]. Journal of Radars, 2022, 11(2): 198-212. doi: 10.12000/JR21146 [8] 邢卓异, 朱舜杰, 黄晓峰, 等. 软件定义航天器系统架构设计[J]. 航天器工程, 2021, 30(5): 1-8. doi: 10.3969/j.issn.1673-8748.2021.05.001 XING Z Y, ZHU S J, HUANG X F, et al. Design on software-defined spacecraft system architecture[J]. Spacecraft Engineering, 2021, 30(5): 1-8. doi: 10.3969/j.issn.1673-8748.2021.05.001 [9] HOLLAND S S, VOUVAKIS M N. The planar ultra-wideband modular antenna (PUMA) array[J]. IEEE Transactions on Antennas and Propagation, 2012, 60(1): 130-140. doi: 10.1109/TAP.2011.2167916 [10] ZHONG J, JOHNSON A, ALWAN E A, et al. Dual-Linear polarized phased array with 9: 1 bandwidth and 60° scanning off broadside[J]. IEEE Transactions on Antennas and Propagation, 2019, 67(3): 1996-2001. doi: 10.1109/TAP.2019.2891607 [11] ZHANG H Y, YANG S W, XIAO S W, et al. Low-Profile, lightweight, ultra-wideband tightly coupled dipole arrays loaded with split rings[J]. IEEE Transactions on Antennas and Propagation, 2019, 67(6): 4257-4262. doi: 10.1109/TAP.2019.2905960 [12] XIAO S W, YANG S W, ZHANG H Y, et al. A low-Profile wideband tightly coupled dipole array with reduced scattering using polarization conversion metamaterial[J]. IEEE Transactions on Antennas and Propagation, 2019, 67(8): 5353-5361. doi: 10.1109/TAP.2019.2911633 [13] 鲁加国, 王岩. 后摩尔时代, 从有源相控阵天线走向天线阵列微系统[J]. 中国科学:信息科学, 2020, 50(7): 1091-1109. doi: 10.1360/SSI-2019-0247 LU J G, WANG Y. From active phased array antenna to antenna array microsystem in post-moore era[J]. Sci Sin Inform, 2020, 50(7): 1091-1109. doi: 10.1360/SSI-2019-0247 [14] LUY J, MUELLER T, MACK T, et al. Configurable RF receiver architectures[J]. Microwave Magazine IEEE, 2004, 5(1): 75-82. doi: 10.1109/MMW.2004.1284946 [15] 黄晓国, 张锦旗. 一种可重构带通滤波器及其制作方法: 201710344759.5[P]. 2017-12-01. HUANG X G, ZHANG J Q. A reconfigurable bandpass filter and its fabrication method: 201710344759.5[P]. 2017-12-01. [16] 彭凤雄, 董铸祥, 郑金汪, 等. 带宽可重构的射频功率放大器: 202023183362.9[P]. 2020-12-25. PENG F X, DONG Z X, ZHENG J W, et al. Bandwidth reconfigurable RF power amplifier: 202023183362.9[P]. 2020-12-25. [17] 程飞. 可重构滤波器的实现及应用研究[D]. 成都: 电子科技大学, 2015. CHENG F. Study on realization and application of reconfigurable filters[D]. Chengdu: University of Electronic Science and Technology of China, 2005. [18] CHUN D W, Incheon. Variable bandwidth RF filter: US 2015/0061792 A1[P]. 2015-03-05. [19] 侯芳, 孙超, 栾华凯, 等. 小型化硅基毫米波MEMS三维异构集成开关滤波器件[J]. 固体电子学研究与进展, 2021, 41(5): 330-336. HOU F, SUN C, LUAN H K, et al. Heterogeneously integrated compact switchable filters in 3D-MEMS silicon process for millimeter wave application[J]. Reaearch & Progress of SSE, 2021, 41(5): 330-336. [20] CARLOFELICE A D, PAULIS F D, FINA A, et al. Compact and reliable T/R module prototype for advanced space active electronically steerable antenna in 3-D LTCC technology[J]. IEEE Transactions on Microwave Theory and Techniques, 2018, 66: 2746-2756. doi: 10.1109/TMTT.2018.2816020 [21] ATABAK R, SAMAN J, ALEXANDER T, et al. Compact 60 GHz phased-array antennas with enhanced radiation properties in flip-chip BGA packages[J]. IEEE Transactions on Antennas and Propagation, 2018, 6(1): 27-33. [22] WAN L X, TIAN G X HOU F Z, et al. Design and implementation of a compact 3-D stacked RF front-end module for micro base station[J]. IEEE Transactions on Components Packaging and Manufacturing Technology, 2018, 20(1): 27-33. [23] WANG Y, WEI W, YANG D, et al. 3D heterogeneous integration of wideband RF chips using silicon-based adapter board technology[J]. Journal of Southeast University, 2021, 37(1): 8-13. [24] 张兵, 谢俊杰, 康宏毅. 一种三维异构集成综合射频前端微系统: 2020103766802.8[P]. 2020-06-12. ZHANG B, XIE J J, KANG H Y. A three-dimensional heterogeneous integrated integrated RF front-end microsystem: 2020103766802.8[P]. 2020-06-12. [25] SANTAGATA F, SUN F W. System in package (SiP) technology: Fundamental, design and applications[J]. Microelectron Int, 2018, 4: 231-243. [26] 北京未来芯片技术高精尖创新中心. 智能微系统技术白皮书[EB/OL]. (2020-12-16). https://www.163.com/dy/article/FTV31BJ50511BHI0.html. Beijing Innovation Center for Future Chips. White paper on intelligent microsystem technologies[EB/OL]. (2020-12-16). https://www.163.com/dy/article/FTV31BJ50511BHI0.html. [27] 缪旻, 金玉丰. 微系统集成全新阶段—IC芯片与电子集成封装的融合发展[J]. 微电子学与计算机, 2021, 38(1): 1-6. MIAO M, JIN Y F. A new stage for microsystem integration-the integrated development of integrated circuits chips and system-level electronic packaging[J]. Microelectronics & Computer, 2021, 38(1): 1-6. [28] 张墅野, 李振锋, 何鹏. 微系统三维异质异构集成研究进展[J]. 电子与封装, 2021, 21(10): 100106. ZHANG S Y, LI Z F, HE P. Progress on 3D heterogeneous integration of microsystem[J]. Electronics & Packging, 2021, 21(10): 100106. [29] 王梦雅, 丁涛杰, 顾 林. 面向信息处理应用的异构集成微系统综述[J]. 电子与封装, 2021, 21(10): 100102. WANG M Y, DING T J, GU L, et al. Overview of heterogeneous integration microsystem for information processing applications[J]. Electronics & Packaging, 2021, 21(10): 100102. [30] 蒋剑飞, 王琴, 贺光辉, 等. Chiplet技术研究与展望[J]. 微电子学与计算机, 2022, 39(1): 1-6. doi: 10.3969/j.issn.1000-7180.2022.1.wdzxyjsj202201001 JIANG J F, WANG Q, HE G H, et al. Research and prospect on chiplet technology[J]. Microelectronics & Computer, 2022, 39(1): 1-6. doi: 10.3969/j.issn.1000-7180.2022.1.wdzxyjsj202201001 [31] LAU J, LI M, LI M, et al. Fan-Out wafer-level packaging for heterogeneous integration[J]. IEEE Transactions on Components, Packaging and Manufacturing Technology, 2018, 8(9): 1544-1560. doi: 10.1109/TCPMT.2018.2848649 [32] HANCOCK T M, DEMMIN J C. Heterogeneous and 3D integration at DARPA[C]//2019 International 3D Systems Integration Conference (3DIC). Sendai: [s.n.], 2019: 4047. [33] LI T, HOU J, YAN J L, et al. Chiplet heterogeneous integration technology-status and challenges[J]. Electronics, 2020, 9(4): 670. doi: 10.3390/electronics9040670 [34] MAHAJAN R, QIAN Z G, VISWANATH R S. Embedded multi-die interconnect bridge-a localized, high-density multichip packaging interconnect[J]. IEEE Transactions on Components, Packaging and Manufacturing Technology, 2019, 9(10): 1952-1962. doi: 10.1109/TCPMT.2019.2942708 [35] LEE J C, KIM J, KIM K W, et al. High bandwidth memory (HBM) with TSV technique[C]//2016 International SoC Design Conference (ISOCC). [S.l.]: IEEE, 2016: 181-182. [36] 阳王东, 王昊天, 张宇峰, 等. 异构混合并行计算综述[J]. 计算机科学, 2020, 47(8): 5-17. YANG W D, WANG H T, ZHANG Y F, et al. Survey of heterogeneous hybrid parallel computing[J]. Computer Science, 2020, 47(8): 5-17. [37] ANDREWS D, NIEHAUS D. Programming models for hybrid FPGA-CPU computational components: A missing link[J]. IEEE Micro Embedded Systems, 2004, 24(4): 42-53. [38] STEIGER C, WALDER H, PLATZNER M. Operating systems for reconfigurable embedded platforms online scheduling of real-time tasks[J]. IEEE Transaction on Computers, 2004, 53(11): 1393-1407. doi: 10.1109/TC.2004.99 [39] AGRON J, PECK W, ANDERSON E, et al. Run-Time services for hybrid CPU/FPGA systems on chip [C]//2006 27th IEEE International Real-Time Systems Symposium (RTSS'06). Rio de Janeiro: IEEE 2006: 312-318. [40] DENG Q X, ZHANG Y, GUAN N, et al. A unified HW/SW operating system for partially runtime reconfigurable FPGA based computer systems[C]//Proceedings Work-In-Progress Session of the 20th Euromicro Conference on Real-Time Systems. Prague: Euromicro Technical Committee on Real-Time Systems, 2008: 32-35. [41] CHEN Y P, MAILLARD P, BARTON J, et al. Single-Event evaluation of Xilinx 16 nm UltraScale+ high-bandwidth memory enabled FPGA[C]//2019 IEEE Radiation Effects Data Workshop. San Antonio: IEEE, 2019: 1-5. [42] 郑媛媛. 支持透明软硬件编程的混合系统的研究与实现[D]. 沈阳: 东北大学, 2008. ZHENG Y Y. Study and implement of hybrid system supporting transparent SW and HW programming[D]. Shenyang: Northeastern University, 2008. [43] 张轶. 基于FPGA的硬件任务动态可重配置操作系统的设计与实现[D]. 沈阳: 东北大学, 2008. ZHANG Y. Design and implementation of runtime operating system for FPGA-based reconfigurable computers[D]. Shenyang: Northeastern University, 2008. [44] 罗焱. 可重构系统中硬件任务的抽象及通信机制的设计与实现[D]. 沈阳: 东北大学, 2010. LUO Y. Design and implementation of hardware task abstraction and communication mechanisms for reconfigurable systems[D]. Shenyang: Northeastern University, 2010. -

ISSN

ISSN

下载:

下载: