-

基于碳化硅(SiC)宽禁带半导体材料的功率半导体器件具有高临界击穿场强、高电子迁移率、高热导率等特性,非常适合于电机驱动、电力牵引、分布式电源系统等高效率和高功率密度的应用场合。目前已经商业化的碳化硅功率半导体器件有肖特基二极管(Schottky Barrier Diode, SBD)、结型场效应晶体管(Junction Field-Effect Transistor, JFET)、金属−氧化物−半导体场效应晶体管(Metal-Oxide-Semiconductor Field-Effect Transistor, MOSFET)[1-2]。相较于SiC MOSFET,SiC JFET具有更多的优势,它没有栅极氧化层,制造工艺更简单,成本更低,也不存在SiC/Si界面可靠性的问题,并且具有更高的电子迁移率、更低的通态电阻和更小的结电容。然而,出于性能和成本的考虑,SiC JFET经常被设计成耗尽型器件,这给习惯应用增强型器件的电路设计人员带来诸多不便。实际应用中,耗尽型SiC JFET可以通过串联一只增强型低压硅(Si)MOSFET来实现增强型工作模式,这一组合称为SiC/Si级联(Cascode)器件[3]。SiC/Si级联器件采用低压Si MOSFET的驱动电路,并具有SiC JFET器件的优点,在高功率、高效率变换器中具有广阔的应用前景[4-8]。

目前市场上已有SiC/Si级联器件产品,开关特性也得到了系统研究,结果表明,SiC JFET串联低压Si MOSFET后,开关速度和开关损耗都得到了改善[9-13]。与此同时,SiC/Si级联器件的短路特性也到了研究。文献[14]研究了SiC/Si级联器件在脉宽为1.5 μs、偏置电压为击穿电压85%的条件时重复短路脉冲作用下的特性退化情况,经过200个短路脉冲,SiC/Si级联器件的通态电阻增加了1.84%,但阈值电压基本没有变化;文献[15]采用实验和数值模拟方式研究了SiC/Si级联器件的短路特性和失效模式,器件的初始温度对SiC/Si级联器件的短路特性影响不大,数值模拟研究表明,短路过程中SiC JFET耗尽区因热而产生的载流子在JFET的栅极形成了较大的泄漏电流,导致SiC JFET“热奔”,而此时低压Si MOSFET还能正常关断,然而,该文仅分析了SiC/Si级联器件的短路失效,并没有与单独SiC JFET的短路失效作对比,无法评估SiC JFET串联低压Si MOSFET后短路特性的变化。

SiC/Si级联器件的特性主要由SiC JFET决定,尽管低压Si MOSFET在级联器件中只起到开关控制作用,然而,SiC/Si级联器件在器件组合结构上毕竟不同单个的SiC JFET,低压Si MOSFET对SiC/Si级联器件短路特性的影响,以及低压Si MOSFET自身的额定电压对SiC/Si级联器件短路特性的影响,需要得到进一步的研究,以便进一步明确SiC/Si级联器件的短路失效机理。

本文通过实验和数值模拟的方式对比了SiC/Si级联器件与SiC JFET的短路失效,分析了SiC JFET和SiC/Si级联器件在短路失效时刻的温度分布,研究了SiC/Si级联器件中低压Si MOSFET对级联器件短路特性的影响,并讨论了不同额定电压的Si MOSFET对SiC/Si级联器件短路特性的影响。

-

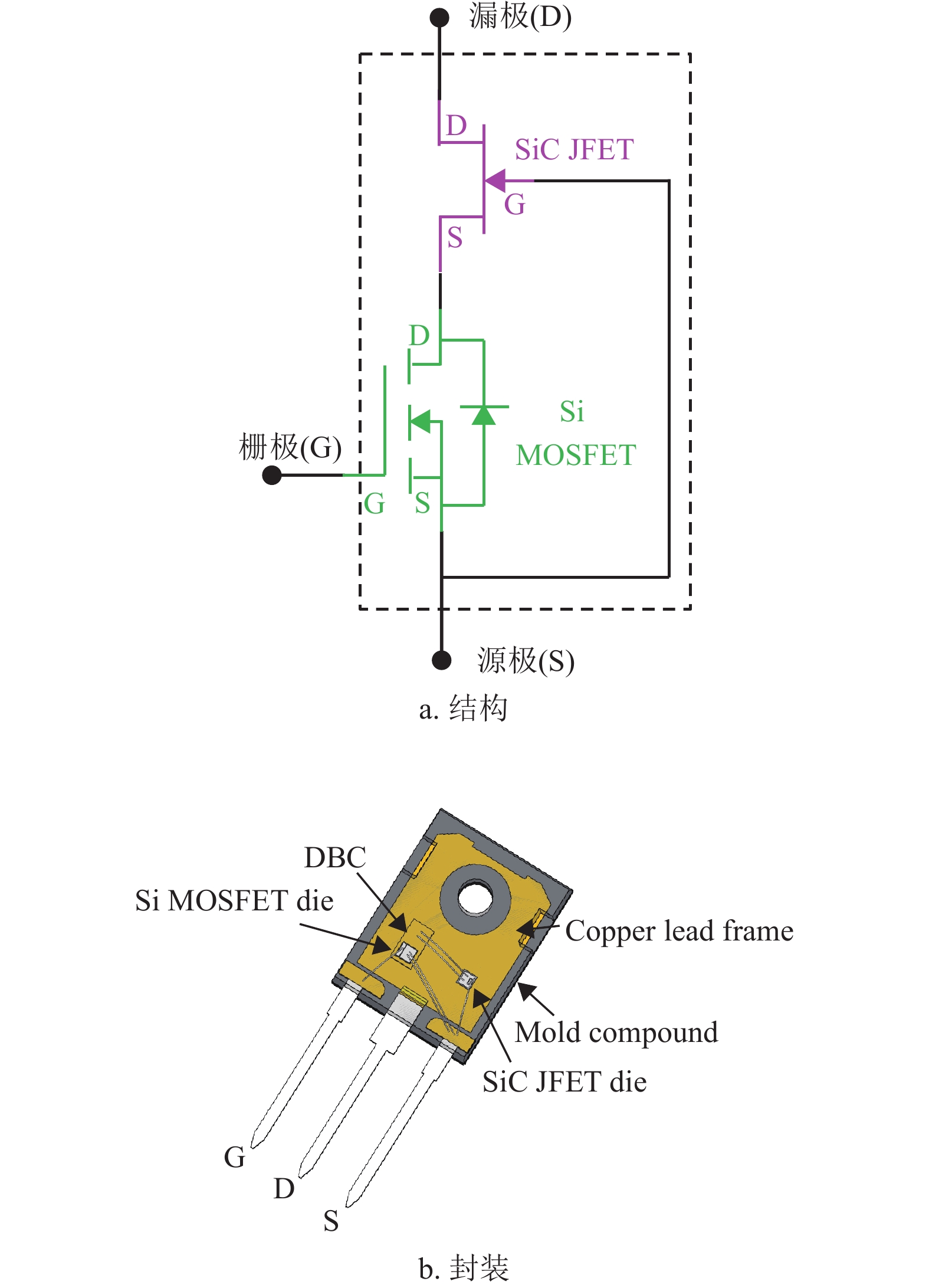

SiC/Si级联器件是将低压Si MOSFET的漏极(Drain, D)−源极(Source, S)并联在SiC JFET的源极(Source, S)−栅极(Gate, G)之间,连接方式如图1所示,其中,图1a为级联器件的组成结构示意图,图1b为采用TO247-3L封装形式的级联器件的内部连线。

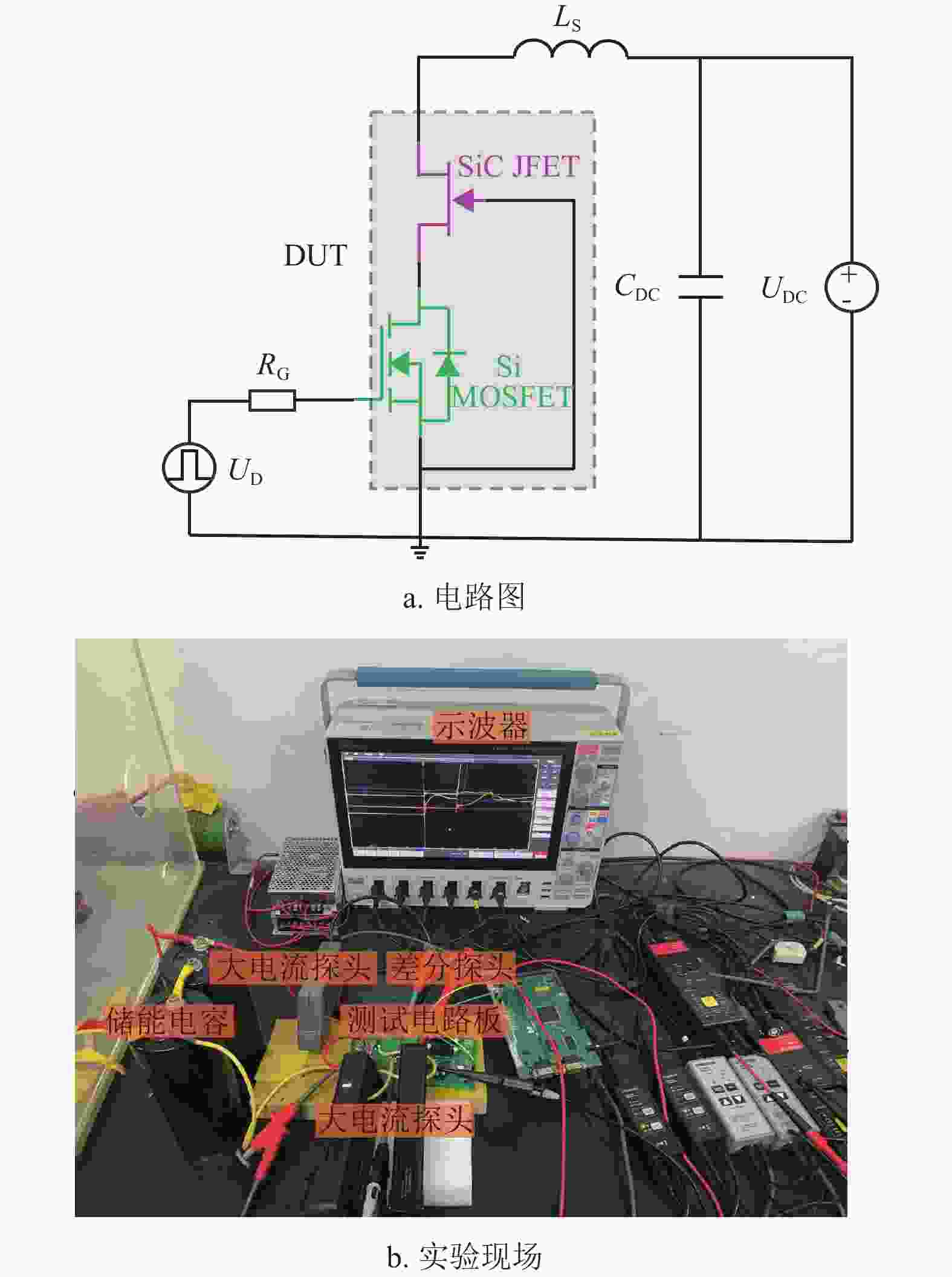

一般而言,功率半导体器件的短路事件主要在两种故障状态下发生[16]:1)硬开关故障(HSF);2)负载故障(FUL)。前者是功率半导体器件已经被短路,然后功率半导体器件导通,后者是功率半导体器件已经处于导通状态时负载短路。本文采用第一种方式来研究低压Si MOSFET对SiC/Si级联器件短路特性的影响,短路测试电路原理图与实验现场图如图2所示,其中,图2a中UDC为直流电源,CDC为储能电容,DUT为被测功率半导体器件,UD为驱动电压,RG为驱动电阻。

图1b中采用TO247-3L封装的级联器件,短路测试时只能测到整个器件的电压和电流,这不利于深入分析低压Si MOSFET对SiC/Si级联器件短路特性的影响。本文短路测试的DUT,除了TO247-3L封装的SiC/Si级联器件,还有分立的SiC JFET、Si MOSFET以及由分立的SiC JFET和Si MOSFET构成的级联器件,其中,分立的SiC JFET与SiC/Si级联器件来自于同一家厂商,Si MOSFET为沟槽栅结构,与所选用的SiC/Si级联器件产品手册对其中的Si MOSFET的描述保持一致。表1列出了所选用的SiC/Si级联器件、分立的SiC JFET和Si MOSFET的型号、参数及其封装形式。

表 1 实验所用器件型号及其参数

类型 型号 电压/V 电流/A 封装 第三代SiC/Si级

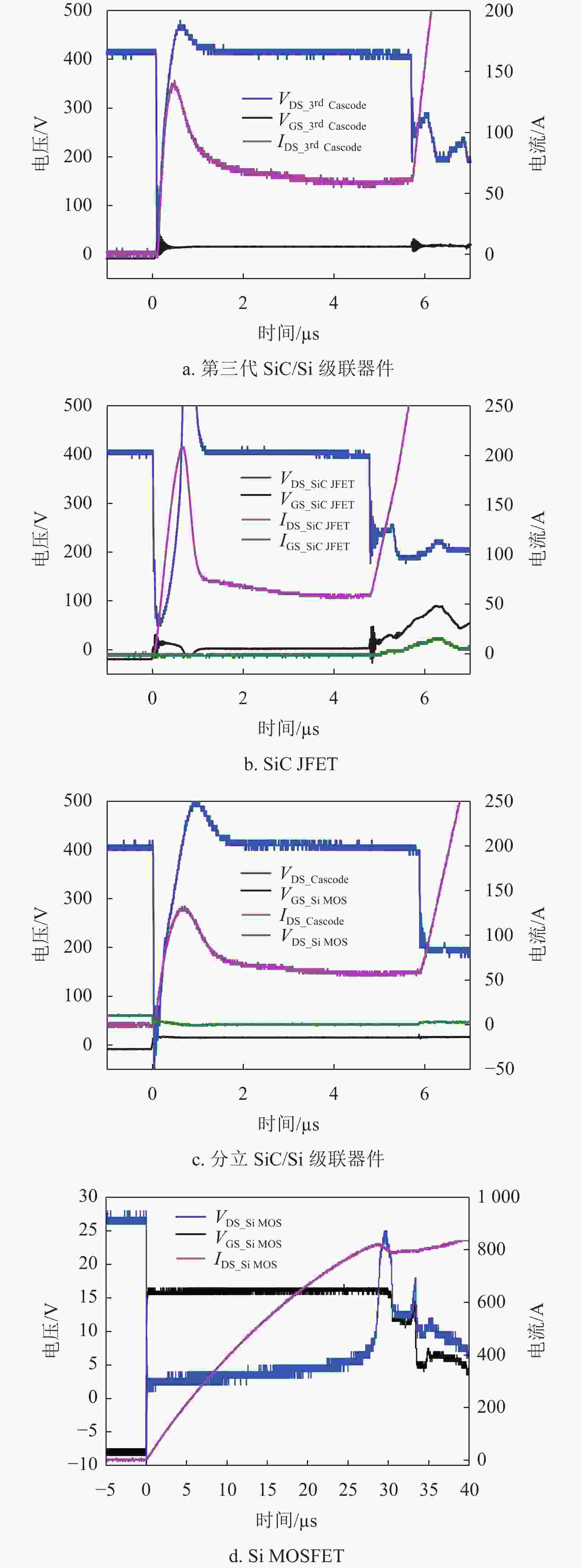

联器件UJ3C065080K3S 650 31 TO247-3L SiC JFET UJ3N065080K3S 650 32 TO247-3L Si MOSFET SiSHA10DN 30 30 PowerPAK-1212-8 图3展示了表1所示的器件在短路过程中的电压和电流,包括漏源电压VDS、栅极电压VGS、漏源电流IDS、栅极电流IGS,测试时图3a−图3c的直流电源UDC为400 V,图3d为25 V。表2总结了图3在4种测试情况时的短路饱和电流峰值和短路失效时间。

表 2 短路实验结果总结

类型 直流电压/V 饱和电流峰值/A 失效时间/μs SiC JFET 400 207 4.8 Si MOSFET 25 824 29.5 第三代SiC/Si级联器件 400 140 5.7 分立器件组成的级联器件 400 130 5.9 -

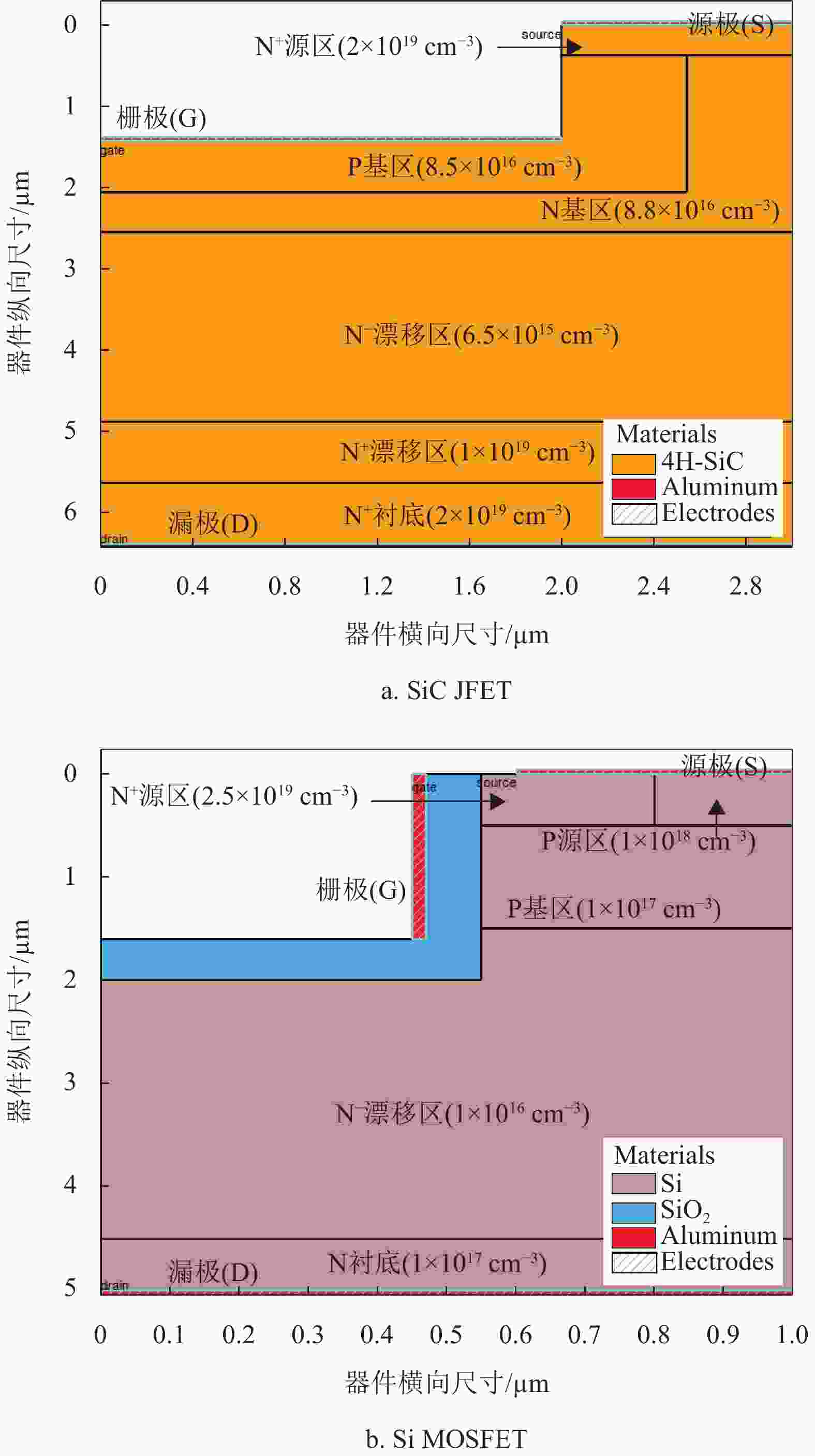

利用半导体器件计算机模拟软件(TCAD)建立了SiC/Si级联器件中SiC JFET和Si MOSFET的数值模型。表1所示额定电压为650 V的SiC JFET,其理论击穿电压一般设计为800 V,30 V的Si MOSFET的理论击穿电压为38 V,根据此规则,TCAD中建立的SiC JFET和Si MOSFET的半幅二维数值模型如图4所示,包括N型衬底、N型漂移区、P型基区、N型基区,N型源区、P型源区和相应的电极,其中,N型漂移区和P型基区的掺杂浓度和厚度决定了半导体器件的击穿。

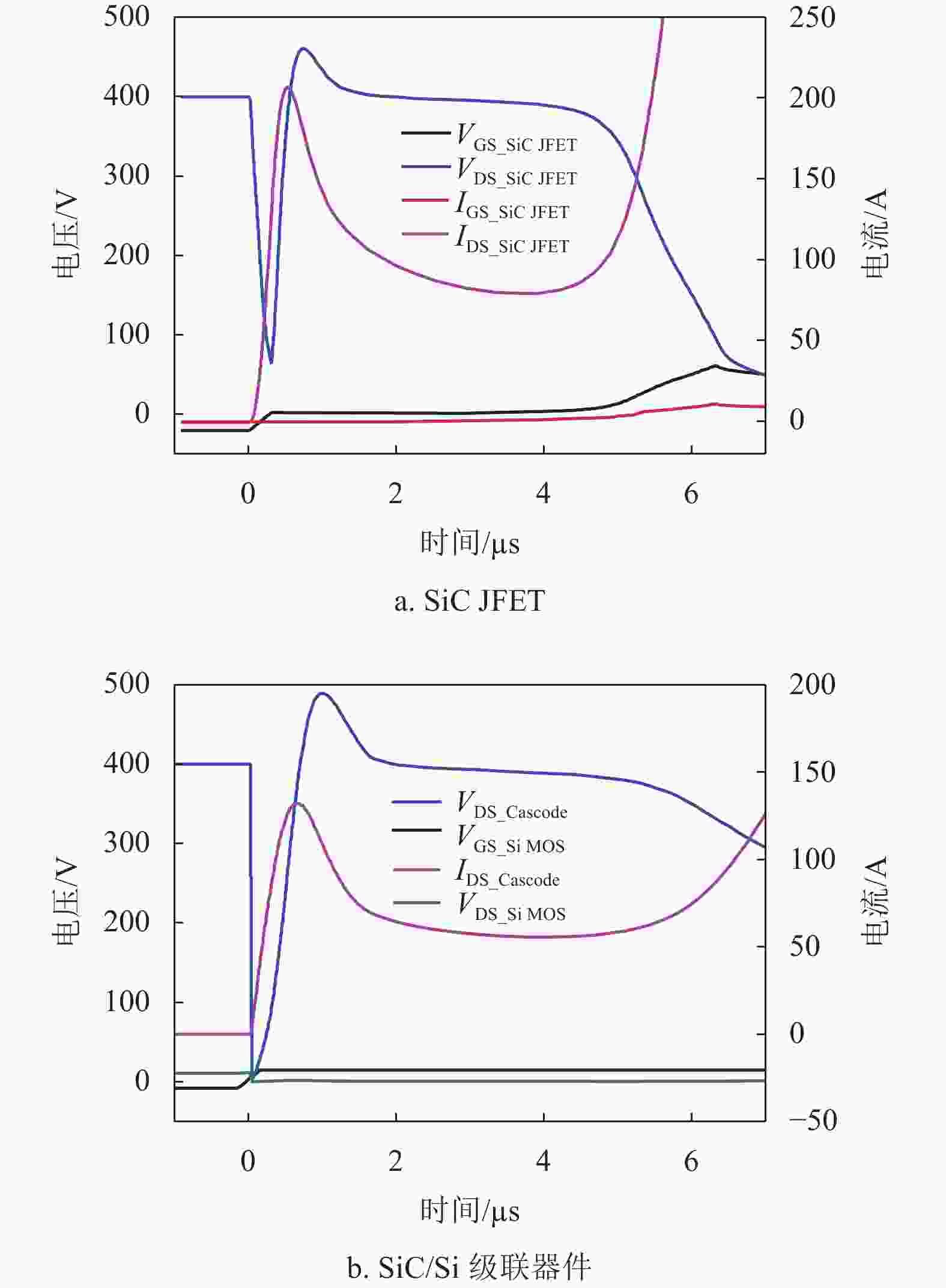

数值模型在模拟短路特性时,考虑了高温下的带隙变窄效应、载流子复合效应、高载流子密度下的俄歇复合效应,引入了与温度相关的载流子迁移率模型,同时,为了进一步提高模型的精度,SiC JFET采用了文献[17]中与温度相关的热容率。图5展示了图4所示的SiC JFET、SiC JFET与Si MOSFET构成的分立级联器件在直流电压为400 V时短路过程中的电压和电流,其中,描述功率半导体器件短路特征的两个关键参数—短路时的饱和电流峰值和短路失效时间,SiC JFET分别为206 A和4.86 μs,SiC JFET与Si MOSFET构成的分立级联器件分别为132 A和5.8 μs,与表2所示的实验结果基本一致。

-

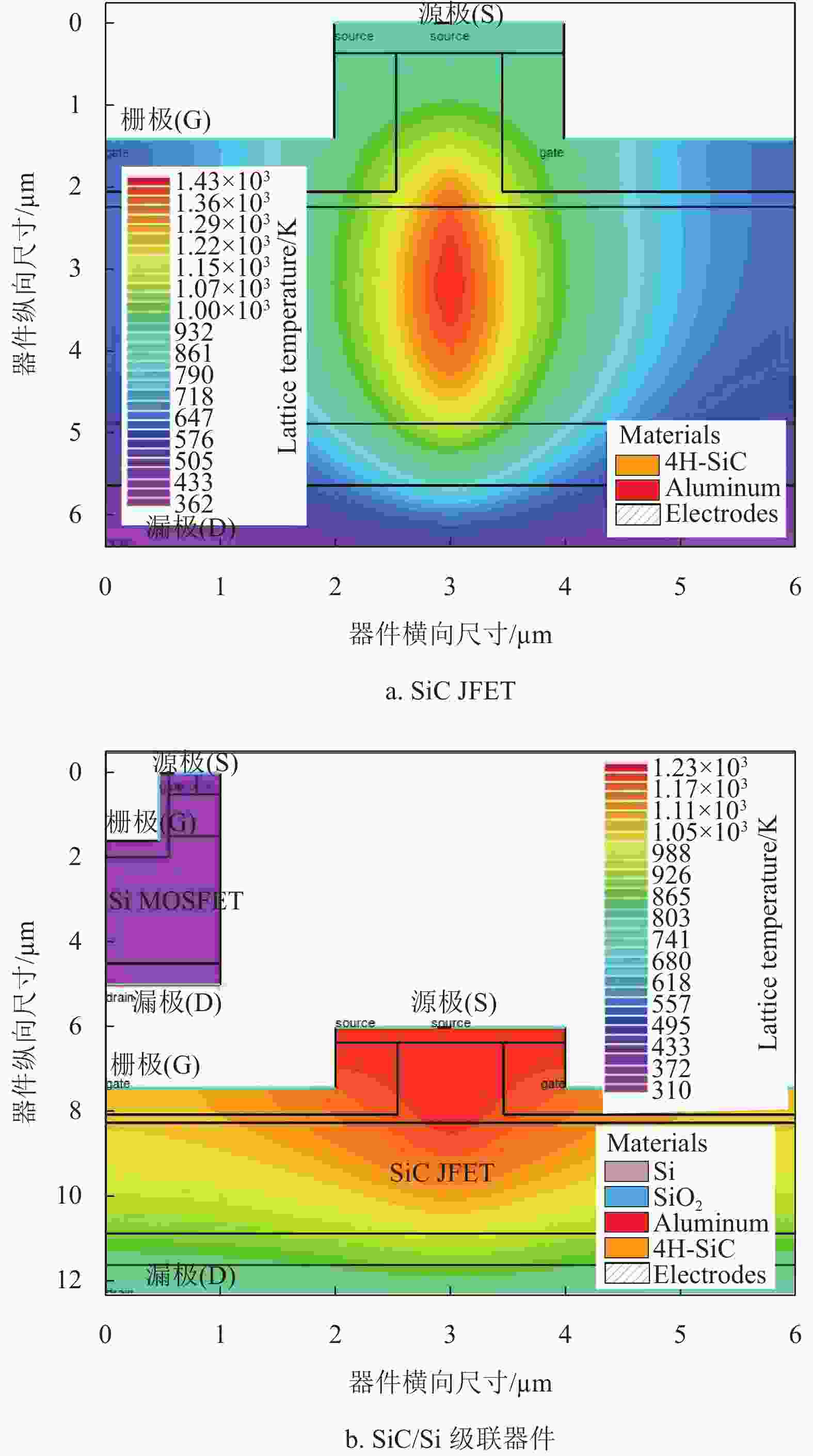

表2所示,由分立器件组成的级联器件和采用TO247-3L封装的级联器件它们的短路饱和电流峰值和短路失效时间相近,但与单独的SiC JFET相差较大,同时也可以看到,SiC JFET串联了低压Si MOSFET后,短路失效时间延长了。SiC JFET串联低压器件后短路失效时间得到了延长,这个能够从数值模型内的温度分布来分析。图6给出了单独的SiC JFET和SiC/Si级联器件在短路失效时刻器件内的温度分布,图7给出了在短路失效前器件内最高温度的变化。从图6a可以看出,SiC JFET失效时,最高温度位于从漏极到源极的电流通道上的N-漂移区,并向SiC JFET的上表面扩散,导致SiC JFET的栅极出现了泄漏电流,最终在失效时刻,SiC JFET的栅极电流也出现了失控现象(见图3b),不过栅极泄漏电流的形成最初是从靠近沟道中的温度最高点附近开始,之后才向左右两侧扩散,因而栅极泄漏电流上升较为缓慢。当SiC JFET与Si MOSFET组成级联器件后,图6b所示的SiC JFET的高温区位于源极附近区域,并向左右两侧的栅极区域延伸,因而SiC JFET的栅极也会出现泄漏电流,这个泄漏电流覆盖整个SiC JFET的栅极区域,因此在短路失效后级联器件中的SiC JFET栅极泄漏电流快速上升。同时,从图7可以看出,在失效前,单独的SiC JFET在短路过程中的最高温度一直都比SiC/Si级联器件的最高温度高,温度高意味着器件的损耗高,器件发热严重,最终因为热击穿而失效。

形成图6和图7两种器件内的温度分布差异,与SiC/Si级联器件的组成结构有关。导通后的低压Si MOSFET等效为一个小电阻,相当于在SiC/Si级联器件的短路电流通道上增加了一个小电阻,这个小电阻在一定程度上能降低短路饱和电流的峰值,在一定程度上抑制了SiC JFET内的温升,同时器件内的热量也能够扩散到SiC JFET的源极表面,因而形成了图6b所示的SiC JFET源极表面附近的温度分布。

另外,从图6b可以看出,SiC/Si级联器件失效时Si MOSFET内的温度远比SiC JFET低,这和图2d所示的Si MOSFET较强的短路耐受能力有关,因而级联器件短路时先失效的是SiC JFET。

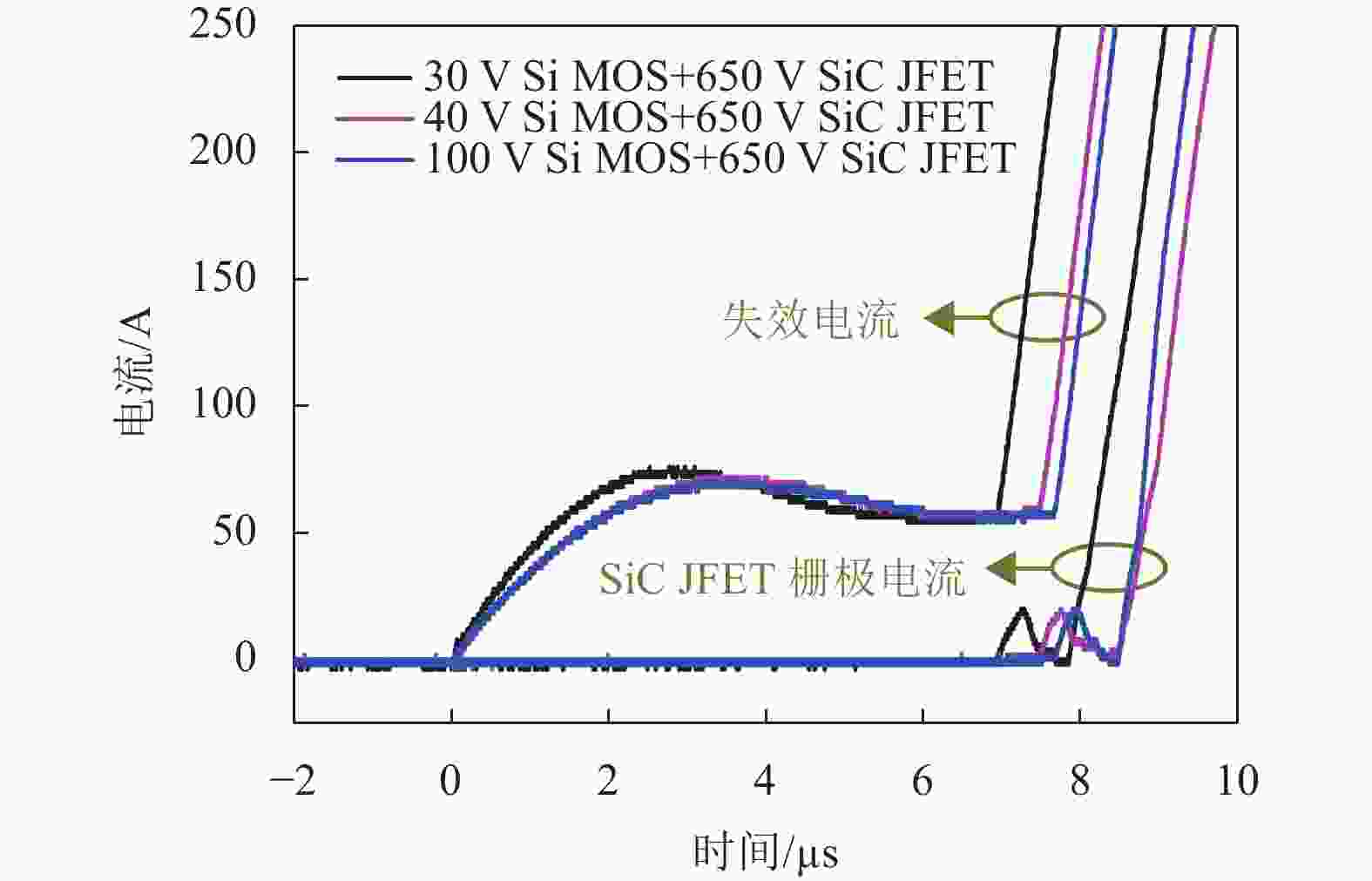

SiC JFET串联低压Si MOSFET后短路失效时间得到了延长,这个延长时间还与低压Si MOSFET自身的额定电压有关。图8展示了额定电压分别为30 、40 、100 V的Si MOSFET与同一型号的SiC JFET构成的分立级联器件的短路失效时的实验波形,可以看出随着Si MOSFET额定电压的增加,分立级联器件的短路失效时间也相应增加。在这个实验中,由于用大电流钳测了SiC JFET的栅极电流,额外引入了一段导线,这带来了一定的寄生电感,与图3c中没有引入额外导线的分立级联器件相比,失效电流上升较为缓慢。

图8中3种额定电压的Si MOSFET来自于同一厂商、同一种封装,并且额定电流都为30 A,可以判定随着额定电压的增加,Si MOSFET的内阻也增加,所构成的分立级联器件的短路饱和电流峰值相应降低,进一步延长了短路失效时间。

图8中的SiC JFET栅极电流在级联器件失效时快速上升,达到峰值后又下降,之后又快速上升。第一个快速上升阶段,与前述的SiC JFET内温度分布有关,栅极泄漏电流覆盖整个SiC JFET的栅极区域,之后主要受载流子速度饱和以及载流子迁移率负温系数等效应的影响,泄漏电流到达峰值后又下降,最终由于栅极区域的反偏PN结被击穿栅极电流也出现了失控,因而级联器件中SiC JFET的失效先是漏源极失效,之后是栅极失效。

-

本文利用实验和数值模拟的方式研究了低压Si MOSFET对SiC/Si级联器件短路特性的影响,结果表明,SiC JFET串联低压Si MOSFET后短路失效时间得到了延长,数值模拟结果显示,短路过程中SiC/Si级联器件中SiC JFET内的最高温度比单独SiC JFET的最高温度低。最后讨论了不同额定电压的Si MOSFET对SiC/Si级联器件短路特性的影响,结果表明,随着低压Si MOSFET额定电压的增加,SiC/Si级联器件的短路失效时间也增加。

Effect of Low-Voltage Si MOSFETs on Short-Circuit Characteristics of SiC/Si Cascode Devices

-

摘要: 由低压硅金属−氧化物−半导体场效应晶体管(Silicon Metal-Oxide-Semiconductor Field-Effect Transistor, Si MOSFET)和碳化硅结型场效应晶体管(Silicon Carbon Junction Field-Effect Transistor, SiC JFET)构成的SiC/Si级联(Cascode)器件,兼具了低压Si MOSFET易于驱动、SiC JFET高耐压低损耗等优点。该文采用实验和数值模拟的方式研究了低压Si MOSFET对SiC/Si级联器件短路特性的影响,结果表明,在短路过程中SiC/Si级联器件中的SiC JFET最高温度比单独的SiC JFET短路时的最高温度低,SiC/Si级联器件的短路失效时间得到了延长,并且随着Si MOSFET额定电压的增加,SiC/Si级联器件短路失效延长的时间也在增加。

-

关键词:

- 泄漏电流 /

- SiC/Si级联器件 /

- SiC JFET /

- 短路失效

Abstract: SiC/Si cascode device, formed by low-voltage Silicon Metal-Oxide-Semiconductor Field-Effect Transistor (Si MOSFET) and Silicon Carbon Junction Field-Effect Transistor (SiC JFET), has several advantages such as low driving-voltage of Si MOSFET, high blocking-voltage, and low loss of SiC JFET. In this paper, the effect of low-voltage Si MOSFET on the short-circuit performance of SiC/Si cascode device has been investigated with experiment and numerical simulation. The results give that during the short circuit, the highest temperature of SiC JFET in the cascode case is lower than that of single SiC JFET case, so the short-circuit failure duration of SiC/Si cascode device is longer than that of single SiC JFET. Moreover, with the increasing in the rated voltage of Si MOSFET, the short-circuit failure duration for SiC/Si cascode device also increases.-

Key words:

- leakage current /

- SiC/Si cascode device /

- SiC JFET /

- short-circuit failure

-

表 1 实验所用器件型号及其参数

类型 型号 电压/V 电流/A 封装 第三代SiC/Si级

联器件UJ3C065080K3S 650 31 TO247-3L SiC JFET UJ3N065080K3S 650 32 TO247-3L Si MOSFET SiSHA10DN 30 30 PowerPAK-1212-8 表 2 短路实验结果总结

类型 直流电压/V 饱和电流峰值/A 失效时间/μs SiC JFET 400 207 4.8 Si MOSFET 25 824 29.5 第三代SiC/Si级联器件 400 140 5.7 分立器件组成的级联器件 400 130 5.9 -

[1] 文译, 陈致宇, 邓小川, 等. 10 kV SiC LBD-MOSFET结构设计与特性研究[J]. 电子科技大学学报, 2021, 50(4): 520-526. doi: 10.12178/1001-0548.2021084 WEN Y, CHEN Z Y, DENG X C, et al. Design and characteristics of a novel 10 kV SiC MOSFET embedding low barrier diode[J]. Journal of University of Electronic Science and Technology of China, 2021, 50(4): 520-526. doi: 10.12178/1001-0548.2021084 [2] 周郁明, 穆世路, 蒋保国, 等. SiC/SiO2界面态电荷对SiC MOSFET短路特性影响的研究[J]. 电子科技大学学报, 2019, 48(6): 947-953. ZHOU Y M, MU S L, JIANG B G, et al. Research on the impact of trapped charges at SiC/SiO2 interface on the short-circuit performances of SiC MOSFET[J]. Journal of University of Electronic Science and Technology of China, 2019, 48(6): 947-953. [3] XIE R, SHI Y J, LI H. Study of 1200 V SiC JFET cascode device[C]//IEEE 5th Workshop on Wide Bandgap Power Devices and Applications. Albuquerque: IEEE, 2017: 316-320. [4] ZHU K, O'GRADY M, DODGE J, et al. 1.5 kW single phase CCM totem-pole PFC using 650V SiC cascodes[C]//IEEE 4th Workshop on Wide Bandgap Power Devices and Applications. Fayetteville: IEEE, 2016: 90-94. [5] WU R Z, GONZALEZ J O, DAVLETZHANOVA Z, et al. The Potential of SiC cascode JFETs in electric vehicle traction inverters[J]. IEEE Transactions on Transportation Electrification, 2019, 5(4): 1349-1359. doi: 10.1109/TTE.2019.2954654 [6] ZHU K, BHALLA A, DODGE J. Enabling 99.3% efficiency in 3.6 kW totem-pole PFC using new 750 V Gen 4 SiC FETs[J]. IEEE Power Electronics Magazine, 2021, 8(4): 30-37. doi: 10.1109/MPEL.2021.3123757 [7] WU R Z, GONZALEZ J O, DAVLETZHANOVA Z, et al. Fast switching SiC cascode JFETs for EV traction inverters[C]//IEEE Applied Power Electronics Conference and Exposition. New Orleans: IEEE, 2020: 3489-3496. [8] DODGE J. SiC JFET cascode enables higher voltage operation in a phase shift full bridge DC-DC converter[C]//International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management. Nuremberg: VDE, 2016: 484-491. [9] MIHAILA A, UDREA F, AZAR R, et al. Analysis of static and dynamic behaviour of SiC and Si devices connected in cascode configuration[C]//International Semiconductor Conference. Sinaia: IEEE, 2001: 333-336. [10] ZHAO C, WANG L L, YANG X, et al. Comparative investigation on paralleling suitability for SiC MOSFETs and SiC/Si cascode devices[J]. IEEE Transactions on Industrial Electronics, 2022, 69(4): 3503-3514. doi: 10.1109/TIE.2021.3070519 [11] GONZALEZ J O, WU R Z, JAHDI S, et al. Performance and reliability review of 650 V and 900 V silicon and SiC devices: MOSFETs, cascode JFETs and IGBTs[J]. IEEE Transactions on Industrial Electronics, 2020, 67(9): 7375-7385. doi: 10.1109/TIE.2019.2945299 [12] SIEMIENIEC R, NOEBAUER G, DOMES D. Stability and performance analysis of a SiC-based cascode switch and an alternative solution[J]. Microelectronics Reliability, 2012, 52(3): 509-518. doi: 10.1016/j.microrel.2011.12.006 [13] ALONSO A R, DÍAZ M F, LAMAR D G, et al. Switching performance comparison of the SiC JFET and SiC JFET/Si MOSFET cascode configuration[J]. IEEE Transactions on Power Electronics, 2014, 29(5): 2428-2440. doi: 10.1109/TPEL.2013.2283144 [14] MARROQUIA D, GARRIGOS A, BLANES J M, et al. SiC MOSFET vs SiC/Si cascode short circuit robustness benchmark[J]. Microelectronics Reliability, 2019, 100-101: 113429. doi: 10.1016/j.microrel.2019.113429 [15] AGBO S N, BASHAR E, WU R Z, et al. Simulations and measurements of failure modes in SiC cascode JFETs under short circuit conditions[C]//IEEE 22nd Workshop on Control and Modelling of Power Electronics. Cartagena: IEEE, 2021: 1-7. [16] KAMPITSIS G, PAPATHANASSIOU S, MANIAS S. Comparative evaluation of the short-circuit withstand capability of 1.2 kV silicon carbide (SiC) power transistors in real life applications[J]. Microelectronics Reliability, 2015, 55: 2640-2646. doi: 10.1016/j.microrel.2015.09.012 [17] TSIBIZOV A, KOVACEVIC-BADSTUBNER I, KAKARLA B, et al. Accurate temperature estimation of SiC power MOSEFETs under extreme operating conditions[J]. IEEE Transactions on Power Electronics, 2020, 35(2): 1855-1865. doi: 10.1109/TPEL.2019.2917221 -

ISSN

ISSN

下载:

下载: