-

超高速数据采集系统是电子仪器、雷达等电子设备的基础。以高速数字存储示波器(Digital Storage Oscilloscope, DSO)为例,待测信号首先经过信号调理电路将待测信号电压调节到合适范围,随后,模数转换器(Analog to Digital Converter, ADC)将模拟信号进行量化后处理,量化后的信号送到现场可编程门阵列(Field Programmable Gate Array, FPGA)进行同步接收、触发、存储和后端处理。随着DSO功能的日益复杂,单片FPGA很难实现上述功能,往往需要将示波器的许多功能进行划分,并分配到不同的FPGA上,形成“主从”采集控制体系结构。在这种架构下,FPGA之间异步控制信号和数据的传输会在信号采集时产生相位偏差甚至故障,从而影响采集系统的功能。因此,解决FPGA间同步传输问题成为超高速采集系统的一个重点研究方向[1-2]。

FPGA之间的传输方式有很多,包括单数据速率(Single Data Rate, SDR)、双倍速率(Double Data Rate, DDR)、串行/解串器(SERializer/DESerializer, SERDES)和高速收发器(Gigabit Transceiver, GT)[3-6]。其中,GT的传输同步是基于嵌入式时钟的自同步方式,主要用于板间数据传输。然而,GT不同于其他传输方式,其资源有限,难以满足多FPGA系统的要求[7]。其余的则是基于源同步的方式进行传输,即发送一个同步的伴随时钟来实现发送和接收之间的同步。在源同步传输模式下,时钟与数据的时延是否一致成为源同步的关键点。此外,在源同步中,由跨板传输延迟引入的亚稳态问题也是源同步成功的一个障碍,特别是随着数据传输速率的提高,时钟的同步裕量进一步减小,这增加了源同步实现的难度[8]。

围绕这一问题,文献[9-10]通过调节IODELAY单元的延迟,并且配合FPGA的BITSLIP功能,实现了数据传输的同步,但其对于多bit同步间的参考选择较为敏感,并未选取最稳定的延迟区间。另外一种方法则是通过增加数据帧头或者增加校验位的方式进行同步,但这类方法的缺点在于传输中存在大量的冗余信息[11]。

基于以上问题,本文对DSO中数据采集系统的多FPGA间源同步技术进行了研究。借助FPGA的IODELAY单元,通过测试数据训练,找到最稳定的同步传输延时,配合移位寄存器实现DSO中多FPGA之间控制信号以及数据信号的同步稳定传输。

-

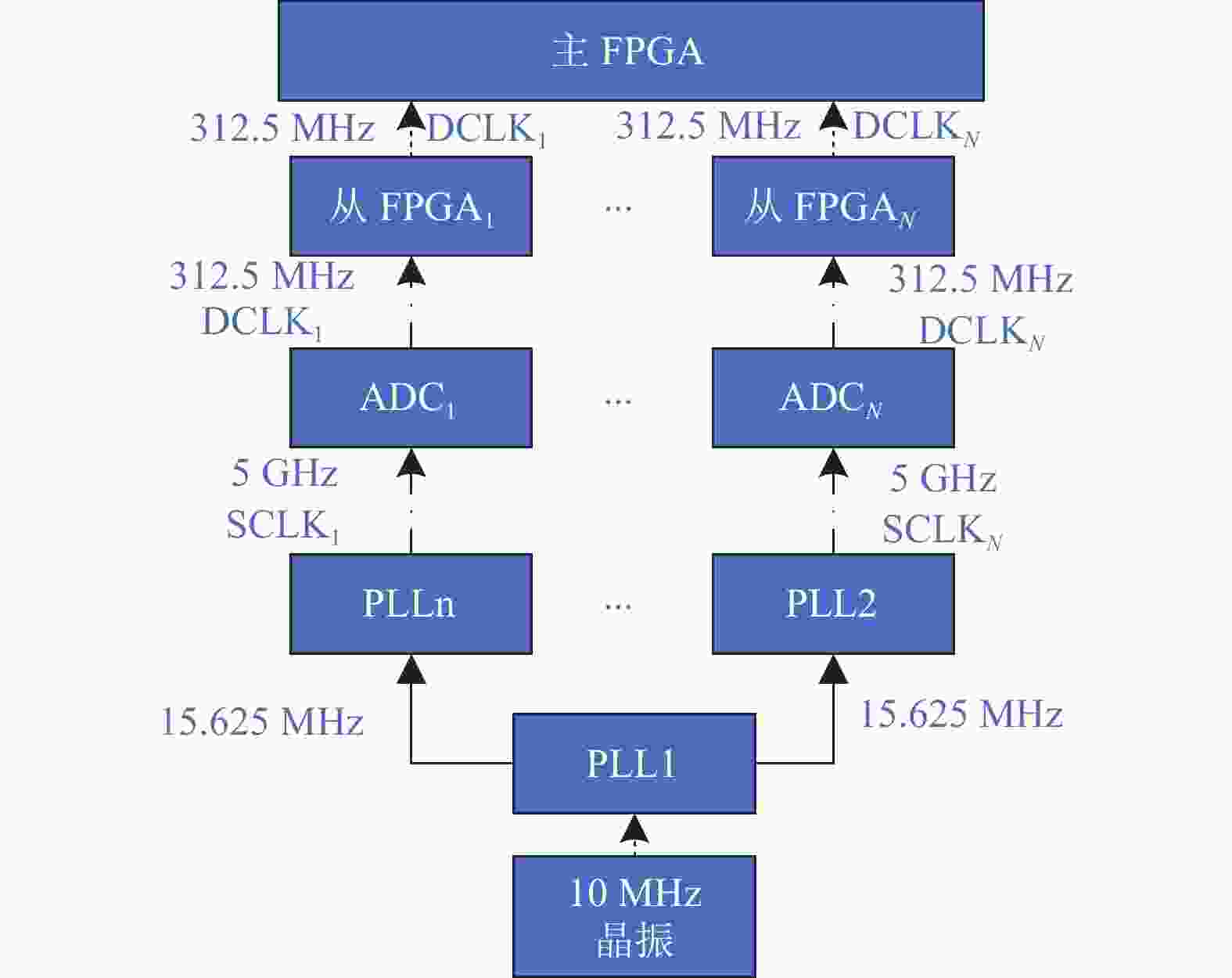

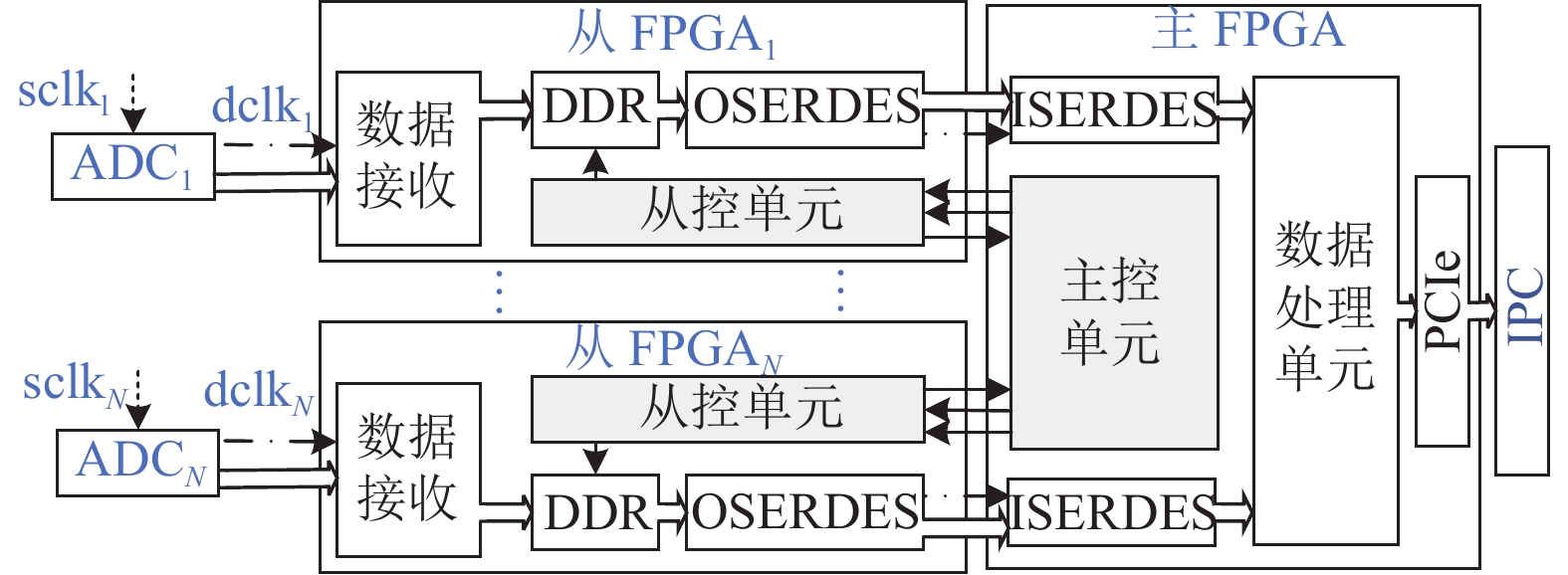

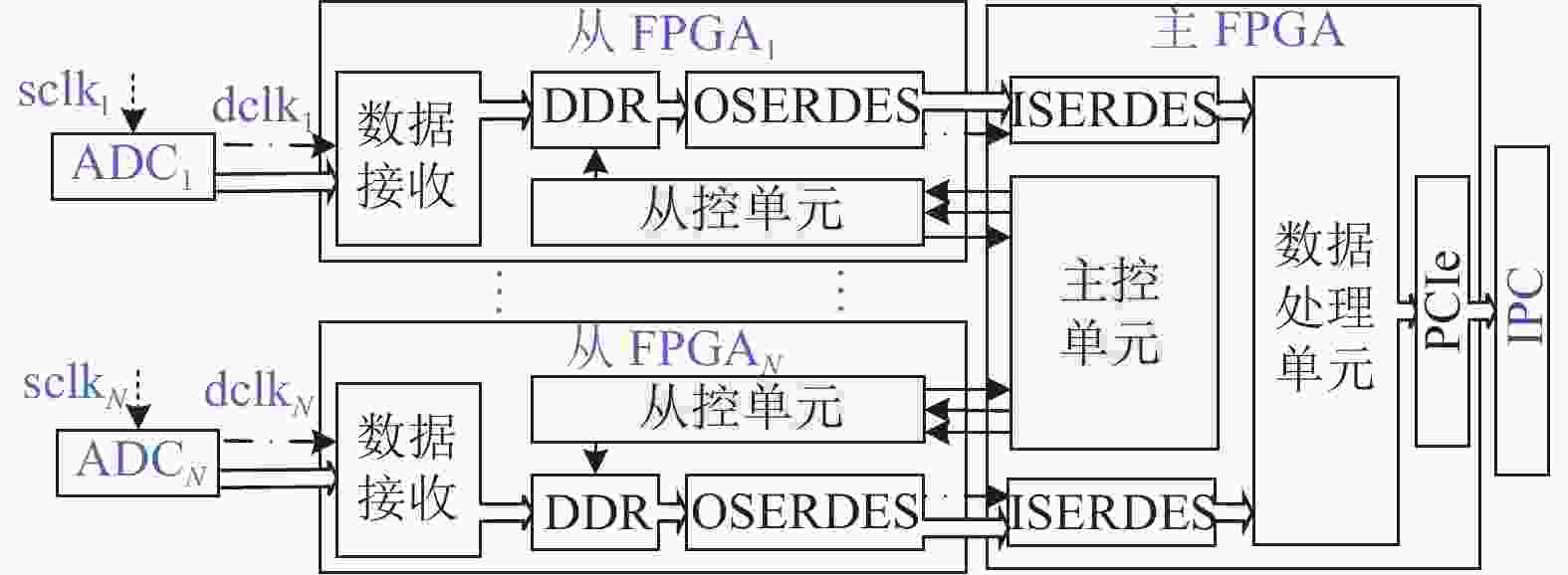

典型的“主从”数据采集系统如图1所示,其中从FPGA用于接收ADC采样数据和DDR存储,系统采集控制主控单元位于主FPGA,通过产生主控信号控制从FPGA中的从控单元,实现对多片FPGA的同步控制。同时,主FPGA负责接收来自多个从FPGA的数据,并专注于后续的信号处理过程。处理后的数据经过PCIe接口传输到工业个人计算机(Industry Personal Computer, IPC)进行测量和显示。

在图1中,从FPGA和主FPGA之间的信号传输主要包括数据信号和控制信号两类。所有的信号基于ADC的随路时钟dclkN作为同步时钟以源同步方式传输。由于传输速率以及位宽的要求,数据通常采用SERDES进行传输,而控制信号采用SDR的方式直接传输。

-

对于“主从”架构采集系统,首先要确保多个FPGA之间时钟的同源性,本系统同步时钟设计的时钟树结构如图2所示。

在图2中,所有时钟都来自一个10 MHz的晶体振荡器。在锁相到10 MHz振荡器后,锁相环1(PLL)产生15.625 MHz时钟信号并将其发送给锁相环PLL2~PLLn,PLL2~PLLn锁相环产生5 GHz采样时钟并将其发送给ADC。每个ADC根据5 GHz采样时钟进行分频,生成一个312.5 MHz的数据相关的同步时钟,发送到相应的从FPGA进行同步数据接收。同时,采用312.5 MHz时钟作为FPGA的主系统时钟,用于DDR存储控制和后端数据传输。该时钟也作为伴随时钟发送到主FPGA进行数据传输和控制。

在主FPGA中,通常选择第一个从FPGA的关联时钟作为主FPGA的主时钟,完成多个从FPGA的数据接收和同步控制。

这种时钟结构保证了多个从FPGA与主FPGA之间时钟的一致性,为后续的控制信号和数据传输同步提供了前提。

-

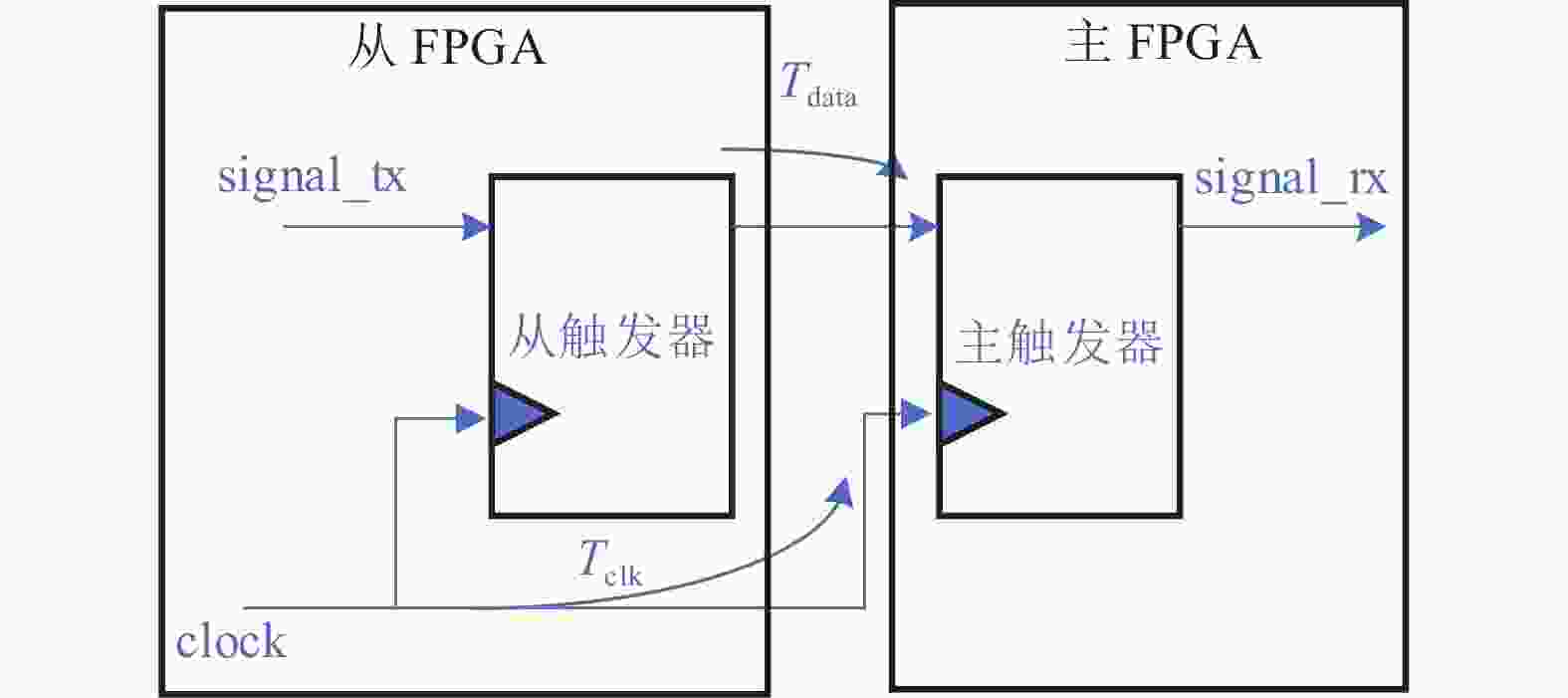

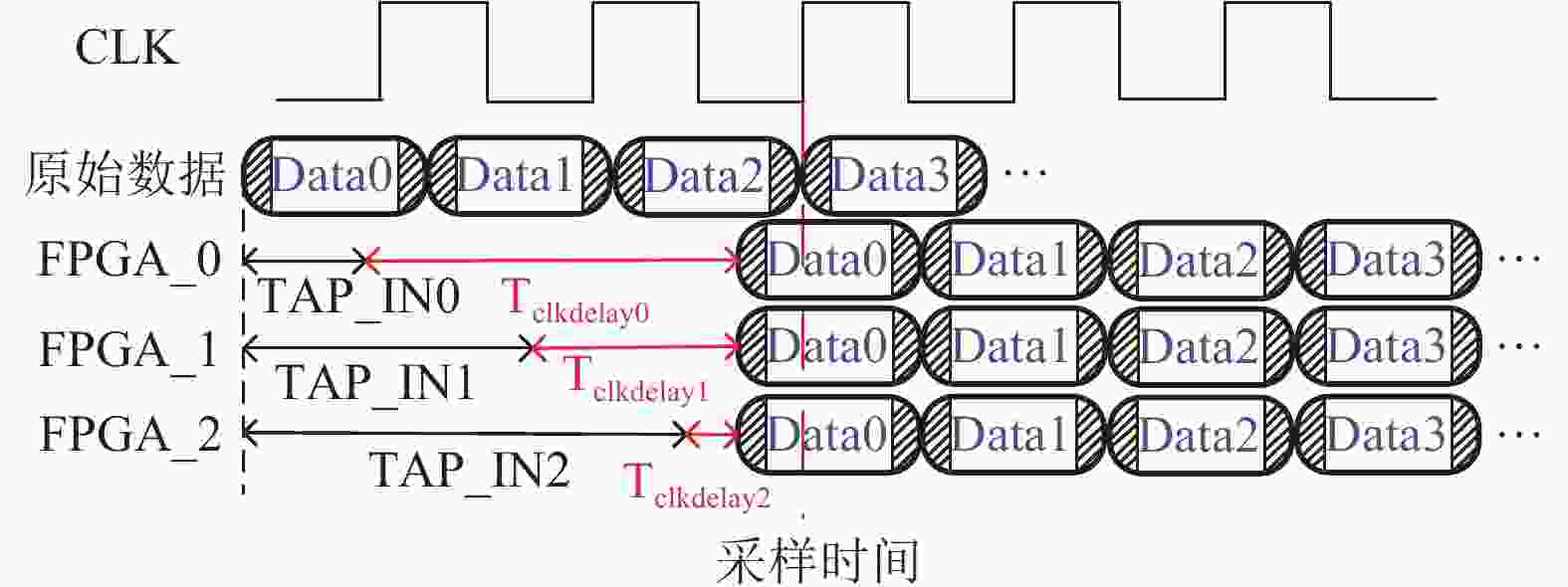

在上述的采样架构中,“主从”FPGA完成了时钟同源的设计,所有的FPGA均工作在同源的模式下,多片FPGA之间的源同步传输如图3所示。

其中,

$ {T_{{\rm{clk}}}} $ 为从FPGA触发器时钟到主FPGA触发器的时钟延时,$ {T_{{\rm{data}}}} $ 为从FPGA触发器时钟到主FPGA触发器的数据延时。当$ {T_{{\rm{clk}}}} = {T_{{\rm{data}}}} $ 时,自然会建立源同步。但由于PCB加工精度、信号跨bank传输、温度变化等原因,两者之间存在一定程度的偏差,可能导致多根线之间接收亚稳态和时序偏差,如图4所示。对于这种异步现象,影响最大的是亚稳态的接收问题。亚稳态的存在会在信号前后产生一个时钟clk的随机误差,这对控制信号和数据信号是致命的。固定偏差主要影响数据信号的传输,特别是在并行多比特传输的情况下,某一比特的错位会导致封装数据出现错误。如在图4中,发送端与接收端符合严格的时序关系,但接收端由于传输延时导致接收端的Ctrl_Lane1k信号跳变发生在时钟的亚稳态区间,从而导致控制信号时序关系存在±1clk的随机误差。对于数据传输线,Data_Lane2k, Data_Lane3k发送端发送的是稳定的“00-11-00-11”,而传输延时导致接收端虽然没有落在亚稳态区间,但接收的数据序列是“10-01-10-01”发生了数据的错位。

因此,解决FPGA之间同步传输的关键在于消除传输的亚稳态,并且实现多比特之间的固定延时传输。

-

基于以上分析,本文提出一种基于同步窗口扫描的FPGA间传输同步方法。本方法针对亚稳态以及传输延时导致的不同步的问题,借助FPGA中的IODELAY单元,通过调节图3中的

$ {T_{{\rm{data}}}} $ 消除亚稳态并且实现多比特数据的同步传输。在系统初始化阶段,发送端产生01翻转的序列,接收端对该序列进行接收并且完成组包,遍历不同IDELAY单元的TAP值,寻找最稳定的TAP值区间,消除亚稳态的影响。 并在此基础上引入并行移位寄存器来实现多比特位之间的同步以及FPGA之间传输的同步。在该方法中,FPGA负责自动调整IDELAY单元的TAP值并存储窗口扫描结果。IPC软件端负责根据FPGA窗口扫描的结果计算稳定的TAP值区间以及多比特位之间对齐的并行移位值,系统框架如图5所示。

在图5中,FPGA硬件电路运转速度快,主要完成状态机的运转和测试数据的重复比较;软件运行灵活度高,主要完成稳定TAP值的计算分析。

软件下发控制信号,使主从FPGA配置为同步测试模式,在测试模式下,硬件端的同步传输模块会通过状态机运转,生成一个包含有效延迟值(TAP)信息的RAM回传至软件端,软件算法计算最稳定的TAP作用于IDELAY单元,使信号能够稳定传输。

-

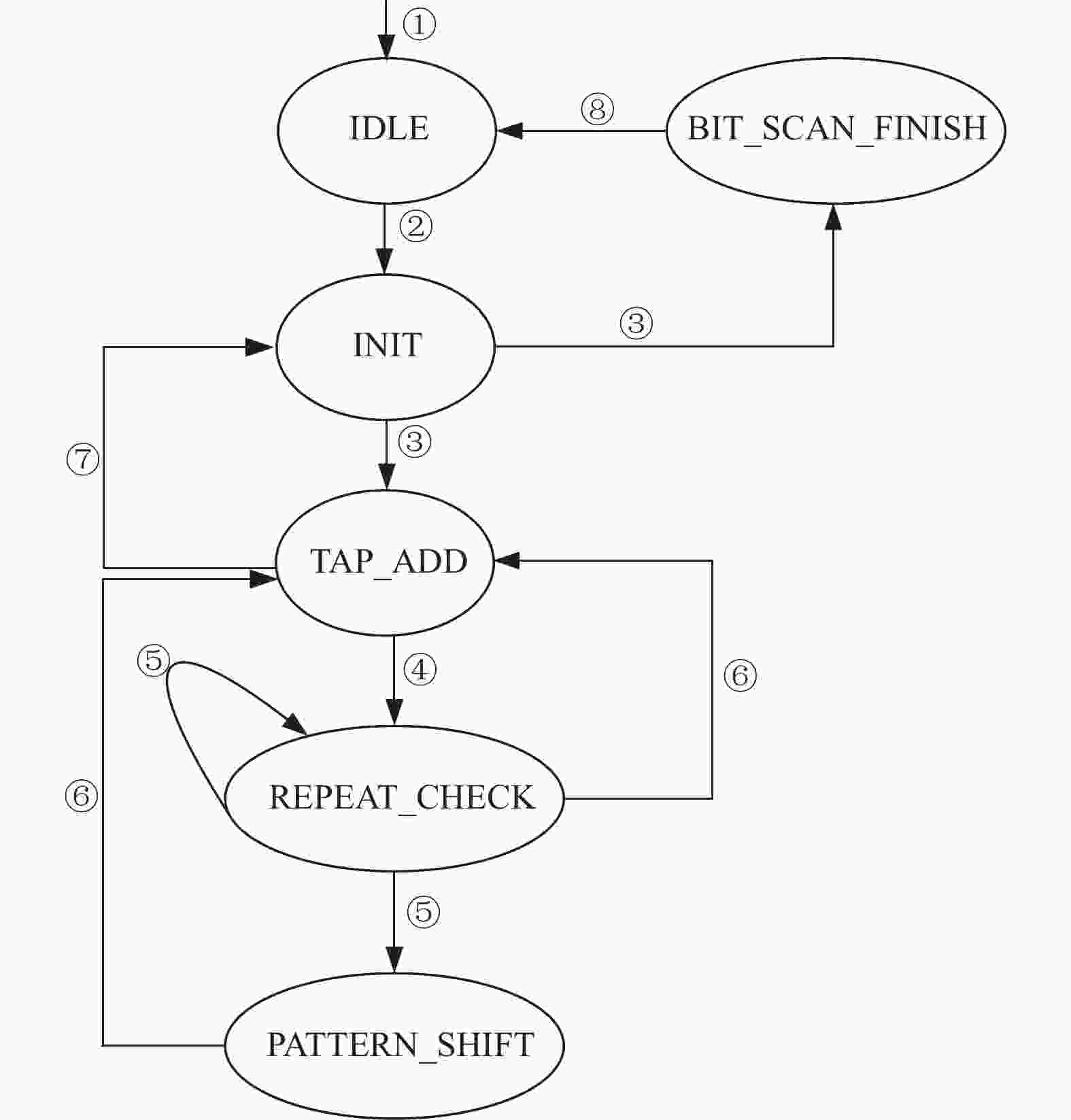

FPGA状态机状态跳转流程图如图6所示。

有限状态机各状态说明:

IDLE:硬件上电后默认状态,进行有限状态机复位,配置测试模式等操作;

INIT:初始状态,进行扫窗起始TAP值(TAP_START)、扫窗结束TAP值(TAP_END)以及扫窗TAP间隔(TAP_GAP)的赋值,以及传输线线号(Lane_num)的判断等操作;

TAP_ADD:对TAP值进行自加,遍历512级TAP值;

REPEAT_CHECK:对正确的PATTERN进行64次比较,以消除亚稳态对比较过程正确性的影响;

PATTERN_SHIFT:对错误的PATTERN进行移位等操作;

BIT_SCAN_FINISH:所有的Lane扫描结束。

状态转移条件说明:

① 软件下发配置TAP_START、TAP_STOP、TAP_GAP等参数,将主从FPGA配置成测试模式,主从FPGA收到RESET信号对系统进行复位;

② 复位完成后,状态机开始工作,从FPGA向主FPGA发送固定码流PATTERN (“0101010110101010”,即0x55AA,该序列周期=16

$ {T_{{\rm{clk}}}} $ ,可以覆盖较大的Delay值,并且“01”“10”翻转频繁,易检测亚稳态);③ n为主从FPGA之间的物理连线数,若Lane_num<n,则跳转至TAP_ADD状态;若Lane_num=n,则跳转至BIT_SCAN_FINISH状态,工作结束;

④ 对DATA_IN施加TAP_START的延迟值,将延迟后的信号分别和初始码流PATTERN进行比较;

⑤ 若比较成功,则跳转至REPEAT_CHECK状态进行多次比较;多次比较成功则认为PATTERN_CORRECT,为稳定的TAP,记录PATTERN的移位值到RAM中。若比较失败,则跳转至PATTERN_SHIFT状态,对码流PATTERN进行移位;若多次比较失败或移位比较失败,则认为PATTERN_ERROR,则为亚稳态区间的TAP,记录“FF”到RAM中;

⑥ 若PATTERN_CORRECT或者PATTERN_ERROR,则对一根Lane进行TAP=TAP+TAP_GAP,跳转至TAP_ADD状态,重复操作;

⑦ 若TAP=TAP_END,则表示一根Lane的TAP遍历完了,Lane_num=Lane_num+1,重复③~⑥的操作;

⑧ 在所有Lane扫描结束后,进入BIT_SCAN_ALLFINISH状态后,FPGA硬件模块将生成一个RAM,提交给PC端软件进行算法处理,并跳转至IDLE状态,等待下一次状态机运转。

-

软件配置流程如图7所示。

软件为FPGA配置测试模式,下发终止TAP值TAP_STOP,起始TAP值TAP_START,TAP步进TAP_GAP等相关控制字(流程图①),在复位完成后,给FPGA下发开始指令(流程图②),等待FPGA的SCAN_ALLFINISH结束标志(流程图③),读取RAM中的扫描结果,根据算法计算出稳定的TAP值,并下发至FPGA(流程图④)。

FPGA同步传输模块会根据软件下发的配置字,生成一个包含稳定TAP信息的RAM,如表1所示。表中每个地址与IODELAY中TAP的映射关系为:

$$\begin{split} &{\rm{TAP}} = \big( {\rm{ADDR}} - \left( {\rm{TAP}}\_{\rm{STOP}} { - {\rm{TAP}}\_{\rm{START}} + 1} \right) \times \\ &\qquad\qquad\quad {\rm{Lane}}\_{\rm{num}} - 1 \big) \times{\rm{TAP}}\_{\rm{GAP}} \end{split} $$ (1) 表 1 RAM存储的扫描结果

Lane编号 TAP值 1 2 3 4 … 10 11 12 … Lane_0 a a FF FF … b b FF … Lane_1 a a a FF … b b FF … Lane_2 a a a a … b FF FF 表1中Lane_num为Lane的编号,内容表示每根Lane的扫窗情况,有具体数值的表示接收信号处于稳定区间,否则置为FF。以数值为

$ a $ 举例,作用该地址下对应的TAP值后,主FPGA接收的信号能和初始码流(55AA)左移位$ a $ 次后对齐。并且$ a $ 和$ b $ 满足以下关系:$$ a+2=b+1\;\;\;\;a < b < {\rm{PATTERN}}\_{\rm{LENGTH}} $$ (2) 式中,

$ {\rm{PATTERN}}\_{\rm{LENGTH}} $ 表示初始码流的周期数。根据以上结果,软件经过算法计算出每根Lane对应的最长稳定区间(即最长的稳定“窗”),假设最长稳定区间的起始地址为$ {\rm{ADDR}}\_{\rm{MIN}} $ ,所对应的TAP值为$ {\rm{TAP}}\_{\rm{MIN}} $ ;终止地址为$ {\rm{ADDR}}\_{\rm{MAX}} $ ,所对应的TAP值为$ {\rm{TAP}}\_{\rm{MAX}} $ ,则有:$$ \begin{split} &{{\rm{TAP}}\_{\rm{num}} = {\rm{TAP}}\_{\rm{STOP}} - {\rm{TAP}}\_{\rm{START}} + 1} \\ &\quad {{\rm{TAP}}\_{\rm{MIN}} = \left( {\left( {{\rm{ADDR}}\_{\rm{MIN}} - {\rm{TAP}}\_{\rm{num}}} \right)} \times \right.} \\ &\qquad\quad {\left. { {\rm{Lane}}\_{\rm{num}} - 1} \right) \times {\rm{TAP}}\_{\rm{GAP}}} \\ &\quad {{\rm{TAP}}\_{\rm{MAX}} = \left( {\left( {{\rm{ADDR}}\_{\rm{MAX}} - {\rm{TAP}}\_{\rm{num}}} \right)} \times\right.} \\ &\qquad\quad {\left. { {\rm{Lane}}\_{\rm{num}} - 1} \right) \times {\rm{TAP}}\_{\rm{GAP}}} \end{split} $$ (3) 由图3分析可知,TAP_MIN和TAP_MAX为两个边界条件,取二者的中间值即为最稳定的TAP_IN值:

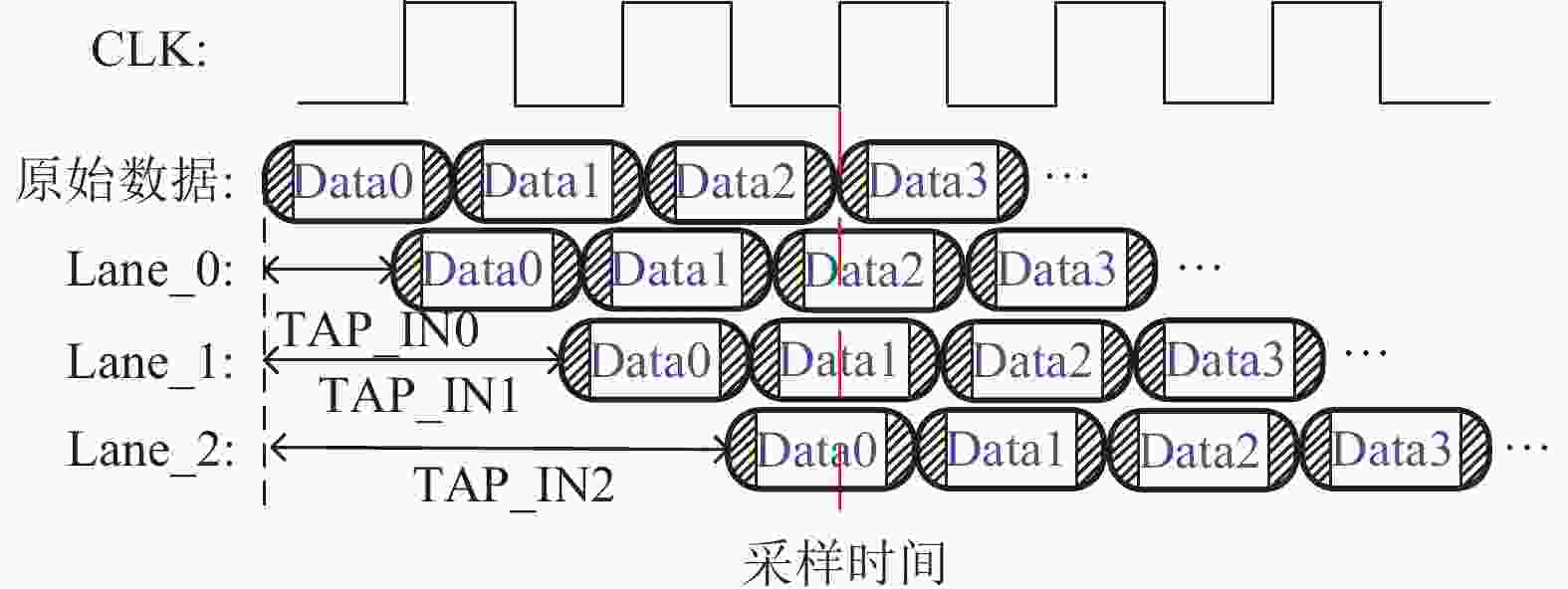

$$ {\rm{TAP}}\_{\rm{IN}} = \left( {{\rm{TAP}}\_{\rm{MAX}} - {\rm{TAP}}\_{\rm{MIN}}} \right)/2 $$ (4) 在完成高速信号稳定传输设计后,延时信号可能出现如图8情况,即不同Lane的信号采样虽然没有出现亚稳态,但是Lane_1相对于Lane_0滞后一个时钟周期,Lane_2相对于Lane_1滞后一个时钟周期,因此需要提出一种校正方法对不同Lane进行同步。

对于主FPGA和从FPGA之间的信号传输,主FPGA接收的数据必须与从FPGA发送的数据一致,并且它们的相对位置不能被打破。即在测试模式下,从FPGA发送测试序列(55AA),主FPGA接收的数据也应该是测试序列(55AA)。

假设主FPGA接收的信号能和测试序列(55AA)移位

$ a $ 次后对齐,此Lane则需要延迟的时钟周期数为:$$ {T_{{\text{data}}}} = \left( {{\rm{PATTERN}}\_{\rm{LENGTH}} - a} \right) {T_{{\rm{clk}}}} $$ (5) 对于主从FPGA间控制信号传输而言,处理方法同数据信号即可。

最后完成高速信号同步传输设计,如图9所示。

-

为了验证本文提出的FPGA间高速信号同步传输方法的有效性,将本方法在自制DSO中进行实现。在本次验证中,信号发生器为UNI-T UTG7122B,用于产生正弦信号;DSO使用双通道5GSPS采样模式,验证平台如图10所示。

-

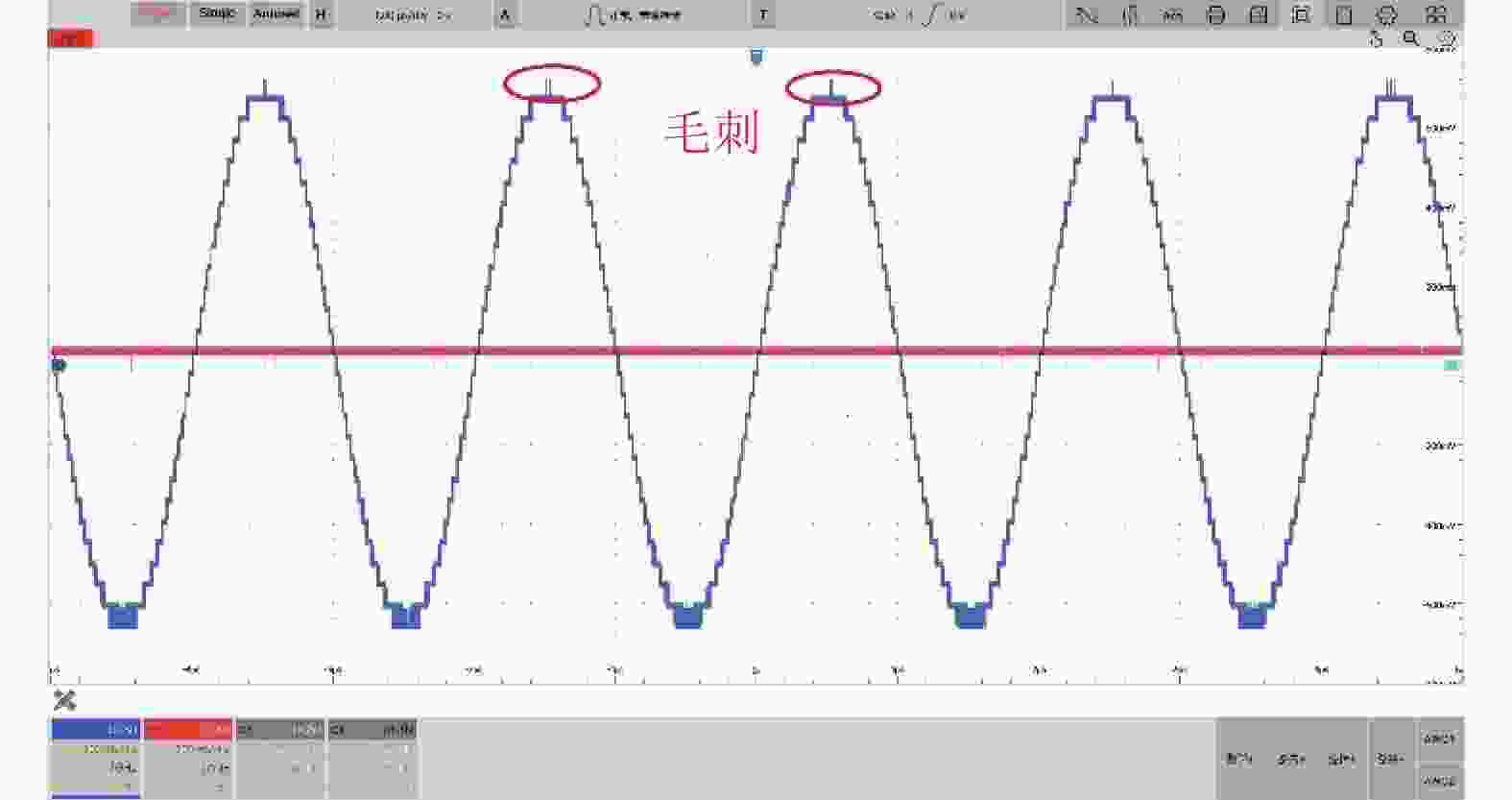

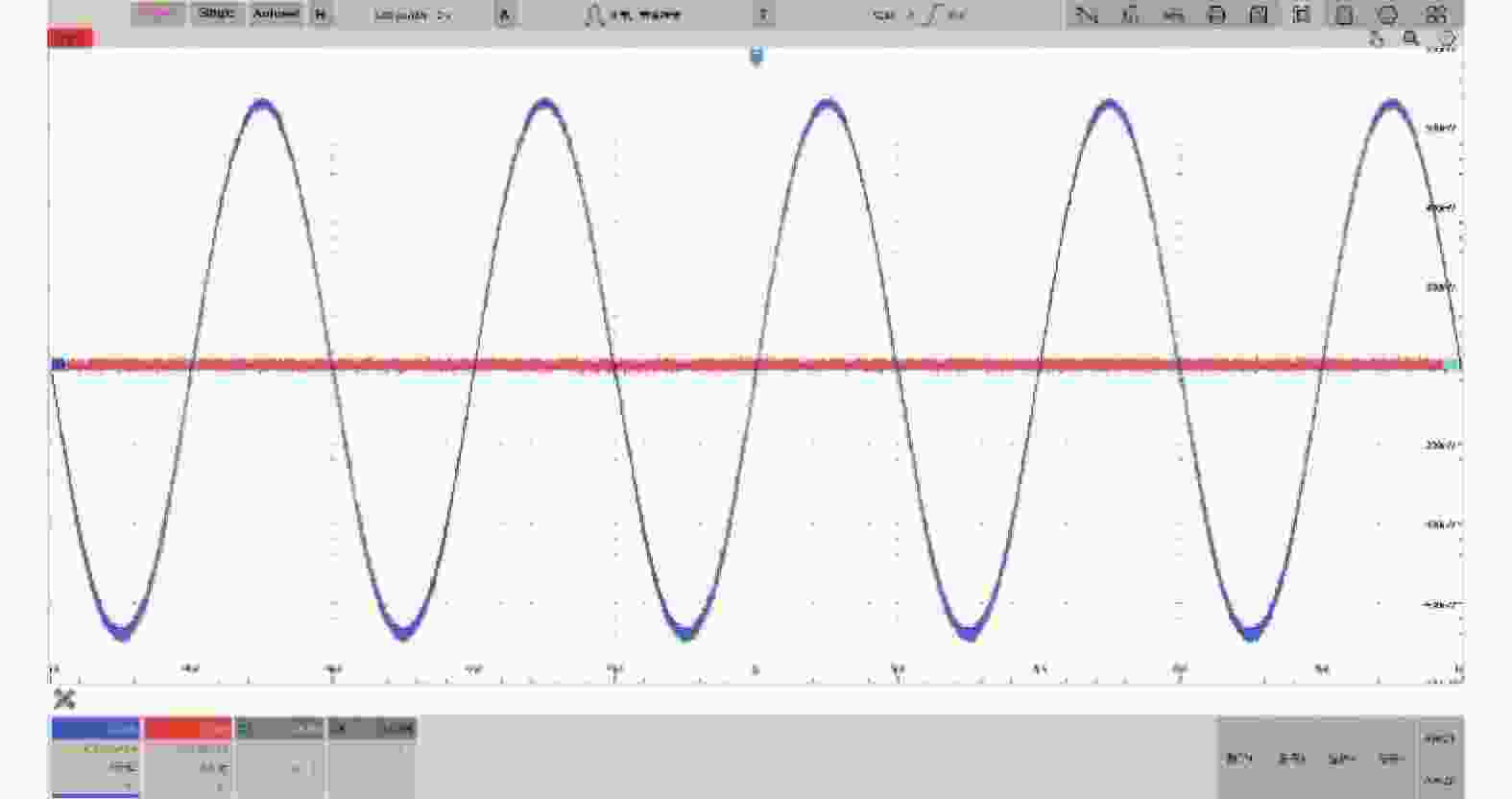

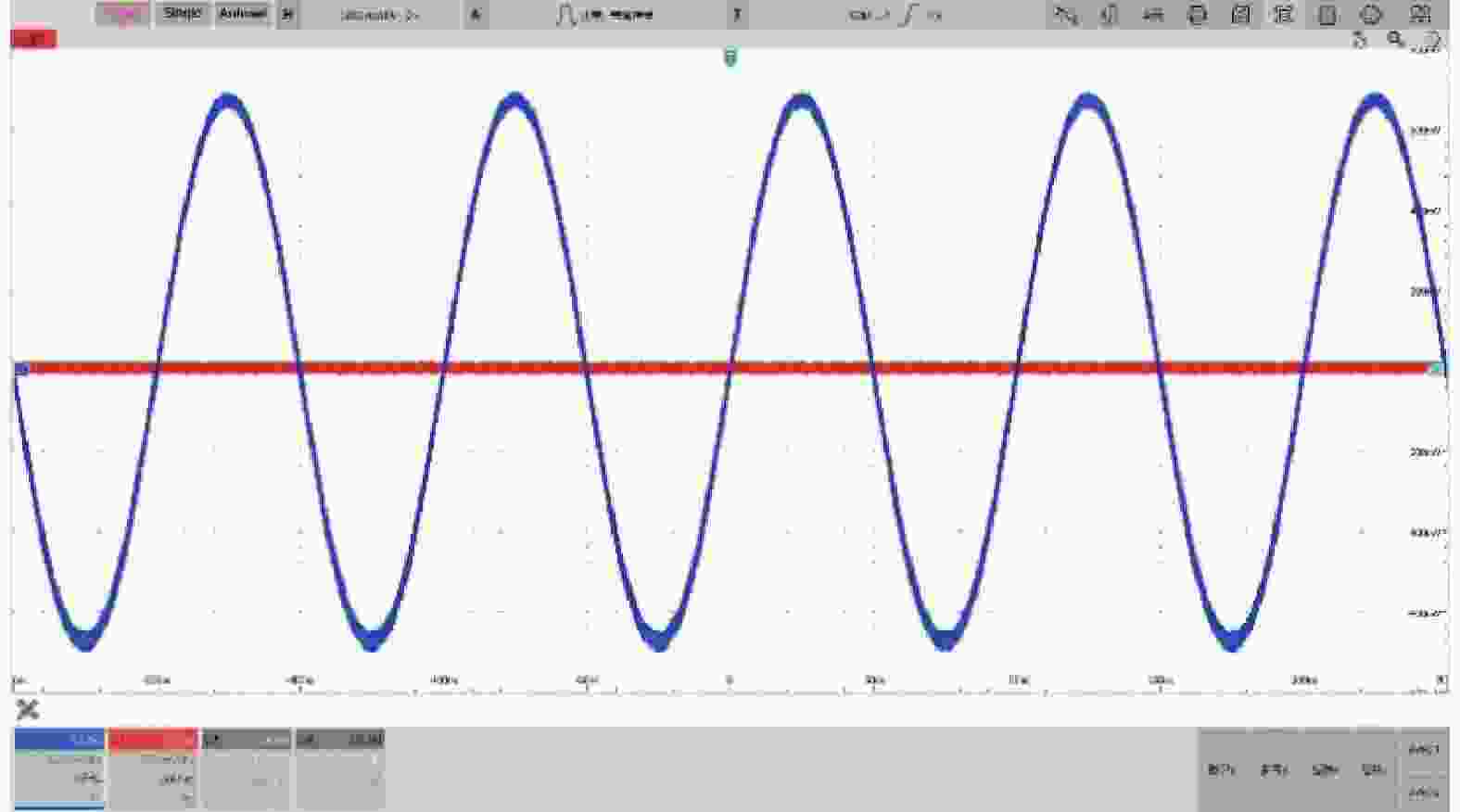

自制DSO通道1输入频率为500 kHz的正弦波信号,如果不进行数据信号同步传输设计,在自制DSO中的反映现象如图11所示。数据在传输过程中会有某个比特位出现亚稳态,波形显示会有毛刺;且波形显示不平滑,呈现阶梯状。

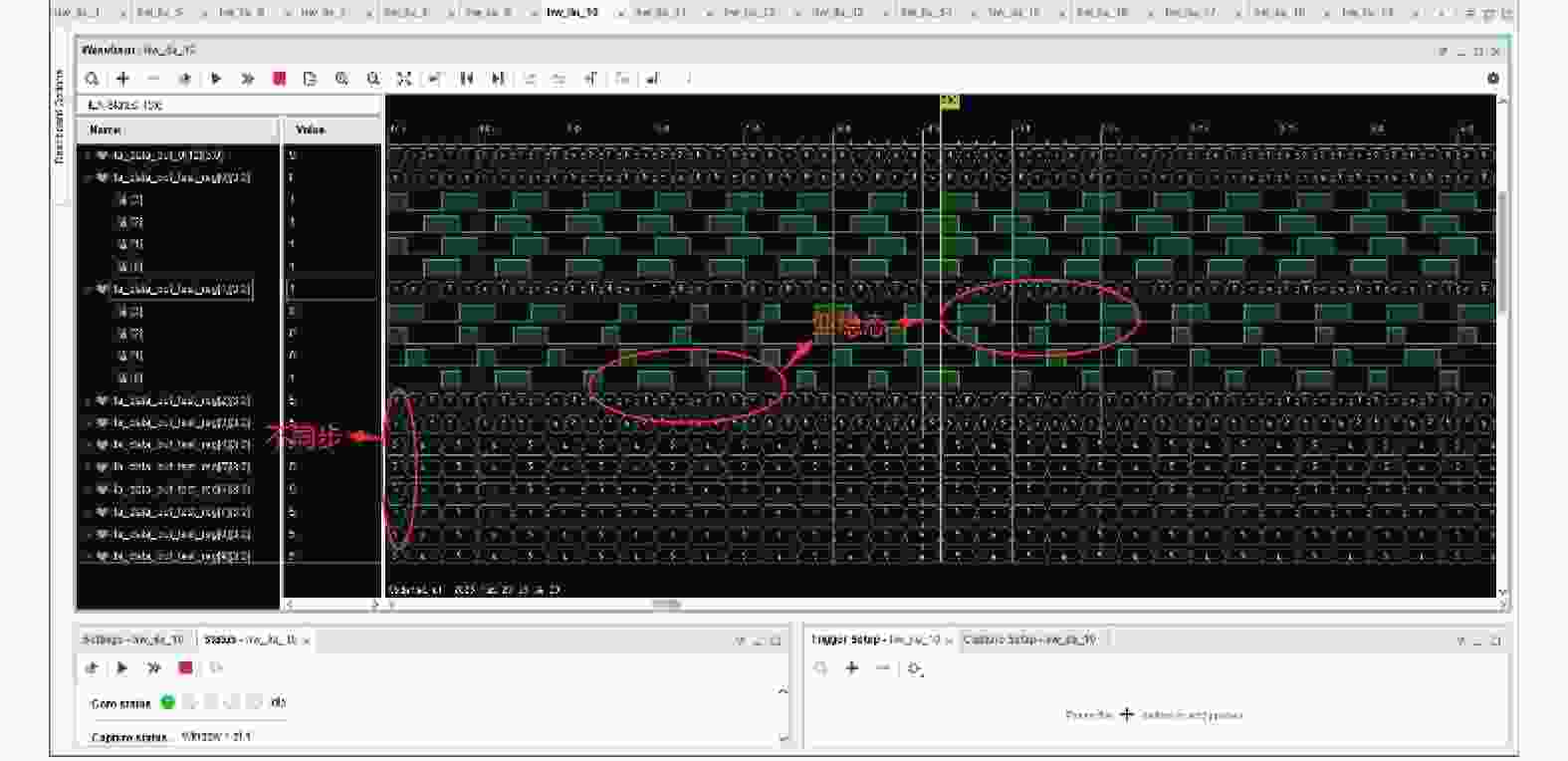

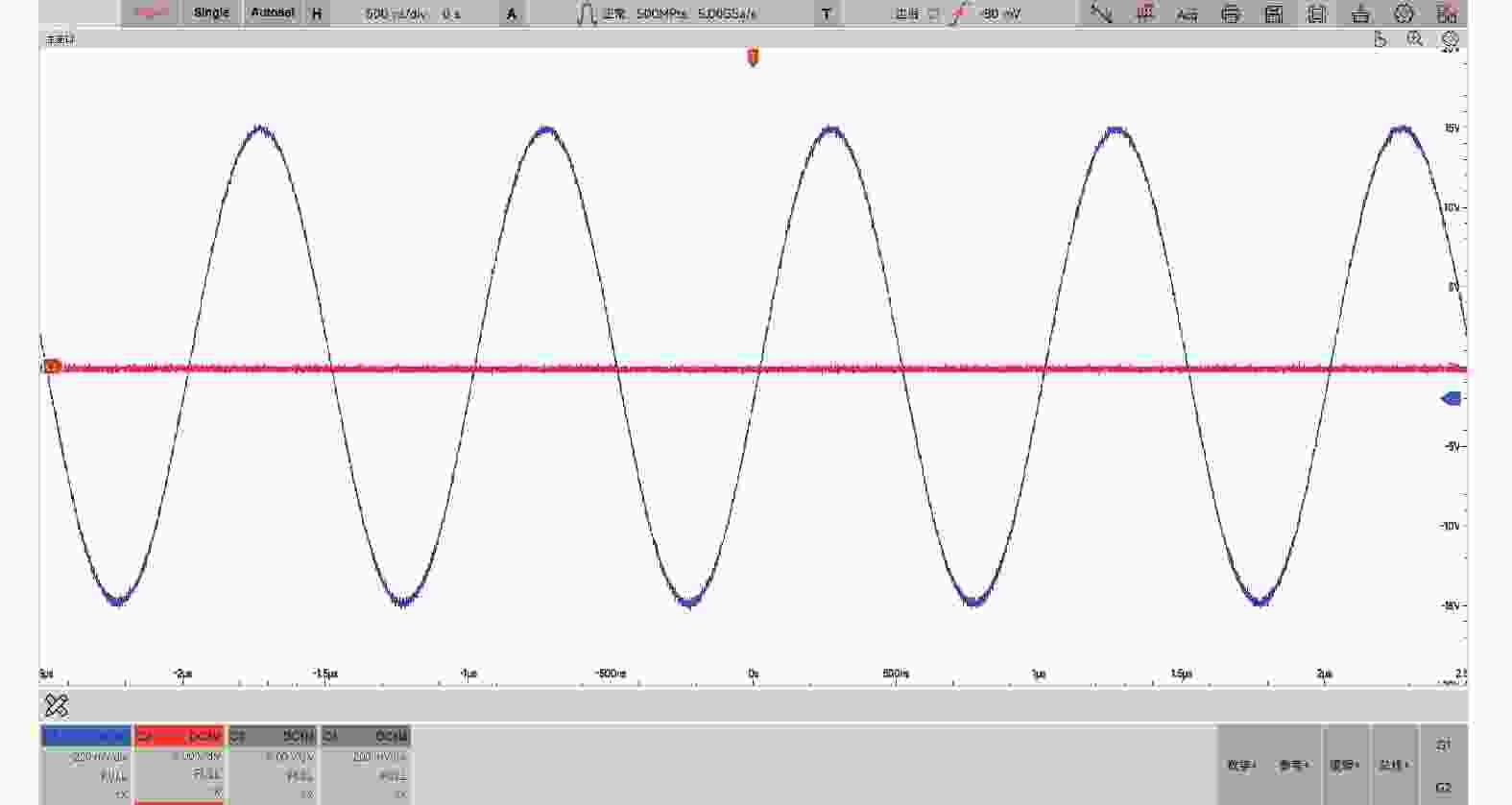

将FPGA配置为测试模式(即发送55AA测试序列),使用VIVADO的ILA工具抓取接收端测试数据。

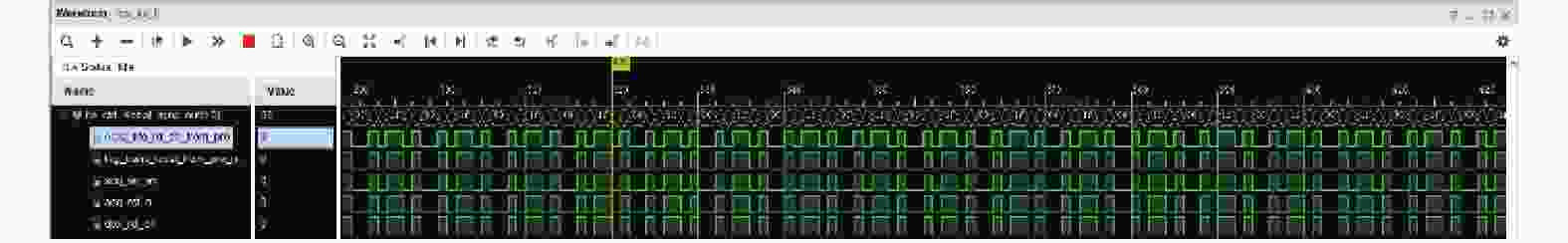

图12所示接收端测试数据会出现亚稳态,同时不同数据Lane之间会有不同步的现象。

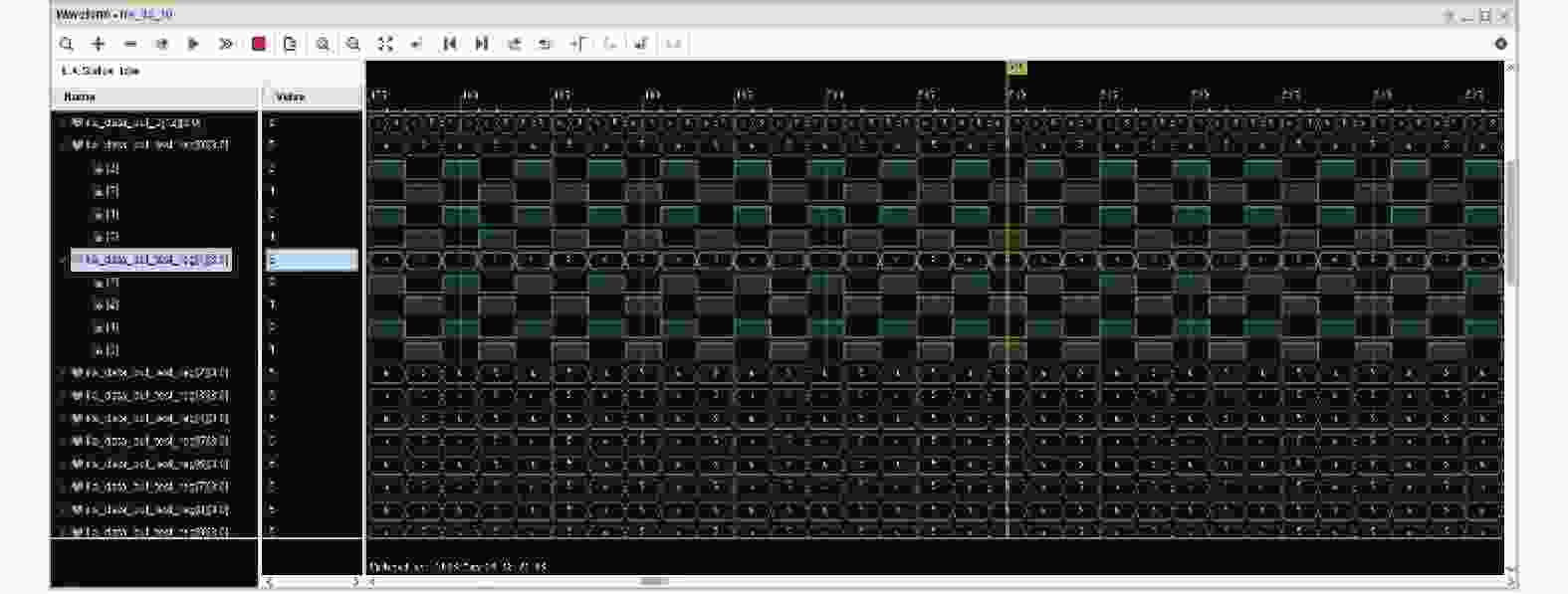

在进行数据信号同步传输设计后,测试模式下使用Vivado的ILA工具抓取测试数据,接收端测试数据无亚稳态,不同数据Lane之间均同步,接收的数据为55AA,如图13所示。

切换为正常工作模式,500 kHz频率的正弦波波形的显示正常且光滑无毛刺,如图14所示,这和ILA的抓取结果一致。

为了进一步验证数据传输的同步性,示波器输入1 MHz的正弦波,波形仍然是光滑无毛刺,如图15所示,因此实现了数据信号的同步传输。

-

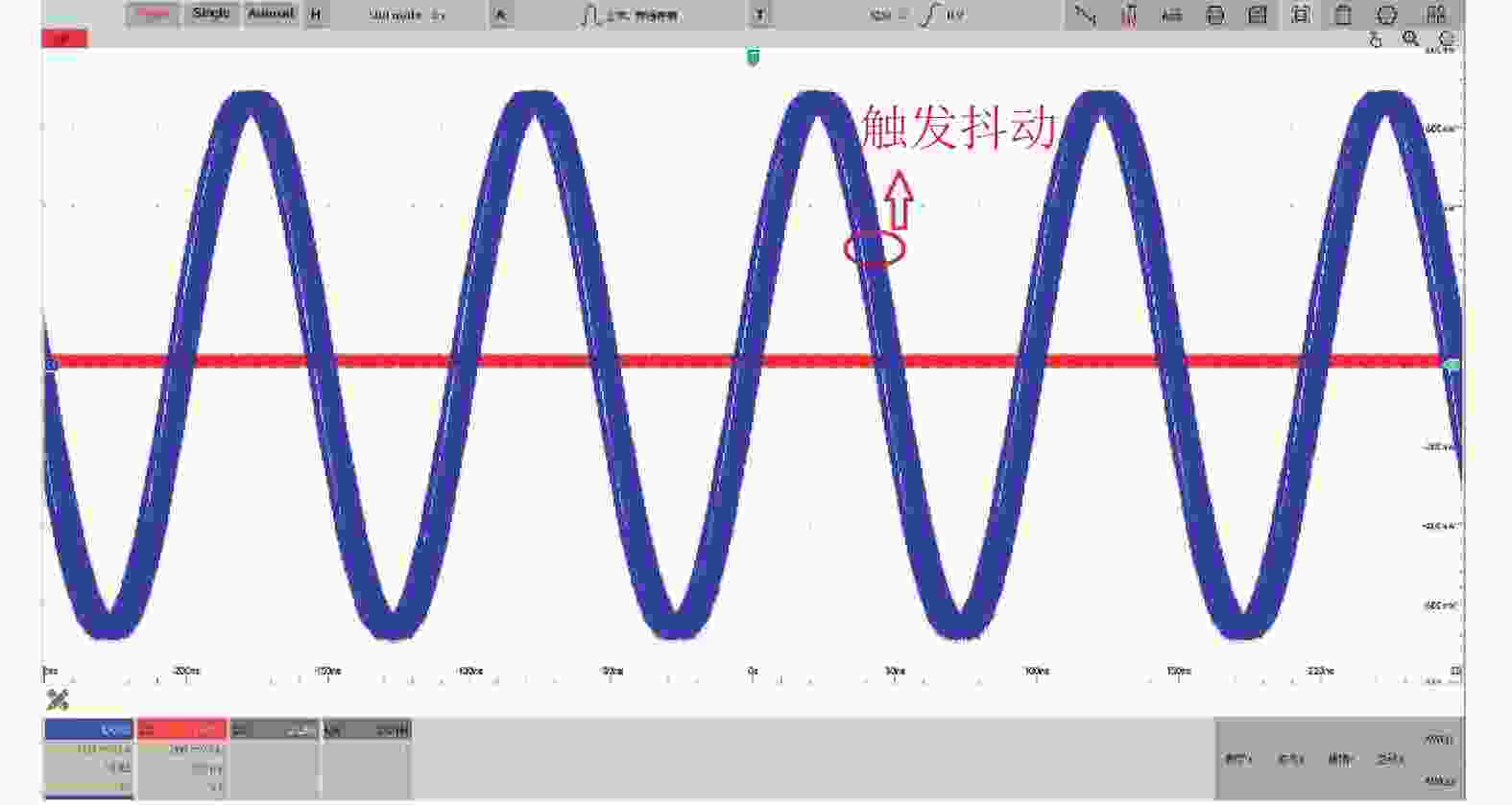

在自制DSO中,控制信号决定着DSO触发的稳定性。自制DSO通道1输入频率为10 MHz的正弦波信号,如果不进行控制信号同步传输设计,在自制DSO中的反映现象如图16所示。打开DSO无限余辉显示模式,多次重复捕捉波形,波形不能稳定触发,会有剧烈的晃动。

同4.1节方法,将FPGA配置为测试模式,使用VIVADO的ILA工具抓取接收端测试数据。

如图17所示接收端测试数据也会出现亚稳态,同时不同控制Lane之间会有不同步的现象。在进行控制信号同步传输设计后,每条控制Lane传输稳定,且多条Lane之间同步,如图18所示。

切换为工作正常模式,打开DSO无限余辉显示模式,波形稳定触发,如图19所示。

-

论文针对FPGA间高速信号传输不同步的问题,提出一种基于FPGA信号传输同步自校正的方法,利用IDELAYE单元实现从FPGA与主FPGA之间的高速信号同步传输,补偿算法实现多FPGA间的高速信号同步传输。

High-Speed Signal Transmission Synchronization Method Between FPGAs in Digital Oscilloscopes

-

摘要: 数据采集系统是数字示波器(DSO)的核心组成单元,随着示波器带宽采样率的逐步提升,单片模数转换器(ADC)+现场可编辑门控阵列(FPGA)的架构难以满足超高速以及多通道的应用场景,因此,高端示波器中数据采集系统普遍采用“主从”FPGA控制架构。在该架构下,多个FPGA之间信号的同步传输是实现采集系统的同步和精确采集的重要前提。针对多FPGA板卡之间的信号同步传输问题,提出了一种FPGA之间高速信号同步传输的方法,借助FPGA的IODELAY单元,通过测试数据训练找到最稳定的同步传输区间,实现多FPGA之间的同步传输。在自研的数字示波器上的实验表明,该方法能够有效实现FPGA之间高速信号的同步传输。Abstract: The data acquisition system is the core component of Digital Storage Oscilloscopes (DSO). With the gradual increase in the bandwidth and sampling rate of oscilloscopes, the single-chip Analog to Digital Converter (ADC) + Field Programmable Gate Array (FPGA) architecture is difficult to meet ultra-high-speed and multi-channel application scenarios. Therefore, data acquisition systems in high-end oscilloscopes generally adopt a 'Master-Slave' FPGA control architecture. Under this architecture, the synchronous transmission of signals between multiple FPGAs is an important prerequisite for achieving synchronization and accurate acquisition of the acquisition system. This paper proposes a method for high-speed signal synchronous transmission between FPGAs to solve the problem of signal synchronization transmission between multiple FPGA boards. With help of FPGA's IODELAY unit, the most stable synchronization transmission interval is found through test data training, and synchronization transmission between multiple FPGAs is realized. Experiments on a domestic digital oscilloscope shows that this method can effectively achieve synchronous transmission of high-speed signals between FPGAs.

-

表 1 RAM存储的扫描结果

Lane编号 TAP值 1 2 3 4 … 10 11 12 … Lane_0 a a FF FF … b b FF … Lane_1 a a a FF … b b FF … Lane_2 a a a a … b FF FF -

[1] 姜子威. 超高速数据采集系统中多器件同步自校正方法研究与实现[D]. 成都: 电子科技大学, 2019. JIANG Z W. Research and implementation of synchronous self-tuning method for multi-device in ultra-high speed data acquisition system[D]. Chengdu: University of Electronic Science and Technology of China, 2019. [2] 孙凯. 20GSPS数字示波器的数据采集模块硬件设计[D]. 成都: 电子科技大学, 2018. SUN K. Hardware design of data acquisition system for 20GSPS digital oscilloscope[D]. Chengdu: University of Electronic Science and Technology of China, 2018. [3] 张华高, 陈岚. DDR源同步接口的设计与时序约束方法[J]. 计算机工程与设计, 2008(7): 1600-1602. ZHANG H G, CHEN L. Design and constraint method of DDR source synchronous interface[J]. Computer Engineering and Design, 2008(7): 1600-1602. [4] 李海涛, 李斌康, 阮林波, 等. 高速ADC采样数据接收缓存系统研究[J]. 自动化仪表, 2020, 41(8): 42-45. LI H T, LI B K, RUAN L B, et al. Research on highspeed ADC sampling data receiving and buffer system[J]. Process Automation Instrumentation, 2020, 41(8): 42-45. [5] 文科, 朱正, 马敏舒. 低成本SerDes在数据采集中的方案设计与应用[J]. 电子技术应用, 2020, 46(8): 88-91. WEN K, ZHU Z, MA M S. Design and application of low-cost SerDes in data acquisition[J]. Application of Electronic Technique, 2020, 46(8): 88-91. [6] IAN B. Synchronize multiple ADCs With JESD204B[M]. [S.l.]: Analog Devices Inc., 2013. [7] 张清亮. 基于FPGA高速通用串行接口的设计与应用[D]. 西安: 西安电子科技大学, 2017. ZHANG Q L. Design and application of high-speed general serial interface based on FPGA[D]. Xi’an: Xidian University, 2017. [8] 于晅, 肇云波. 基于FPGA高速数据采集的解决方案[J]. 现代电子技术, 2007(5): 145-148. doi: 10.3969/j.issn.1004-373X.2007.05.051 YU X, ZHAO Y B. High-speed data acquisition based on FPGA[J]. Modern Electronics Technique, 2007(5): 145-148. doi: 10.3969/j.issn.1004-373X.2007.05.051 [9] 张静宇, 楼大年. 一种基于FPGA的多通道数据传输自动同步的方法[C]//第十八届卫星通信学术年会. 北京: [s.n.], 2022: 171-176. ZHANG J Y, LOU D N. An automatic synchronization method of multi-channel data transmission for FPGA[C]//Proceedings of the 18th Annual Conference on Satellite Communication. Beijing: [s.n.], 2022: 171-176. [10] 刘丽格, 李天保, 石鑫刚. 一种板间高速传输系统的设计与实现[J]. 无线电通信技术, 2011, 37(4): 53-55. doi: 10.3969/j.issn.1003-3114.2011.04.017 LIU L G, LI T B, SHI X G. Design and implementation of a high-speed board-to-board transmission system[J]. Radio Communications Technology, 2011, 37(4): 53-55. doi: 10.3969/j.issn.1003-3114.2011.04.017 [11] 李优杏, 周先敏, 吕红军. 基于FPGA的SERDES接口设计与实现[J]. 中国通信学会第五届学术年会. 北京: [s.n.], 2008: 11-14. LI Y X, ZHOU X M, LYU H J. Design and realization of serdes interface base on FPGA[J]. Proceedings of the fifth Annual Conference of the Chinese Society of Communications. Beijing: [s.n.], 2008: 11-14. -

ISSN

ISSN

下载:

下载: