-

集成电路技术的进步使得传统的基于总线结构的片上通信方式面临着功耗、性能、时延和可靠性等诸多方面的问题,已经逐渐不能满足片上多模块间通信的需要。为了克服总线结构的不足,人们将通信网络的思想运用到芯片通信结构的设计上,提出了片上网络(NoC)[1]。为了解决时钟树设计的难题,降低时钟偏斜,NoC通常使用本地同步全局异步(GALS)的互连方法。在这种互连结构中,系统被分为多个功能模块,每一个功能模块都有自己的工作时钟[2]。

NoC的测试可以分为3个主要方面:资源核的测试[3]、路由的测试[4-6]以及路由间互连链路[7-9]的测试,本文关注NoC互连线的测试问题。在当前先进半导体生产工艺下,集成电路片上延时的主要来源已经从门延迟变为互连线延迟。工艺误差以及串扰等问题又使得互连线上的延迟存在较大不确定性。GALS结构对延迟匹配的要求较高,很容易因为线路的延迟引起电路故障[10]。延迟故障通常只在电路工作在正常工作频率时表现出来,若测试时电路的工作频率低于正常工作频率,延迟故障不会被发现。全速测试(at-speed test)面临着测试矢量生成以及测试应用等多方面的问题[11],内建自测试(BIST)很好地解决了这些问题[12-13]。文献[14-15]研究了由串扰和噪声引起的互连线故障,并都提出了相应的测试硬件电路。文献[16]提出了另一种BIST解决方案,并分析了测试结果。但所有这些都是针对同步电路的测试方法,不能被应用到异步电路的测试中,本文提出了一种针对片上跨时钟域互连线的全速测试方法。

-

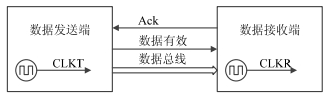

本文采用握手协议作为异步设计通讯的方法,该协议通过两个控制信号的配合完成数据的传输任务。图 1所示是一个基于握手协议实现的NoC节点间通信模型。包含一个应答信号ACK,一个数据有效信号,以及一组数据总线。图 1中的数据发送端和数据接收端即是相邻两个路由器的一个数据通道。两个路由器工作在不同的时钟信号下,CLKT信号和CLKR信号分别为数据发送端和数据接收端的时钟信号。

数据接收端接收到数据有效信号之后,其内部电路产生一个数据的读取脉冲,数据接收端的数据存储单元在该脉冲信号的上升沿或下降沿将数据总线中的数据缓存,完成数据的读取操作。如图 2所示,在T1时间,数据有效信号到达接收端,但由于数据总线上存在较大的延迟,数据信号在T3(T1< T3)时间才到达接收端。在T2时刻(T1<T2<T3),数据接收端产生读取脉冲信号,并在该信号的上升沿读取数据总线。但由于此时数据总线上新的数据还没有到达接收端,接收端采集到的是数据总线上原有的旧数据。

-

为了准确反映数据有效信号与数据信号间的时序关系,消除异步时钟不确定性所带来的问题,将数据有效信号作为数据接收端BIST中数据采样寄存器的时钟信号。如图 3所示,数据有效信号data_en和8位数据总线dataout同时从发送端出发,其中data_en到达接收端的data_en_r做为数据寄存器的时钟信号,dataout到达接收端的作为寄存器组tdata_buf的数据输入端。在数据有效信号的上升沿,数据采集寄存器将数据总线上的数据锁存,再将该数据与数据接收端ATPG单元所生成的数据做比较。如果数据一致,则说明在数据有效信号到达之前,数据总线上的数据已经到达,本次测试未发现延迟故障。相反,若采样的数据与预期数据不同,则说明在数据有效信号到达时,数据总线上的数据没有完全到达接收端,系统存在延时故障。另外,为了使数据总线上的所有位在测试时都发生跳变,首先将测试数据取反后置入数据总线。

测试电路结构如图 4所示,相邻路由节点之间通过四相位握手协议进行通信。当测试使能信号有效时,BIST模块获得数据链路的控制权,系统进入测试状态。然后数据发送端与数据接收端的BIST电路通过握手协议,在数据链路中传输测试数据,对数据链路进行延迟测试,并将测试结果输出。

BIST电路主要由3部分组成,分别为发送电路(sender)、接收电路(receiver)和测试矢量生成模块(ATPG)。在下面的内容中对这3部分进行分别讨论。

-

由于串扰以及工艺偏差的影响,当数据线上传输的数据不同时,其延迟也相同。为了整个测试的完备性,需要验证在所有情况下,系统都不存在延迟故障。而利用传统的方法,对于N位数据总线,需要进行2N次测试。当N值较大时,会极大地增加测试时间和测试成本。为了解决这一问题,在ATPG电路中实现最大入侵错误(maximum aggressor fault,MAF)串扰故障模型来最大化串扰对延迟的影响[17]。通过实现MAF串扰故障模型,每一个测试向量保证数据总线中的某一位在传输上升或下降信号时的延迟被最大化,完整的上升信号与下降信号传输测试结果可以完全反映该位上是否存在延迟故障。因此对于N位数据总线,只需要进行2N次测试,就可以完成对互连导线延迟故障的诊断,并且极大地提高了测试的速度和障覆盖率,减少了测试成本。

ATPG模块通过使用状态机控制一个移位寄存器实现,图 5、图 6分别为其工作流程图和电路接口定义。clk和rst分别为电路的时钟和复位信号,out_en为数据有效信号,rd_en为数据读取信号,start为测试开始信号,pattern[7:0]为数据输出总线。当测试开始时,BIST电路向ATPG发送一个start脉冲,ATPG开始进行初始化进程,当数据准备好后,它将out_en信号拉高,并将数据置入pattern[7:0]。每当BIST电路需要一个测试数据时,它向ATPG发送一个rd_en脉冲,同时读取pattern[7:0]上的数据。ATPG在接收到rd_en信号后,将下一个数据置入pattern[7:0]。所有测试向量输出完毕后,ATPG将out_en信号拉低,通知BIST电路测试结束。

-

数据发送端的BIST电路实现数据有效信号和数据总线的控制,并接收来自于数据接收端的ACK信号。为了实现MAF模型,需要使所有数据信号线上的电平都发生跳变。在进行测试时,首先将测试数据逐位取反后置入数据总线,然后再将测试数据置入数据总线,这样保证了所有数据线上都发生信号跳变。

数据发送端的BIST电路由一个状态机实现,图 7为发送端BIST电路的接口定义。其中clk和rst分别为电路的时钟和复位信号,out_en、start、rd_en、pattern(7:0)是和ATPG通信的信号,用以完成ATPG初始化和测试向量读取。data_en为数据发送端数据有效信号,dataout(7:0)为8位数据总线,Ack为数据接收端响应信号,共同组成了一个四相位握手协议的数据与控制信号,也是本文的测试目标。

图 8为电路的状态转换图,状态机各状态完成的任务如下所述:

1) Idle:初始状态,初始化控制信号以及数据总线,等待测试使能信号test_en。当test_en有效以后,进入InitATPG状态。

2) InitATPG:向ATPG发送start信号,初始化ATPG,并等待ATPG初始化完成。当ATPG单元的out_en信号有效后,进入WaitAckH状态。

3) WaitAckH:等待数据接收端的Ack信号响应。若Ack为高电平,则说明数据接收端BIST初始化结束或上一次测试过程结束,进入GetPattern状态,读取测试数据。

4) GetPattern:先判断out_en是否有效,若out_en有效,则产生一个rd_en脉冲信号,同时读取ATPG数据输出端的数据并缓存,转入DataOut状态。若out_en无效,则说明测试已经结束,转入Idle状态。

5) DataOut:将Getpattern状态中缓存的数据取反后送入数据总线,同时置data_en信号为低电平,转入WaitAckL状态,等待数据接收端响应。

6) WaitAckL:等待数据接收端响应,若Ack=0,则说明取反后的测试数据已经成功到达接收端,数据总线已经保持有测试数据取反后的数据,转入Test状态进行延迟故障的测试。

7) Test:进行延迟故障的测试,将从ATPG单元上采样的数据送入数据总线,同时使data_en=1,然后转入WaitAckH状态等待数据接收端BIST响应。

-

数据接收端的BIST电路与数据发送端电路相互配合,共同完成延迟故障测试任务。它对发送端的数据有效信号做出响应,采集数据总线上的数据信号,将该数据与ATPG单元产生的数据相比较,若一致,则说明没有延迟故障。否则,输出故障信息。

图 9所示为电路的接口定义,其中clk和rst分别为电路的时钟和复位信号,start、rd_en、out_en和pattern(7:0)用来和ATPG进行通信,date_en、Ack和pattern(7:0)构成四相位握手协议和数据发送端相配合,faultflag为故障信息数据端,每一位代表一位数据信号上是否有延迟故障。如若faultflag的值为10000001,则说明最高位与最低位信号线上存在延迟故障,其他数据位不存在延迟故障。

图 10所示为电路的状态转换图,电路的具体工作流程及各状态之间的跳转关系如下所述:

1) Idle:初始状态,对BIST电路的输出信号以及内部寄存器做初始化操作,等待测试使能信号test_en。当test_en信号有效时,系统进入测试状态,状态机进入InitATPG状态。

2) InitATPG:输出控制信号对ATPG进行初始化操作,当ATPG的数据输出使能信号out_en有效,则初始化完成,进入GetPattern状态,读取测试向量。

3) GetPattern:首先侦测out_en信号的值,若out_en信号为高电平,则产生一个rd_en脉冲,同时读取ATPG数据输出端的数据,存入pattern_buf,然后转入SampleData状态。若out_en信号为低电平,则说明该测试循环已经结束,转入Idle状态。

4) SampleData:当data_en为低电平时,每个时钟周期读取一次数据总线,并将读取到的数据缓存到data_buf中,比较data_buf与pattern_buf的值,若data_buf=~pattern_buf,将Ack信号置为低电平以响应数据发送端,通知发送端可以进行延迟故障测试。进入WaitDataEn状态。

5) WaitDataEn:当Data_en信号为高电平时,将pattern_buf与tdata_buf(tdata_buf为Data_en信号上升沿采样的数据)上的数据进行比较,如果一致,那么本次测试没有发现延迟故障,否则将错误信息通faultflag输出,进入GetPattern状态进行下一次测试。

-

利用Verilog语言,对上述BIST电路结构与ATPG模块进行RTL级建模,然后利用Mentor Modelsim软件对电路进行仿真,以验证电路的时序以及功能是否正确。将各模块互连,组成如图 11所示的测试系统,Sender为数据发送端BIST电路,Receiver为数据接收端BIST电路,tpgen为ATPG模块。DelayModule为延迟模块,利用该模块调节date_en和dataout上的延迟。为了便于观察,隐藏了电路中信号变化了细节,只给出了数据接收端的data_en信号、dataout信号以及电路的故障输出faultflag。

通过对电路的建模及仿真,可以验证本文的延迟故障测试电路以及测试方法的正确性,可以快速有效地发现互连导线上所存在的延迟故障。

图 12为电路的仿真波形图。从图中可以看出,dataout的某些信号线上存在较大延迟。此时,系统存在延迟故障,faultflag的输出应该是有延迟故障的对应位为1,其他位为0。图中粗竖线位置为data_en上升沿到达的时间,此时dataout[7]的上升沿以及dataout[6]、dataout[4]、dataout[3]、dataout[1]的下降沿已经到达,不存在延迟故障;dataout[5]、dataout[2]和dataout[0]的下降沿未到达,存在延迟故障。faultflag的输出为00100101B,正确反映了该延迟故障。

-

硬件实现采用Digilent Nexys2 FPGA开发板,该开发搭载一块Xilinx Spartan3E(XC3S500E) FPGA芯片,图 13为开发板上实现的测试电路的结构图。其中,Sender为数据发送端BIST电路;Receiver为数据接收端BIST电路,故障信息输出直接驱动8位LED,通过LED的亮灭指示相应的互连导线上是否存在延迟故障;tpgen_r和tpgen_s分别为Sender和Receiver的ATPG模块;delayModule为数据链路延迟调制模块,通过它设置数据链路的延迟;Test_db完成test_en信号输入的去抖动,test_en信号由开发板上的按键开关产生;seg7为7段数码管的驱动电路,它根据Sender和Receiver的信号输出判断测试电路的当前状态,并将其显示在4位7段数码管上,当测试完成时,数码管上显示done字样;ClkModule为时钟生成模块,它由两个数字时钟管理单元(digital clock management,DCM)组成,对板上50 MHz晶振产生的时钟信号进行倍频与分频,产生测试电路的工作时钟。

完成了电路的实现后,可以利用Xilinx ISE提供的时序分析工具提取出dataout和data_en信号上的延迟,如表 1所示,判断电路是否存在延迟故障,以及所存在的延迟故障类型。通过与FPGA上的运行结果相比较,可知测试电路的运行结果是否正确。

表 1 各链路上延迟数值

From To 延迟/ns dataout_2 tdata_buf_2 8.56 dataout_5 tdata_buf_5 8.06 dataout_7 tdata_buf_7 7.81 data_en data_en_r 6.44 dataout_6 tdata_buf_6 5.04 dataout_3 tdata_buf_3 4.89 dataout_1 tdata_buf_1 4.55 dataout_0 tdata_buf_0 4.30 dataout_4 tdata_buf_4 3.19 将设计实现后的配置文件下载到FPGA中运行,所得结果如图 14所示。LED灯右起第2位、第5位、第7位亮,其他位不亮,表明第2位、第5位、第7位存在延迟故障,与表 1中数据完全相符。

BIST测试需要在系统中添加额外的硬件结构,会占用芯片上有限的资源,所以,需要严格控制BIST电路的资源占用。表 2为本文设计的BIST电路在FPGA中实现时所占用触发器以及LUT的数量。从表中数据可以看出,只需要98个触发器与152个4输入LUT就可以实现本论文中所提出的的测试电路,片上逻辑资源占用较少。

表 2 BIST电路逻辑资源消耗

已用 可用 利用率/% 触发器 98 9 312 1 LUT 152 9 312 1 -

对高密度、高工作频率的片上网络的测试是一项十分重要却又十分困难的工作。在深亚微米工艺条件下,如延迟故障等多种电路故障只有当电路工作在正常操作模式下才会表现出来。本文采用异步通信中常用的四相位握手协议,建立了延迟故障测试模型。提出了一种针对NoC节点间互连线延迟故障的BIST测试方法,设计了相应的测试电路,该电路可以通过在数据发送端与数据接收端之间进行数据传输,完成NoC节点间互连导线延迟测试的任务;设计了专用的ATPG模块用以生成测试数据,该ATPG模块可以实现MAF模型,从而最大化了串扰对互连线上延迟的影响;利用Verilog语言编写代码,完成了测试电路与ATPG模块的RTL级建模,并利用Modelsim软件进行仿真;最后,在FPGA上实现了该测试电路。仿真及硬件验证结果表明,该方法可以准确地发现互连线上所存在的延迟故障。

随着集成电路集成度的不断提高,要生产出完全没有故障的NoC芯片越来越困难,芯片的成品率也越来越低,仅仅能够诊断出互连线上所存在的延迟故障是不够的。今后的研究需重点考虑以下问题:1) 容错设计:当NoC中某一部分出现故障时,系统不仅可以发现该故障,而且可以通过调整自动避开该故障,使得电路可以继续正常工作。2) 在线测试:本文的方法只能在系统处于测试状态时进行,不能对NoC的运行状态做实时监测。需要研究在线测试方法,在系统运行时对系统进行实时监测,报告系统中所出现的瞬态或永久故障,并可以利用容错设计的方法予以纠正。

Research of Interconnection Delay Fault Detection of Network-on-Chip

-

摘要: 基于GALS结构的NoC节点间通常拥有较长的互连线,并且采用异步方式进行通信,对延迟匹配的要求较高。该文提出了一种内建自测试方法,完成跨时钟域互连链路的延迟测试问题。针对该方法完成了相应的测试电路以及测试矢量生成模块的设计与仿真,并在FPGA中实现该电路以验证测试电路的功能和性能。仿真与硬件验证结果都表明,所设计的测试电路以及ATPG模块能够实现NoC互连线延迟故障诊断的功能;该文的延迟故障诊断方法能够快速准确地发现互连线上存在的延迟故障。Abstract: There are quite long interconnection lines between the nodes of a network-on-chip (NoC) based on the globally asynchronous locally synchronous (GALS) structure. It is difficult to match the delay requirement for the communication with the asynchronous ways. In this paper, we propose a build-in self-test (BIST) method to solve the problem of interconnection delay fault across different clock domains. The test circuit and the module of automatic test pattern generation (ATPG) are designed and simulated. The circuit with FPGA is realized to verify the function and performance of the test circuit. The results of simulation and hardware verification indicate that test circuit and the module of ATPG can carry out the function of interconnection delay fault diagnosis of NoC, and the proposed method of interconnection delay fault diagnosis can detect the delay fault existed in the interconnection line rapidly and accurately.

-

表 1 各链路上延迟数值

From To 延迟/ns dataout_2 tdata_buf_2 8.56 dataout_5 tdata_buf_5 8.06 dataout_7 tdata_buf_7 7.81 data_en data_en_r 6.44 dataout_6 tdata_buf_6 5.04 dataout_3 tdata_buf_3 4.89 dataout_1 tdata_buf_1 4.55 dataout_0 tdata_buf_0 4.30 dataout_4 tdata_buf_4 3.19 表 2 BIST电路逻辑资源消耗

已用 可用 利用率/% 触发器 98 9 312 1 LUT 152 9 312 1 -

[1] LAI Ming-che, GAO Lei, XIAO Nong, et al. An accurate and highly-efficient performance evaluation approach based on queuing model for on-chip network[J]. Sicience China Information Sciences, 2013, 56(7):1-20. https://www.researchgate.net/publication/257686935_An_accurate_and_highly-efficient_performance_evaluation_approach_based_on_queuing_model_for_on-chip_network [2] KHETADE V E, LIMAYE S S. Novel data dependent pausible clocking scheme with pll calibration for GALS NOC[C]//Recent Advances in Intelligent Computational Systems (RAICS).[S.l.]:IEEE, 2011:813-818. [3] NAEEM A. Scalability analysis of memory consistency models in NoC-based distributed shared memory SoCs[J]. Computer-Aided Design of Integrated Circuits and Systems, 2013, 32(5):760-773. doi: 10.1109/TCAD.2012.2235914 [4] FU Fang-fa, MA Jian-xin, WU Zi-xu, et al. Low-cost router microarchitecture based on dimension-switch for fault-tolerance in 2D-mesh NoC[C]//Optoelectronics and Microelectronics Technology (AISOMT).[S.l.]:IEEE, 2011:313-319. [5] GALVEZ J J, RUIZ P M. Efficient rate allocation, routing and channel assignment in wireless mesh networks supporting dynamic traffic flows[J]. Ad Hoc Networks, 2013, 11(6):1765-1781. doi: 10.1016/j.adhoc.2013.04.002 [6] LOTFI-KAMRAN P, RAHMANI A M, DANESHTALAB M, et al. EDXY-A low cost congestion-aware routing algorithm for network-on-chips[J]. Journal of Systems Architecture, 2010, 56(7):256-264. doi: 10.1016/j.sysarc.2010.05.002 [7] 姜书艳, 罗刚, 吕小龙, 等. 片上网络互连串扰故障模型的研究及改进[J]. 电子测量技术, 2012, 35(4):123-127. http://www.cnki.com.cn/Article/CJFDTOTAL-DZCL201204032.htm JIANG Shu-yan, LUO Gang, LÜ Xiao-long, et al. Improvement and verification of interconnection crosstalk fault model of network-on-chip[J]. Electronic Measurement Technoloty, 2012, 35(4):123-127. http://www.cnki.com.cn/Article/CJFDTOTAL-DZCL201204032.htm [8] JIANG Shu-yan, LUO Gang, LIANG Hao, et al. A test method of interconnection online detection of NoC based on 2D torus topology[C]//2011 International Conference on Applied Superconductivity and Electromagnetic Devices, ASEMD 2011. Sydney, Australia:[s.n.], 2011:183-187. [9] 姜书艳, 罗刚, 吕小龙, 等. 90 nm和65 nm工艺下片上网络互连串扰故障模型分析[J]. 电子测量与仪器学报, 2012, 26(3):267-272. http://www.cnki.com.cn/Article/CJFDTOTAL-DZIY201203016.htm JIANG Shu-yan, LUO Gang, LÜ Xiao-long, et al. Analysis of interconnection crosstalk fault model of network-on-chip undertechnique of 90 nm and 65 nm[J]. Jounal of Electronic Measurement and Instrument, 2012, 26(3):267-272. http://www.cnki.com.cn/Article/CJFDTOTAL-DZIY201203016.htm [10] JIANG Shu-yan, LUO Gang, CHEN Su, et al. Study of synchronization test methods of NoC at multi-clock domains[J]. COMPEL-the International Jounal for Computation and Mathematics in Electrical and Electronic Engineering, 2013, 32(2):504-515. doi: 10.1108/03321641311296909 [11] CHANG Kai-hui, CHOU Hong-zu, MARKOV I L. RTL analysis and modifications for improving at-speed test[C]//Proceedings Design, Automation and Test in Europe, DATE. Dresden, Germany:IEEE:400-405. [12] CASELLI N, STRANO A, LUDOVICI D, et al. Cooperative built-in self-testing and self-diagnosis of NOC bisynchronous channels[C]//Proceedings-IEEE 6th International Symposium on Embedded Multicore SoCs, MCSoC 2012. Washington, DC, USA:IEEE Computer Society, 2012:159-166. [13] KUIKEN O J, ZHANG Xiao, KERKHOFF H G. Built-in self-diagnostics for a NoC-based reconfigurable IC for dependable beamforming applications[C]//IEEE International Symposium on Defect and Fault Tolerance in VLSI Systems. Washington, DC, USA:IEEE Computer Society, 2008:45-53. [14] ATTARHA A, NOURANI M. Testing interconnects for noise and skew in gigahertz SoC[C]//Proc of ITC.[S.l.]:IEEE, 2001:305-314. [15] SU Chau-chin, CHEN Yue-tsang, HUANG Mu-jeng, et al. All digital built-in delay and crosstalk measurement for on-chip buses[C]//Proc of DATE Conf. Paris, France:IEEE Computer Society, 2000:527-531. [16] JUTMAN A. At-speed on-chip diagnosis of board-level interconnect faults[C]//Proc of 9th European Test Symposium. Washington, DC, USA:IEEE Computer Society, 2004:2-7. [17] CUVIELLO M, DEY S, Bai Xiao-liang, et al. Fault modeling and simulation for crosstalk in system-on-chip interconnects[C]//1999 IEEE/ACM International Conference on Computer-Aided Design. San Jose, CA, USA:IEEE, 1999:297-303. -

ISSN

ISSN

下载:

下载: