-

随着数字集成电路的特征尺寸进入纳米量级,集成电路的稳定性逐渐成为研究重点,尤其是低功耗下的电路容错特性。一方面深亚微米下会出现更多由工艺或信号带来的随机噪声,具有动态特性会出现在电路的各个位置,且不容易被传统的检测技术识别[1-2];另一方面,传统低功耗技术常依托于降低电路供电电压来实现。但电路容错阈值也随供电电压的降低而变小,因此数字电路本身对噪声的容错能力会被大大削减。在噪声增加、电路容错能力下降的双重背景下,低功耗的容错问题成为研究热点。

传统的容错技术解决方法:1) 针对传输中的错误,如电容电感串扰(crosstalk)[3]电压降(IR drop)[4]、接地反弹(ground bounce)[5]等,其解决思路是在假设逻辑操作正确的基础上。但此假设在深亚微米的电路中并不实际,因为低特征尺寸下,电路会出现源于工艺或信号的本征噪声,受此影响基本逻辑操作会出现一定比例或较大比例的错误。2) 纠错技术[6-7],其瓶颈是噪声分布的未知性,因此未能有效地对随机噪声进行编码纠错。

在动态噪声的干扰下,基于统计学的解决思路是研究的热点,近年来研究者将MRF的特性应用到电路结构设计[8-10],从能量的观点来处理动态随机噪声,得到低功耗下电路高稳定的特性。以马氏场论为基础的电路设计不再力求每个电路节点的每个信号在每一时刻都正确,而是从统计学的角度达到电路运算正确的联合概率最大化。从能量角度实现正确运算的能量低于错误能量,使得电路稳定在正确状态中,其电路可在超低供电压下达到很高的噪声容错性能。相较于传统的CMOS电路,其主要的不足是MRF基本逻辑门电路结构复杂,面积大约是传统对应逻辑门电路的20倍,从而制约了该技术在大规模集成电路中的应用。后续研究者以优化面积为目标陆续提出了面积优化的MRF(area-efficient MRF)电路[11],master-slave(MS)电路[7],MS电路可以实现相比原MRF结构50%的面积优化,但其结构存在性能损失[12]。本文提出了环逻辑的共享技术[13],但是因为没有遵循电路设计能量原则,也出现了电路性能损失。

本文提出一种PMRF的电路设计方法。首先将MRF的簇能量U分割成{U0,U1}两个子集,其中,U0为输出逻辑值为0的能量公式,U1为输出逻辑值为1的能量公式。在实际的电路运算中,存在很多不对称的电路逻辑如NAND、NOR、AND和OR门等。当输入满足贝努力1, 0等概率分布时,输出比特0和1的概率不相等,因此输出逻辑不对称导致簇能量U0,U1也具有不对称性。基于不对称簇能量的表达,本文提出部分簇能量的电路设计方法,只取高概率的簇能量来设计电路,实现面积优化。这种方法因为舍去低概率簇能量而带来性能损失,本文进而提出互补部分能量对的设计思路实现面积优化的多逻辑结构,利用两部分能量电路的互补特性,如NAND和NOR互补能量对电路来互相补偿所舍去的部分能量。本文在设计时向三输入和四输入互补结构拓展,实现MUX和MUX-AND电路结构,并设计以MUX和MUX-AND为基础的8位超前进位加法器。在性能测试和硬件的对比中均显示,本文提出的结构具有20%的性能提升,并在65 nm TSMC版图实现后取得25%的面积节约。

-

马尔科夫电路基于马尔科夫场理论,其电路设计包括从多级布尔逻辑到MRF网络的映射和从MRF网络到MRF基本单元的映射两个过程。

-

设$ X = \{ {x_1}, {x_2}, \cdots, {x_n}\} $是一组随机变量,定义集合{X-xi}为xi的领域Ni,在MRF中直接相连的子集称为簇。如果变量满足以下条件,则为马尔科夫场:

正数性:$ P({x_i}) > 0, \forall {x_1} \in X $; 马氏性:$ P({x_i}\left| {\{ X - {x_i}\} } \right.) = P({x_i}\left| {{N_i}} \right.) $。

-

从CMOS电路到MRF网络映射过程分为点和边的映射,其映射法则为:节点表示输入或输出的变量。边表示基于邻域内簇中的条件概率。MRF的电路设计主要针对电路的联合概率,力求正确的概率大于错误的概率,式(1) 给出了电路联合概率和能量之间的关系,借助式(1) 将最大化的联合概率问题转化成最小化的簇能量问题[8]:

$$ P(X) = \mathop \prod \limits_{c \in C} \frac{1}{Z}{\rm{exp}}\left( {\frac{{ - {U_c}({x_c})}}{{{k_b}T}}} \right) $$ (1) 式中,$ X = \{ {x_1}, {x_2}, \cdots, {x_n}\} $是全部节点的集合;xc是每个簇c的节点子集;Z是归一化的常数;$ {U_c}({x_c}) $表示簇能量;kbT是物理学中的热力学常数。

-

从CMOS电路到基本单元映射的主要目的是设计高性能的基础模块。优化的关键策略是根据式(1) 将最大的联合概率问题转换为最小的簇能量问题。MRF基本单元设计需要正确状态的簇能量低于错误状态的簇能量从而保证电路处于稳定状态。簇能量的设计过程首先将所有的输入输出状态考虑进能量表中,令$ f({x_0}, {x_1}, \cdots, {x_n}) $为输入在簇中的逻辑运算,当操作正确时f=1,反之f=0。又令簇能量为$ {U_c}({x_c}) = - \sum {{f_i}({x_0}, {x_1}, \cdots, {x_n})} $。

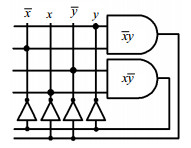

其簇能量由f决定,以MRF反相器为例,反相器的簇能量真值表如表 1所示,其中包括操作正确和错误状态。若正确其簇能量$ U(x, y) = - (\bar xy + x\bar y) $为-1,小于错误的簇能量0。根据簇能量公式设计的MRF反向器如图 1所示,图中上面的NAND完成簇能量公式$ \bar xy $,下面的NAND实现公式$ x\bar y $,反馈结构不仅完成了簇能量的公式,也加强了输入和输出信号。虽然MRF有反馈结构,但依然是组合逻辑,因为其输出由当前输入决定。由MRF的反向器可知其面积和复杂度远大于传统的反向器。同样的设计思路,文献[8-13]提出了MRF的其他逻辑结构以及优化结构,但最终的结构均存在较大的复杂度问题,制约了此电路设计技术向大规模集成电路的发展。

表 1 NAND的能量分割

输入x1x2 输出 状态 本文簇能量分割 部分簇能量 MS分割[12] 理想yout 实际y 00 1 0 错误 0 group0 00 1 1 正确 -1 group1 01 1 0 错误 0 $ {U_0} = \; - {x_1}{x_2}\bar y $ 性能损失簇能量 group0 01 1 1 正确 -1 group1 10 1 0 错误 0 group0 10 1 1 正确 -1 group1 11 0 0 正确 -1 group0 11 0 1 错误 0 group1 -

传统的MRF基本单元基于完整的簇能量公式只有一种逻辑输出(如或逻辑、与逻辑等)[8-9]。受传统的全能量设计启发,本文提出PMRF来指导电路设计实现多逻辑结构。进而提出互补的PMRF对(EPMRF-pair),如NAND-NOR,其互补对相互补偿因为部分簇能量带来的性能损失。

-

首先根据正确的输出值将簇能量分割成两个部分。令$ {X_{{\rm{in}}}} = \{ {x_1}, {x_2}, \cdots, {x_n}\} $为输入信号,yout是输入信号在逻辑运算单元Γ作用下的输出,无噪影响下youtΓ(Xin),噪声情况下$ y = {y_{{\rm{out}}}} + \sigma ({\rm{Noise}}) $,其中σ(Noise)表示噪声影响。在此基础上定义被分割的子簇能量:$ U({X_{{\rm{in}}}}, {y_{{\rm{out}}}} = 0){\rm{ = }}{U_0} $,$ U({X_{{\rm{in}}}}, {y_{{\rm{out}}}} = 1){\rm{ = }}{U_1} $。其中U0和U1表示输出正确为1和为0的子簇能量公式。本文提出的分割方法不同于传统的MS分割方法,如表 1所示。MS[12]分割方法:$ [U({X_{{\rm{in}}}}, {y_{{\rm{out}}}}) = 0]{\rm{ = grou}}{{\rm{p}}_0} $,$ [U({X_{{\rm{in}}}}, {y_{{\rm{out}}}}) = 1]{\rm{ = grou}}{{\rm{p}}_1} $。表 1所示的能量分割方法和原能量公式形式等价。

-

在逻辑运算中,有许多不对称的电路逻辑门,包括NAND、NOR、AND和OR等。例如,表 2所示与非门NAND,当输入为0,1等概率分布时,其输出概分布不对称,逻辑“1”输出和逻辑“0”输出比例为3:1。簇能量公式与输出一一对应,因此簇能量公式项数也有不对称特性。因为MRF的电路设计由簇能量公式决定,由此本文通过舍去部分簇能量来进一步化简电路结构和复杂度。基于上述想法,本文提出部分簇能量方法,当簇能量不对称时,选取高概率的输出值所对应的簇能量。假设簇能量公式项数为c,定义c[U0]=c[U1]为簇能量对称,反之不对称。下文以NAND为例子,表 1中c[U1]=3,c[U0]=1,取U1作为NAND的部分簇能量$ {U_p}{\rm{ = }}{U_1} = - {\bar x_1}{x_2}y - {x_1}{\bar x_2}y\; - {\bar x_1}{\bar x_2}y $,同时部分簇能量U0被舍去,因而也会带来对输出比特‘0’的能量损失。本文方法是性能和面积的折中,下一节将会提出互补部分簇能量对的方法来进行性能补偿。

表 2 NAND-NOR的互补对能量表的能量分割

输入 有效输出 互补的PMRFUm(x1, x2, y1.y2) x1 x2 NAND y1 NOR y2 0 0 1 UP-NAND 1 损失项 x1x2y1y2 0 1 1 UP-NAND 0 UP-NOR 不需要互补项 1 0 1 UP-NAND 0 UP-NOR 不需要互补项 1 1 0 损失项 0 UP-NOR x1x2y1y2 令$ {y_{{\rm{ou}}{{\rm{t}}_i}}} = \mathit{\Gamma }({X_i}) $是经过卡诺图花间的最简表达形式,若存在概率关系$ P\left( {{y_{{\rm{out}}}} = 0\left| {{X_{{\rm{in}}}}} \right.} \right) \le P\left( {{y_{{\rm{out}}}} = 1\left| {{X_{{\rm{in}}}}} \right.} \right) $,则最简的部分簇能量为$ {U_p}({X_{{\rm{in}}}}, y) = - \mathit{\Gamma} ({X_i})y $,若$ P({y_{{\rm{out}}}} = 0\left| {{X_{{\rm{in}}}}} \right.) > P({y_{{\rm{out}}}} = 1\left| {{X_{{\rm{in}}}}} \right.) $,则最简表达式为$ {U_p}({X_{{\rm{in}}}}, y) = - \overline {\mathit{\Gamma} ({X_i})} \overline y $。因此最简的NAND和NOR部分簇能量表示为:

$$ {U_{p - {\rm{NAND}}}}({x_1}, {x_2}, y) = - (\overline {{x_1}{x_2}} )y $$ (2) $$ {U_{P - {\rm{NOR}}}}({x_1}, {x_2}, y)\; = - ({x_1} + {x_2})\overline y $$ (3) -

在逻辑运算中存在互补不对称的逻辑,如与非门NAND是对U1作为部分簇能量的高优先级选取,而或非门NOR则是对U0作为部分簇能量的高优先级选取。选取这些对0和1不同优先级的模块为互补逻辑单元,利用联合簇能量来补偿由于舍去低优先级簇能量带来的性能损失。以NAND-NOR这对互补的部分簇能量对为例说明互补对的构造方法和结构设计。NAND的部分簇能量UP-NAND如表 2所示,输入输出项为{00, 1},{01, 1},{10, 1},而{11, 0}是舍去的部分能量。对于NOR的部分簇能量UP-NOR而言,输入项为{01, 0},{10, 0},{11, 0},而{00, 1}是舍去的部分能量。因为UP-NAND包括NOR簇能量舍去项{00, 1},UP-NAND包括NAND的舍去项{11, 0}。因此两部分簇能量合并就可以相互补偿对方性能损失项。通过化简输入项,利用联合簇能量表达性能补偿$ {U_m} = {y_1}{y_2} + {\bar y_1}{\bar y_2} $。NAND-NOR互补能量对结构如图 2所示,其中g1实现NAND的部分簇能量UP-NAND,g3实现NOR的部分簇能量UP-NOR),而g2和g4实现Um的互补逻辑。对于g1,其逻辑操作为$ {f_1} = \overline {({x_1}{x_2})} {f_4} $;g2: $ {f_2} = \overline {(\overline {{x_1} + {x_2}} ){f_1}} $;g3: $ {f_3} = ({x_1} + {x_2}){f_2} $;g4: $ {f_4} = \overline {({x_1}{x_2}){f_3}} $。化简得到$ {f_4} = \overline {({x_1} + {x_2})} = {y_1} $,带入$ {f_1} = \overline {{x_1}{x_2}} = {y_1} $,$ {f_2} = {x_1} + {x_2} = {\bar y_2} $,$ {f_3} = {x_1} + {x_2} = {\bar y_2} $。此推导也说明回环结构的输出仅由当前输入决定,属于组合电路。相对于传统的结构,文中提出的互补对,因为输出两个逻辑,其单位逻辑的连接线关系没有增加,因此不会影响后端连接线的复杂度。

-

设计时先设计多路选通器MUX结构,将二输入互补逻辑拓展到三输入逻辑。MUX的输入输出关系为$ {y_{{\rm{mux}}}} = {x_a}{x_s} + {x_b}{\bar x_s} $。图 3为扩展NAND-NOR互补对到三输入以后的电路结构,其中灰色模块:g1、g3和g6是部分簇能量结构,g2、g4和g5是能量互补结构。其实现的逻辑公式推导如下,g1逻辑公式为$ {f_1} = \overline {({x_a}{x_s})} {f_4} $;g2: $ {f_2} = \overline {(\overline {{x_s} + {{\bar x}_b}} ){f_1}} $;g3: $ {f_3} = ({x_s} + {\bar x_b}){f_2} $;g4: $ {f_4} = \overline {({x_a}{x_s}){f_3}} $。令$ {y_1} = \overline {({x_a}{x_s})} $,$ {y_2} = \overline {({x_s} + {{\bar x}_b})} $,得$ {f_5} = \overline {{{\bar x}_b} + {x_s}} + {x_a}{x_s} = {x_b}{\bar x_s} + {x_a}{x_s} $,$ {f_4} = {y_1} $。

在设计EPMRF MUX的基础上设计EPMRF MUX-AND模块用于实现超前进位加法器模块结构,其中f3可与与门形成互补逻辑对,MUX-AND模块如图 4所示。在MUX-AND和MUX设计的基础上超前进位加法器进位模块结构如图 5所示。本文真值表化简是为了更清晰地说明设计思路,在大规模设计中可只用NAND-NOR等互补对为基础单元。

-

本文的电路测试平台为低功耗仿真工具HSPICE,使用TSMC 65 nm CMOS库仿真,其标准电压是1.2 V,阈值电压为0.22 V。在供电电压为0.25 V的测试条件下,针对不同的MRF的NAND模块噪声性能测试结果如图 6所示。本文提出的互补能量对的部分能量MRF(EPMRF-pair)的噪声容错能力比传统CMOS,MS以及cyclic结构都有明显的提高,其中CMOS的性能在低电压下较差无法稳定工作,cyclic NAND[13]稳定性较差,MRF-NAND[10]和MRF-MS[12]均存在毛刺。本文多逻辑结构不仅在性能方面有一定的提升,在面积方面,也比MRF-NAND和MRF-MS节约了73%和43%,如表 3所示,体现了其在大规模的逻辑运算中的复杂度优势。表 3中,A是反相器面积,n是NAND个数,value是面积节约百分比公式(value-EMRFpair)/value。

表 3 面积比较

本文同时测试了在0.25 V电压和不同的输入信噪比(signal-to-noise ratio,SNR)条件下加法器电路的容错性能。其中输入为高斯分布零均值,100、110、120、130、150 mV方差的噪声,并且在电源和地之间加入10mV的噪声仿真。将HSPICE测试结果导入MATLAB进行数据分析并计算噪声功率。测试的基准信号是室温下的无噪声传统CMOS结构。本文提出的加法器结构和传统结构的比较如图 7所示,可见在不同SNR条件下本文提出的加法器结构的输出性能较几种传统结构有1 dB以上的改善。

-

本文针对加法器进行了专用集成电路版图的实现,其使用65 nm TSMC工艺库,在前端Design Compiler综合和后端IC Compiler布局布线后得到版图如图 8所示,其版图的面积比较和延时比较如表 4所示,表中,Vdd_min为当输入为SNR= 6.5 dB,输出的噪声方差<10-4V。在与传统CMOS对比中可以看出本设计的最低工作电压为0.25 V,其对应为功耗可以实现93.8%的能耗节约。

表 4 加法器版图的测试结果对比

方案 面积/μm2 晶体管数 延时/ns 能耗/mm×MHz+ @ Vdd-min Pre-layout Post-layout CMOS_CLA 66.96 12*12 312 0.63 1.69@0.8 V MRF_CLA 945.4 43.4*43.4 4 594 3.02 7.53@0.4 V MS_CLA 622 35.2*35.2 3 332 1.60 755@0.35 V 本文CLA 438 29.5*29.5 2 365 1.70 104@0.25V 在与MS超前进位加法器[12]的比较中,本文提出的结构在增加5.8%的延时条件下,具有29%的面积优势和86%的能耗改善。

-

本文提出一种部分簇能量的电路设计方法,并进一步根据两个互补部分簇能量构造互补的簇能量对来补偿电路的性能损失。其结构具超低供电电压及不同输入SNR下的容错性能优势,并且在版图实现后具有86%的功耗和29%的面积节约。本文提出的方法适合大规模集成电路的超低功耗高稳定性电路的使用。

MRF Circuits Design with Complementary Partial Clique Energy Method

-

摘要: 功耗是电路设计的关键性问题之一,低功耗下的稳定性问题逐渐成为电路设计的热点和挑战,基于马尔科夫随机场(MRF)的低功耗设计从能量的角度出发有效地解决了电路的容错问题,但是其单逻辑的单元结构面积和复杂度制约了该技术在大规模集成电路的应用。该文提出了一种基于部分簇能量的MRF电路设计方法(PMRF),并结合互补逻辑的特点来实现多逻辑结构,面积共享的同时一方面补偿由于部分簇能量带来的性能损失,一方面化简马氏随机场电路设计在较大规模电路设计中的面积和复杂度瓶颈问题。对比传统MRF电路设计,该文用PMRF方法设计了超前进位加法器结构,在低功耗仿真中具有20%的性能提升,并在65 nm TSMC版图实现后取得29%的面积节约和86%的功耗节约。Abstract: Power consumption is a key issue in digital circuit design. The reliability of circuits becomes one of main challenges for low supply voltage design. Markov random field (MRF) circuits, which are the probabilistic-based approaches with energy based point of view, can achieve high noise immunity in ultra-low supply. However the traditional MRF elements have complex structures which become a stringent limitation factor for the application of MRF-based circuits in VLSI design. In this paper, we present a partial MRF (PMRF) clique energy design method for multi-logic elements, which can be referred to complementary PMRF pair. The proposed structure compensates the performance loss and achieves the area and complexity reduction. A full carry-look-ahead adder is implemented by using our proposed PMRF-pairs on the 65 nm TSMC CMOS technology. The measurement results show that the PMRF-pairs design can achieve higher fault-tolerance while occupying 29% area-saving, 86% energy-saving and 20% performance improvement compared with the complete MRF design.

-

Key words:

- complementary logic /

- look-ahead adder /

- low-power /

- MRF /

- noise immunity

-

表 1 NAND的能量分割

输入x1x2 输出 状态 本文簇能量分割 部分簇能量 MS分割[12] 理想yout 实际y 00 1 0 错误 0 group0 00 1 1 正确 -1 group1 01 1 0 错误 0 $ {U_0} = \; - {x_1}{x_2}\bar y $ 性能损失簇能量 group0 01 1 1 正确 -1 group1 10 1 0 错误 0 group0 10 1 1 正确 -1 group1 11 0 0 正确 -1 group0 11 0 1 错误 0 group1 表 2 NAND-NOR的互补对能量表的能量分割

输入 有效输出 互补的PMRFUm(x1, x2, y1.y2) x1 x2 NAND y1 NOR y2 0 0 1 UP-NAND 1 损失项 x1x2y1y2 0 1 1 UP-NAND 0 UP-NOR 不需要互补项 1 0 1 UP-NAND 0 UP-NOR 不需要互补项 1 1 0 损失项 0 UP-NOR x1x2y1y2 表 3 面积比较

表 4 加法器版图的测试结果对比

方案 面积/μm2 晶体管数 延时/ns 能耗/mm×MHz+ @ Vdd-min Pre-layout Post-layout CMOS_CLA 66.96 12*12 312 0.63 1.69@0.8 V MRF_CLA 945.4 43.4*43.4 4 594 3.02 7.53@0.4 V MS_CLA 622 35.2*35.2 3 332 1.60 755@0.35 V 本文CLA 438 29.5*29.5 2 365 1.70 104@0.25V -

[1] REJIMON T, LING A, BHANJA S. Probabilistic error modeling for nano-domain logic circuits[J]. IEEE Trans VLSI, 2009, 17(1):55-65. doi: 10.1109/TVLSI.2008.2003167 [2] VAHID H, ALI P. A graph based approach for reliability analysis of nano-scale VLSI logic circuits[J]. Microelectronics Reliability, 2014, 54(3):1299-1306. doi: 10.1016/j.microrel.2014.01.017 [3] QIAN Li-bo, XIA Yin-shui, SHI Ge. Study of crosstalk effect on the propagation characteristics of coupled MLGNR interconnects[J]. IEEE Trans Nanotechnology, 2016, 15(5):810-819. doi: 10.1109/TNANO.2016.2586920 [4] DING Wei-sheng, HSIEH H, HAN Cheng-yu. Test pattern modification for average IR-drop reduction[J]. IEEE Trans VLSI, 2016, 24(1):38-49. doi: 10.1109/TVLSI.2015.2391291 [5] SHIUE G H, YEH C L. Ground bounce noise induced by crosstalk noise for two parallel ground planes with a narrow open-stub line and adjacent signal traces in multilayer package structure[J]. IEEE Trans Components, 2014, 4(5):870-881. http://ieeexplore.ieee.org/xpl/articleDetails.jsp?reload=true&arnumber=6727451&filter%3DAND%28p_IS_Number%3A6810855%29 [6] HONG Jian, KIM S. Flexible ECC management for low-cost transient error protection of last-Level caches[J]. IEEE Trans VLSI, 2016, 24(6):2152-2164. http://ieeexplore.ieee.org/lpdocs/epic03/wrapper.htm?arnumber=7368208 [7] FARBEH H, KIM H. Floating-ECC:Dynamic repositioning of error correcting code bits for extending the lifetime of non-volatile caches[J]. IEEE Trans Computers, 2016, 16(99):1-10. http://ieeexplore.ieee.org/xpl/mostRecentIssue.jsp?punumber=12&isnumber=7605562 [8] BAHAR R I, CHEN Jie. A probabilistic-based design for nanoscale computation[J] Nano, Quantum and Molecular Computing, 2004, 14(2):133-156. doi: 10.1007/1-4020-8068-9_5 [9] BAHAR R I, CHEN Jie. A Probabilistic-based design for nanoscale computation[M]. Beijing:Academic Publishers, 2005:133-156. [10] NEPAL K, BAHAR R I, MUNDY J. Designing logic circuits for probabilistic computation in the presence of noise[C]//IEEE DAC. San Jose:ACM, 2005:485-490. [11] BAHAR R I, CHEN Jie. A probabilistic-based design for nanoscale computation[J]. IEEE Transactions on Circuits and Systems I:Regular Papers, 2010, 5(14):21-36. doi: 10.1007/1-4020-8068-9_5 [12] WEY I C, CHEN Y G. Design and implementation of cost-effective probabilistic-based noise-tolerant VLSI circuits[J]. IEEE Transactions on Circuits and Systems I:Regular Papers, 2009, 56(11):2411-2420. doi: 10.1109/TCSI.2009.2015648 [13] LI Yan, LI Xiao-qian, HU Jian-hao. Area-sharing cyclic structure MRF cirucits design in ultra-low supply voltage[C]//IEEE International Symposium on Circuits and Systems. Beijing:IEEE, 2015:2353-2356. [14] PARIHI K K. VLSI digital signal processing systems:Design and implementation[M]. Beijing:John Wiley & Sons, 2007:50-80. -

ISSN

ISSN

下载:

下载: