-

随着信息技术的飞速发展,人们对存储器的安全性、可靠性有了更高的要求。与传统非易失性存储器[1-2]相比,一次可编程(one time programmable, OTP)存储器凭借其较高的可靠性、极强的稳定性和抗辐照等特性,广泛地应用于高稳定性、高保密性和一次编程等重要场[3-6]。如射频识别(radio frequency identification, RFID)、芯片密钥信息存储、航空航天以及太空领域等[7-9]。然而,由于极易受到OTP存储器器件工艺的影响[10],如今的OTP存储器在读取和编程过程中极易出错[11],从而大大降低了数据存储的可靠性[12]。因此,如何降低OTP存储器在编程或读取过程中的出错率,提高OTP存储的可靠性,成为OTP存储控制器领域的技术难点。探究高性能、高可靠性的OTP存储控制器,确保数据安全、正确地存储,对OTP存储器的发展具有重大的意义和价值[13-14]。

本文中设计了一种具有高可靠性的OTP存储控制器,通过配置相关的控制寄存器,产生不同指令的接口时序,实现对OTP存储器的编程、读取、唤醒、复位、睡眠等操作。采用配置寄存器方式来操作OTP存储器可增加OTP的灵活性,同时,在对OTP存储器编程操作过程中,本文设计了一种编程算法,即对OTP存储器编程地址进行冗余处理,并对同一个地址多次施加脉冲电压。解决了OTP存储器容易出现编程错误的问题,并在OTP存储控制器中设计加扰电路对密钥等特殊信息进行加密,提高了访问OTP存储器的可靠性、安全性。

-

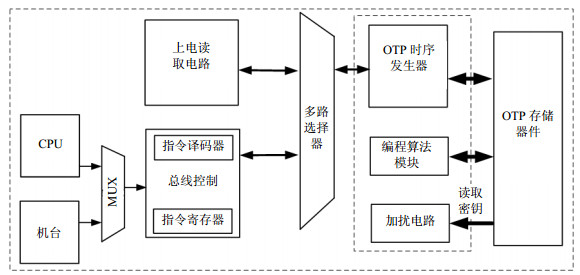

OTP存储控制器内部包括CPU、上电读取电路、总线控制模块、多路选择器、OTP时序发生器电路、编程算法电路和加扰电路。OTP存储控制器系统架构如图 1所示。

CPU用于配置和访问存储器的指令,上电读取电路用于在OTP存储控制器上电时读取它各个区域的信息。控制电路用于装载CPU的一系列指令集,并解析所定义的操作OTP存储器的指令。多路选择器选择上电读取电路读取信息指令或总线控制电路的指令,并将选择的指令传送至时序发生器。时序发生器电路按照CPU发送的操作指令产生对应的访问存储器的时序。编程算法模块在对OTP存储器进行编程操作时,对OTP存储器所需编程的地址进行冗余处理,地址冗余处理机制可以把一个逻辑地址映射到多个物理地址上,当存储在某个物理地址上的数据出现错误时,可以通过该映射关系找到这个逻辑地址上映射的其他物理地址的数据,避免存储的数据丢失。对每一个所要编程的数据采取施加多次(高达16次)编程脉冲电压处理的方式把数据编程到OTP存储器中,大大增加了OTP数据存储的可靠性。加扰电路用于对存储器中读取的密钥信息进行加密处理,极大地提高了访问OTP存储器的可靠性、安全性。加扰电路对密钥信息等特殊信息采用加密的算法具体为:对其编程信息在编程至OTP存储器件之前加上0x55,使得编程至OTP器件的数据被打乱,同样在从OTP存储器件中读取出来时,在加扰电路模块再将读取出的数据减去0x55,从而还原数据。这种方法在占用很小的芯片面积的情况下,实现了数据的加密,保证了密钥等特殊信息的安全性和可靠性。

-

本文设计的OTP存储器内部区域如图 2所示,包括:芯片序列号区域,用于存储芯片序列号;接口封闭区域,用于存储相关接口封闭信息;OTP存储器工作模式区域,用于存储OTP存储器的操作模式,包括机台工作模式和正常工作模式;系统封闭控制区域,用于存储封闭系统区域的控制信息;用户封闭控制区域,用于存储用户区域的控制信息;系统密钥区域,用于存储密钥信息区域;以及用户区,用于存储用户所要存储的信息。

-

本文设计的OTP存储控制器首先需要上电初始化操作,待OTP存储控制器上电后,将整OTP存储器进行初始化。配置OTP存储控制器的控制寄存器对OTP存储控制器进行唤醒操作,然后对OTP存储控制器内部逻辑进行复位,复位后读取OTP存储器中所保存的数据,并依次读取OTP存储器模式信息、接口封闭信息、系统区域封闭信息、用户区域封闭信息及系统密钥区域信息。当读取OTP存储器内部信息完毕后,OTP存储器进入睡眠状态,等待CPU发出唤醒指令。通过OTP存储控制器的上电操作,使OTP存储器每次上电或进行测试、写入、读取等操作时都要重新配置寄存器,避免了由于控制器内部寄存器的值没有及时复位而导致的指令错误,从而造成数据出错。

根据CPU的输入,OTP存储控制器有两种模式,测试模式:输入的scan_mode=1’b1;工作模式:输入的scan_mode=1’b0。

-

OTP存储控制器在测试模式下的主要功能是检测OTP存储器是否有硬件损坏,这是对OTP存储器出厂时的必要操作。由于OTP存储器的一次编程性,未编程过的区域存储的值为0,因此,通过读取OTP存储器中未编程的区域,可判断OTP存储器内部是否存在硬件损坏。

在测试模式下,OTP存储控制器的工作状态有8种,分别为:OTP_Wake_Up状态,用于把OTP存储控制器由睡眠状态转换为工作状态;OTP_Reset状态,用于复位OTP存储控制器内部的逻辑;OTP_Read状态,用于读出OTP存储器中保存的数据;OTP_Sleep状态,用于把OTP存储控制器由工作状态转换为睡眠状态;OTP_Blank_Check状态,用于测试OTP存储器的值是否全为0,如果不全是0,说明有制造缺陷;配置OTP控制寄存器中的OTPC_Test_Vol状态,可选择做2 Kb还是8 Kb测试,默认为8 Kb测试;OTP_Program_Info状态,用于对OTP存储器进行写“1”操作,即表示对OTP存储器进行编程,“0”表示OTP存储器默认状态;OTP_Program_Key状态,控制OTPC_Rng寄存器产生随机数,用于对OTP存储器进行编程测试。测试模式下操作流程如图 3所示。

-

OTP存储控制器在正常模式下,时序发生电路根据CPU发送的操作指令生成一系列的时序,完成对OTP存储器的读操作或编程操作。在进行编程操作时,编程至存储器件的数据要经过编程算法的处理才能被编程入OTP存储器中。本文设计嵌入的编程算法即在编程操作中对同一个地址多次施加脉冲电压,施加次数最多可达16次。这充分保证了数据正确编程至OTP存储器的给定地址,从而提高了数据的安全性,避免了数据的编程失败。

正常工作模式下,OTP存储控制器有5种操作状态。分别为:OTP_Wake_Up状态,用于把OTP存储器从睡眠状态转换为工作状态;OTP_Reset状态,用于复位OTP存储控制器的内部逻辑;OTP_Read状态,用于读出OTP存储器中保存的数据;OTP_Sleep状态,用于把OTP存储控制器由工作模式转换为睡眠模式;OTP_Program_Info状态,用于在OTP存储器中进行写“1”操作。

-

当有数据要写入OTP存储器时,CPU将系统模式控制信号otp_opr_start_sys置为0,则系统模式使能信号scan_mode=1’b0,OTP存储控制器进入唤醒状态,等待510个时钟周期后,进入到复位状态。在复位状态下对OTP存储控制器内的寄存器进行复位操作,系统内控制寄存器、状态寄存器、地址寄存器、数据寄存器均被重新配置。复位操作完成以后,将需要访问的OTP存储器区域地址配置到OTPC_ADDR地址寄存器中,配置完成后读出相应地址的数据判断是否为已写入,然后将编程的数据及逻辑比特地址配置到待编程数据寄存器OTPC_WDATA中去,最后通过配置OTP_CTRL状态寄存器发送数据,等待命令检查完毕后调用相应的编程状态机进行编程。

在对OTP存储器操作的过程中,编程和读取操作的地址分配采用冗余处理的方法,提高数据编程至OTP存储器的可靠性。该冗余处理方案集成至编程算法模块的电路来控制实现,每编程一个数据对应4位OTP存储器件的物理地址,并一次对4位物理地址的每一位进行编程,当其中不少于3位地址都编程成功时才可以认为所配置的该位数据编程成功,否则该数据位编程失败。

访问OTP存储器的地址由13位地址构成,包括系统地址、逻辑位地址和物理地址。对地址进行冗余处理结构如图 4所示,系统及逻辑位地址为选中OTP存储器的具体一个区域。对于编程地址,一位逻辑地址映射4位物理地址的冗余,并一次对4位地址的每一位进行编程,当其中不少于3位地址都编程成功时才可认为所配置的该位数据编程成功,否则认为该位数据编程失败。

在对OTP存储器4位物理地址中的每一位数据编程操作时,需配置所要编程的地址,编程地址等于提供的初始编程地址,在提供的初始编程地址位置施加3个编程脉冲电压,并记N(表示记录编程脉冲次数)等于0次;施加完3个编程脉冲电压基础上继续施加1个编程脉冲电压;编程验证操作;通过编程验证操作得到的数据判定编程的数据是否为1(OTP存储器编程数据为“1”,未编程的数据为“0”),若编程数据为“1”,则表示本次对该地址的编程操作成功,继续按照该方法执行下一个地址的编程操作。若编程数据为“0”,执行下一步;判定是否在该位置加了16次编程脉冲电压,判定次数由N来计数。若在指定的该OTP存储器地址位置未达到所加16次编程电压,则继续施加脉冲电压,此时N加1;每施加一次脉冲电压(即N每增加1)进行编程数据是否为“1”的判定,再判定编程脉冲电压是否编程至16次的循环判定,在16次编程脉冲操作之内验证编程数据成功,则该地址数据编程成功;若在该位置加了16次编程电压还是为“0”,则编程失败。具体流程如图 5所示。

-

当需要从OTP存储器中向外读取数据时,需先把要读出的地址放到OTP存储控制器中的地址寄存器OTPC_ADDR中,再把OTP存储器中的控制寄存器OTPC_OTPC_CMD的值改为3’h2。开始信号OTPC_START= 1’b1后,指令译码器电路对CPU所配置的控制寄存器进行解析,并把访问OTP存储器的指令发送至OTP时序发生器电路。时序发生器电路按照所配置的指令生成具体的时序,在该时序的驱动下完成对OTP存储器的访问。等待读取完毕,OTPC_DONE被置为1,数据被输入读寄存器。

-

本文设计了一种高可靠性OTP存储控制器,通过CPU配置不同的寄存器指令来生成一系列接口时序,进而完成对OTP存储器的一系列流程化操作。本文设计的控制器电路降低了对OTP存储器操作过程中的错误率,提高了编程效率。在对OTP存储器密钥信息读取时,通过设计的加扰电路对OTP存储器中读取的数据进行加扰处理,使用户看到的数据与真正写入到OTP存储器的数据不同,从而提高了数据的安全性。写入数据时,通过嵌入编程算法对数据进行处理,保证了数据正确性。对OTP存储器编程采用地址冗余处理及同一个编程地址多次编程的方法,确保了数据正确编程至OTP指定地址,极大地增强了OTP存储器的可靠性。本文设计的OTP存储控制器电路及嵌入的编程算法对其他存储器控制器的设计具有一定的借鉴性。

本文研究工作得到了成都市科技项目(2018- YFYF-00031-GX)的资助,在此表示感谢。

High Reliability OTP Storage Controller

-

摘要: 该文设计了一种OTP存储控制器电路,通过操作OTP存储器指令产生对应不同操作的接口时序,完成对OTP存储器的编程、读取、唤醒、复位、睡眠等操作。同时,在对OTP存储器编程操作中,针对OTP编程易出错的问题,设计了一种编程算法,即对OTP编程地址进行冗余处理,并在编程操作中对同一个地址多次施加脉冲电压,使编程至OTP存储器的数据的正确性急剧提高。嵌入编程算法电路实现了高可靠性的编程算法,有效地控制了OTP存储器的编程操作。因此,本该设计的高可靠性OTP存储控制器解决了访问存储器时容易出现编程错误的问题,提高了访问OTP存储器的可靠性。Abstract: In this paper, an one time programmable (OTP) memory controller circuit is designed. By operating the OTP memory instruction, the interface timings corresponding to different operations are generated to complete operations such as programming, reading, waking up, resetting, and sleeping on the OTP memory. At the same time, in the OTP memory programming operation, a programming algorithm is designed for the OTP programming error-prone problem. That is, the OTP programming address is redundantly processed, and the pulse voltage is applied to the same address multiple times during the programming operation. The accuracy of data programmed into the OTP memory is dramatically increased. The embedded programming algorithm circuit implements a highly reliable programming algorithm and effectively controls the programming operation of the OTP memory. Therefore, it solved the problem of programming error when accessing memory, and greatly improved the reliability of the OTP memory.

-

Key words:

- controller circuit /

- OTP memory /

- programming algorithms /

- reliability

-

[1] 刘洋, 辜科, 李平, 等.新型非易失性存储器的抗辐射能力研究进展[J].太赫兹科学与电子信息学报, 2016, 6(14):966-971. http://d.old.wanfangdata.com.cn/Periodical/xxydzgc201606028 LIU Yang, GU Ke, LI Ping, et al. Research progress of the radiation response of new non-volatile RAMs[J]. Journal of Terahertz Science and Electronic Information Technology, 2016, 6(14):966-971. http://d.old.wanfangdata.com.cn/Periodical/xxydzgc201606028 [2] 拉贝艾, 钱德卡桑, 尼克里克.数字集成电路——电路、系统与设计[M].周润德, 译.北京: 电子工业出版社, 2004: 477-484. RABAEY J M, CHANDRAKASAN A, NIKOLIC A C B. Digital integrated circuits-circuits, systems and design[M]. Translated by ZHOU Run-de. Beijing: Electronic Industry Press, 2004: 477-484. [3] KIM J B, LEE K. 3-Transistor antifuse OTP ROM array using standard CMOS process[C]//2003 Symposium on VLSI Circuits Digest of Technical Papers. Kyoto, Japan: IEEE, 2003, 239-242. https://www.researchgate.net/publication/4028178_3-transistor_antifuse_OTP_ROM_array_using_standard_CMOS_process [4] LI Feng, YANG Xiao-yu, MEEKS A T, et al. Evaluation of SiO2 antifuse in a 3D-OTP memory[J]. IEEE Transactions on Device and Materials Reliability, 2004, 4(3):416-421. doi: 10.1109/TDMR.2004.837118 [5] JANG Ji-hye, YANG Hui-ling, JIN Li-yan, et al. Design of 1-kbit antifuse OTP memory IP using dual program voltage and its measurement[C]//The 8th Electrical Engineering/Electrmics, Computer, Telecommunications and Information Technology(ECTI)Association of Thailand-Conference. Khon Kaen. Thailand: IEEE, 2011: 118-120. https://www.researchgate.net/publication/252016219_Design_of_1-kbit_antifuse_OTP_memory_IP_using_dual_program_voltage_and_its_measurement [6] LI W T, MCKENZIE D R, WISZNIEWSKI W. A comparative study of the on-off switching behavior of metal-in-sulator-metal antifuses[J]. IEEE Electron Device Letters, 1998, 19(9):295-297. https://www.researchgate.net/publication/3253950_Comparative_study_of_the_on-off_switching_behavior_of_metal-insulator-metal_antifuses [7] 袁蕊林.一种OTP存储器读出系统的设计技术研究[D].成都: 电子科技大学, 2012. http://cdmd.cnki.com.cn/Article/CDMD-10614-1012471097.htm YUAN Rui-lin. Research on the design of a OTP memory readout system[D]. Chengdu: University of Electronic Science and Technology of China, 2012. http://cdmd.cnki.com.cn/Article/CDMD-10614-1012471097.htm [8] LEE M C, BARSATAN R, CHAN M. OTP memory fot low cost passive RFID tags[C]//2007 IEEE Conference on Electron Devices and Solid-State Circuits. Taibei, Taiwan, China: IEEE. 2007: 633-636. https://www.researchgate.net/publication/224305900_OTP_Memory_for_Low_Cost_Passive_RFID_Tags [9] 刘敬术, 刘俊伟, 王兼明, 等.基于OTP的一次性电子钱包RFID卡[J].计算机与数字工程, 2009, 31(2):168-170. doi: 10.3969/j.issn.1672-9722.2009.02.047 LIU Jing-shu, LIU Jun-wei, WANG Jian-ming, et al. One time E-purse RFID based on OTP memory[J]. Computer and Digital Engineering, 2009, 31(2):168-170. doi: 10.3969/j.issn.1672-9722.2009.02.047 [10] CHAN W T. NG K P, LEE M C, et al. CMOS-compatible zero-mask one time programmable (OTP) memory design[C]//20089th International Conference on Solid-State and Integrated-Circuit Technology. Beijing, China: IEEE, 2008: 978-981. http://cpfd.cnki.com.cn/Article/CPFDTOTAL-ZGAN200810001216.htm [11] 吴欣昱, 张金旻, 罗玉香. OTP存储器位线负载对读出速度的影响[J].微电子学, 2015, 45(5):649-651, 656. http://d.old.wanfangdata.com.cn/Periodical/wdzx201505022 WU Xin-yu, ZHANG Jin-min, LUO Yu-xiang. Influence of large capacitances upon read-out speed in OTP memory[J]. Microelectronics, 2015, 45(5):649-651, 656. http://d.old.wanfangdata.com.cn/Periodical/wdzx201505022 [12] 毛冬冬, 曾昆农, 李建军. OTP存储器存储单元内寄生电容对读取阈值的影响[J].电子设计工程, 2016, 24(2):82-85. doi: 10.3969/j.issn.1674-6236.2016.02.025 MAO Dong-dong, ZENG Kun-nong, LI Jian-jun. Influence of parasitic capacitance in OTP memory cell on reading threshold[J]. Electronic Design Engineering, 2016, 24(2):82-85. doi: 10.3969/j.issn.1674-6236.2016.02.025 [13] JEON H G, YANG H L, CHOI I H, et al. Design of 32 kbit one-time programmable memory for microcontroller units.[J]. Journal of Central South University. 2012, 19(12):3475-3483. doi: 10.1007/s11771-012-1432-4 [14] SHEN Ling, ZHENG Yong-an, YANG Fan, et al. A low power self-Turoff program method for one-time programmable memory[C]//201613th IEEE International Conference on Solid-State and Integrated Circuit Technology. Hangzhou, China: IEEE, 2016: 25-28. -

ISSN

ISSN

下载:

下载: