-

与硅(Si)基功率半导体器件相比,碳化硅(SiC)功率半导体器件具有工作频率高、开关损耗低、体积小等诸多优点[1-2]。在工业应用场合,尤其是在电机驱动系统中,短路事件时有发生,这种情况下功率器件承受了比正常状态下高得多的电流应力。由于相同功率等级下,单个SiC功率器件芯片面积比Si功率器件小,因而遭遇短路故障时SiC MOSFET比Si MOSFET更容易失效。

目前,不少工作对SiC MOSFET在短路环境下的特性进行了深入地研究。文献[3-4]采用数值模拟和实验相结合的方法研究了1.2 kV的SiC MOSFET的短路失效机理。文献[5]采用二维有限元数值模拟了SiC MOSFET的“热奔”失效模式。文献[6]对比了不同型号的商业化SiC MOSFET的短路特性。文献[7-8]采用半导体器件计算机模拟(TCAD)的方法研究了SiC MOSFET在短路状态下器件内部的温度分布。这些文献的研究结果,对于正确认识SiC MOSFET在短路故障情况下发生失效的起因、应用时选择正确的SiC MOSFET型号以及在SiC MOSFET保护电路的设计等方面都有积极意义。

SiC MOSFET区别于Si MOSFET的一个显著特点是在SiC/SiO2界面处存在着密度高达1012 cm-2·eV-1的界面态陷阱,比Si/SiO2界面态陷阱密度高出两个数量级。

界面态陷阱能够俘获N型MOSFET沟道中的自由电子,形成呈负电性的界面态电荷,这种行为导致沟道中自由电子数量减少、通态电阻增加;同时,呈负电性的界面态电荷对沟道中的自由电子具有电荷散射作用,阻碍了沟道中自由电子的运动、降低了自由电子的迁移率。文献[9-11]从理论和实验两个方面研究了界面态电荷对SiC MOSFET开关特性的影响,指出界面态电荷能够引起SiC MOSFET开通延迟、关断提前和开关损耗增加。

减少界面态电荷的数量能够提升SiC MOSFET的沟道电流,当SiC MOSFET在开关电路中突然遭遇短路事故时,势必将进一步抬升SiC MOSFET的沟道电流密度,因而界面态电荷能够影响SiC MOSFET处于短路状态下的生存时间。

本文以型号为C2M0080120D的SiC MOSFET (第二代碳化硅产品,1.2 kV/36 A)为参照对象,建立了SiC MOSFET在短路故障电路中的失效模型。该模型考虑了短路状态下SiC MOSFET结构中穿过N-漂移区和P基区组成的PN结的泄漏电流,引入了包含界面态电荷的载流子迁移率,讨论了界面态电荷对SiC MOSFET处于短路状态下生存时间的影响,并通过分析界面态电荷对穿过PN结泄漏电流分量的影响因素,揭示了界面态电荷影响SiC MOSFET短路生存时间的机理。

-

一般地,功率MOS器件在开关电路中的模型,基本上都是采用Spice Level-1等效电路模型来反映长沟道器件的静态和动态行为。这种模型[10, 12-13]是根据MOS器件的漏源电压VDS、栅极电压VGS和阈值电压VTH的相对关系将器件的工作状态划分为截止区、线性区和饱和区3个不同的区域,每个区域对应一段电流表达式,分别为:

$${I_{{\rm{CH}}}} = 0,\;{\rm{ 当}}\;{\rm{ }}{V_{{\rm{GS}}}} < {V_{{\rm{TH}}}}$$ (1) $$\begin{array}{c} {I_{{\rm{CH}}}} = \mu {C_{{\rm{ox}}}}\frac{W}{L}[({V_{{\rm{GS}}}} - {V_{{\rm{TH}}}}) \cdot {V_{{\rm{DS}}}} - \frac{1}{2}V_{{\rm{DS}}}^2] \times \\ (1 + \lambda {V_{{\rm{DS}}}}),\;{\rm{ 当}}\;{\rm{ }}{V_{{\rm{GS}}}} > {V_{{\rm{TH}}}}\;\& \;{V_{{\rm{DS}}}} < ({V_{{\rm{GS}}}} - {V_{{\rm{TH}}}}) \end{array}$$ (2) $$\begin{array}{l} {I_{{\rm{CH}}}} = \frac{{\mu {C_{{\rm{ox}}}}}}{2}\frac{W}{L}{({V_{{\rm{GS}}}} - {V_{{\rm{TH}}}})^2}(1 + \lambda {V_{{\rm{DS}}}})\\ \;\;\;\;\;\;\;{\rm{当}}\;{V_{{\rm{GS}}}} > {V_{{\rm{TH}}}}\;\& \;{V_{{\rm{DS}}}} > ({V_{{\rm{GS}}}} - {V_{{\rm{TH}}}}) \end{array}$$ (3) 式中,μ为沟道载流子迁移率;Cox为氧化层电容;W/L为器件的宽长比;λ为沟道调制系数。

遭遇短路故障时,SiC MOSFET的N-漂移区和P基区所构成的PN结直接承受了直流母线电压,此时通过PN结的电流和二极管的反偏PN结相似,因而可以采用经典的PN结理论来描述短路状态下SiC MOSFET内通过N-漂移区和P基区PN结的电流,并且将该电流也称之为泄漏电流。

经典PN结理论认为,通过反偏PN结的泄漏电流由两个电流分量构成,一个分量是空间电荷区因热激发而产生的电子空穴对形成的电流,另一个是N-漂移区和P基区的少数载流子扩散到对方形成的扩散电流。

另外,如前所述,SiC MOSFET的PN结直接承受了母线电压,考虑到比较高的直流电压偏置,雪崩效应所产生的雪崩电流也计入到反偏PN结的泄漏电流,因而短路状态下通过SiC MOSFET的N-漂移区和P基区PN结的电流由3个分量构成,分别是热产生电流Ith、扩散电流Idiff和雪崩电流Iav。

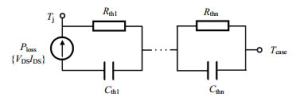

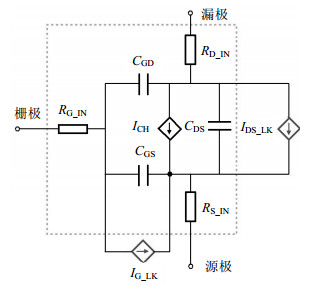

基于此分析,在功率MOSFET的Spice Level-1等效电路模型基础上,引入N-漂移区和P基区构成的PN结泄漏电流,构成了SiC MOSFET在开关电路中因遭遇短路故障而反映其失效过程的模型,其等效电路模型如图 1所示。

图 1中虚线框内即为广泛采用的功率MOS器件的Spice Level-1等效电路模型,虚线框外的电流源IDS_LK代表前面提及到的PN结泄漏电流,另外栅极氧化层的泄漏电流也被引入,用电流源IG_LK表示。IDS_LK和沟道电流ICH并联,与极间电容的充放电电流一起构成了SiC MOSFET的漏源极电流IDS。

表 1列出了泄漏电流IDS_LK的3个电流分量的表达式及其符号取值[5]。

表 1 泄漏电流分量表达式及其符号取值

表达式 符号取值或表达式 ${I_{{\rm{th}}}} = \frac{{qS{n_{\rm{i}}}}}{{{\tau _{\rm{g}}}}}\sqrt {\frac{{2{\varepsilon _{{\rm{SiC}}}}}}{q}\left( {\frac{{{N_{\rm{D}}} + {N_{\rm{A}}}}}{{{N_{\rm{A}}}{N_{\rm{D}}}}}} \right){V_{{\rm{DS}}}}} $ NA=3.5×1017 cm-3

ND=7.5×1015 cm-3

τg=2 ns S=0.124 cm2

${n_{\rm{i}}} = 1.7 \times {10^{16}}{T^{3/2}}{\operatorname{e} ^{ - 2.08 \times {{10}^4}/T}}{\rm{c}}{{\rm{m}}^{ - 3}}$${I_{{\rm{diff}}}} = q{S_{}}\left( {\frac{{n_{\rm{i}}^{\rm{2}}{D_{\rm{n}}}}}{{{L_{\rm{n}}}{N_{\rm{A}}}}} + \frac{{n_{\rm{i}}^{\rm{2}}{D_{\rm{p}}}}}{{{L_{\rm{p}}}{N_{\rm{D}}}}}} \right)$ ${D_{\rm{n}}} = \frac{{kT}}{q}{\mu _{\rm{n}}}$ ${D_{\rm{p}}} = \frac{{kT}}{q}{\mu _{\rm{p}}}$

${L_{\rm{n}}} = \sqrt {{D_n}{\tau _{\rm{n}}}} {\rm{ }}$ ${L_{\rm{p}}} = \sqrt {{D_{\rm{p}}}{\tau _{\rm{p}}}} {\rm{ }}$${\alpha _{\rm{n}}} = 4.6 \times {10^5}\exp \left( { - \frac{{1.78 \times {{10}^7}}}{E}} \right){\rm{ c}}{{\rm{m}}^{ - 1}}$

εSiC=9.7×8.854×10-14 F·cm-1 -

以往所建立的考虑温度影响的功率半导体器件的等效电路模型,是在图 1所示虚线框的电路模型基础上增加温控电流源来实现的[12-13]。当功率半导体器件遭遇短路事故时,直流母线电压直接施加在器件漏源两端,器件内的电场强度和电流应力急剧增加,导致器件的温度急剧升高、载流子的动能和势能增加,但同时载流子受到散射的几率也增加,因而载流子迁移率与温度和场强之间的关系比较复杂,导致功率器件的特性随温度和场强的变化而变化。因此,采用精确的与温度和场强有关的沟道载流子迁移率模型,是建立准确的SiC MOSFET失效模型的关键步骤。

对于N型SiC MOSFET,沟道中的自由电子在输运过程中将遭受4种散射,分别是体晶格散射、声光子散射、表面粗糙度散射和库伦散射,4种散射形成4种不同的载流子迁移率,分别用μB、μAC、μSR和μC表示。根据Mathiessen法则[10, 14-15],SiC MOSFET沟道中自由电子的迁移率μ表示为:

$$\frac{1}{\mu } = \left( {\frac{1}{{{\mu _{\rm{B}}}}} + \frac{1}{{{\mu _{{\rm{AC}}}}}} + \frac{1}{{{\mu _{{\rm{SR}}}}}} + \frac{1}{{{\mu _{\rm{C}}}}}} \right)$$ (4) 表 2示出了上述4种迁移率所对应的表达式及其参数取值,其中,Qinv为沟道反型层电荷,Qtrap为界面态电荷,E⊥为沟道方向垂直电场。从表 2可以看出,SiC MOSFET沟道自由电子的迁移率不仅与温度和场强有关,还和SiC MOSFET的Qtrap有关。

表 2 SiC MOSFET沟道电子迁移率表达式

分量 表达式 取值 μB ${\mu _{{\rm{min}}}} + \frac{{{\mu _{{\rm{max}}}} - {\mu _{{\rm{min}}}}}}{{1 + \frac{{N{}_{\rm{A}}}}{{{N_{{\rm{REF}}}}}}}}$ μmax=950 cm2/V s

μmin=40 cm2/V s

NA=6×1017 cm-3

NREF=2×1017 cm-3μAC $\frac{B}{{{E_ \bot }}} + \frac{{CN_{\rm{A}}^{{\rm{ \mathsf{ α} }}1}}}{{TE_ \bot ^{{\rm{1/3}}}}}$ B=1.0×106 cm/s

α1=0.0284

C=3.23×106 K cm/s·(V/cm)-2/3μSR $\frac{{{D_{\rm{1}}}}}{{E_ \bot ^2}}$ D1=5.82×1014 cm2/V·s (V/cm)2 μC $N{T^{\rm{ \mathsf{ α} }}}\frac{{Q_{{\rm{inv}}}^{\rm{ \mathsf{ β} }}}}{{{Q_{{\rm{trap}}}}}}$ α=1 β=1

N=0.007 525 cm2/V·s -

由表 1和表 2可见处于短路状态下的SiC MOSFET的泄漏电流和迁移率皆与温度有关,为了准确描述强电场和强电流应力下SiC MOSFET的短路行为,需建立SiC MOSFET的电-热耦合模型。对于已经封装了的功率半导体器件,由热容和热阻组成的热网络模型可以模拟功率半导体器件的瞬态热阻抗,Cauer和Foster是两种使用较为广泛的热网络模型。其中,Cauer热网络模型需要功率器件的具体封装信息,因而该模型更接近于器件实际的物理结构,并且能够模拟封装内的温度分布;Foster热网络不需要功率器件的具体封装信息,也不是用来模拟器件内的温度分布,而是根据式(5)所示的简单表达式来模拟器件的结温Tj。结温是功率器件的实际工作温度,更能体现功率器件的电-热耦合过程。

$${T_{\rm{j}}} = {T_{{\rm{case}}}} + {P_{{\rm{loss}}}}{Z_{{\rm{th}}}}$$ (5) 式中,Tcase为环境温度;Ploss为功率器件产生的损耗;Zth为瞬态热阻抗,由组成Foster网络的热阻R和热容C根据式(6)来决定。

$${Z_{{\rm{th}}}} = \sum\limits_{i = 1}^n {{R_i}\left[ {1 - {\rm{exp}}\left( { - \frac{t}{{{R_i}{C_i}}}} \right)} \right]} $$ (6) 图 2示出了SiC MOSFET的电-热耦合模型。SiC MOSFET的功耗Ploss传递到由RC元件组成的Foster热网络,Foster网络根据式(5)和式(6)计算出结温Tj返回给SiC MOSFET的电路模型,电路模型根据与温度相关的物理量重新计算出电压VDS和电流IDS,并得出器件的功耗Ploss,这种电-热耦合行为重复进行,直至仿真结束。

本文建立的SiC MOSFET遭遇短路事故而展现出失效行为的模型是以C2M0080120D为参照对象,根据C2M0080120D手册中的瞬态热阻抗拟合到的14阶Foster模型的RC网络参数如表 3所示。

表 3 C2M0080120D的14阶Foster网络模型的RC参数

热阻Rth/mK·W-1 热容Cth/mJ·K-1 Rth1=13.30 Cth1=0.424 Rth2=13.30 Cth2=0.341 Rth3=37.80 Cth3=1.320 Rth4=36.90 Cth4=1.580 Rth5=8.36 Cth5=1.880 Rth6=5.84 Cth6=2.640 Rth7=4.32 Cth7=8.500 Rth8=5.12 Cth8=14.200 Rth9=5.19 Cth9=26.000 Rth10=4.75 Cth10=47.800 Rth11=4.66 Cth11=102.000 Rth12=5.87 Cth12=165.000 Rth13=4.08 Cth13=282.000 Rth14=1.04 Cth14=2 410.000 -

采用1.2节所述迁移率模型的SiC MOSFET的Spice Level-1等效电路模型的准确性,已经在前期的工作中得到了验证[10, 16],这里仅对比引入泄漏电流模型后对前期所建立的SiC MOSFET等效电路模型的影响。图 3展示了有泄漏电流模型和无泄漏电流模型时SiC MOSFET等效电路模型在箝位开关电路中漏源电压和漏源电流的对比,直流电源电压为470 V。从图中可以看出,在开通和关断阶段泄漏电流模型的影响基本可以忽略,仅仅是在导通阶段引入了泄漏电流模型后SiC MOSFET的通态压降轻微增加、通态电流轻微减小。

图 4示出了验证SiC MOSFET短路失效模型的电路原理图及实验平台。市电经整流后的直流电压VDC通过充电电阻给4个并联、容量为1 mF的电容器提供短路能量,一个数字信号处理器(DSP)开发板给SiC MOSFET的驱动电路提供控制信号,驱动电路通过5.1 的电阻RG来控制SiC MOSFET的导通。

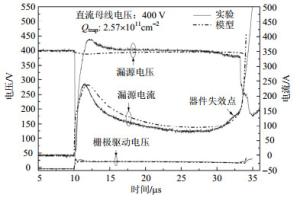

SiC MOSFET短路失效模型的验证如图 5所示,包括漏源电压、漏源电流和栅极电压的对比。由图可见,在400 V的直流偏置下,失效模型很好地再现了SiC MOSFET在短路环境下的失效行为,SiC MOSFET经历了22 μs的短路压力之后漏源电流和栅极电压突然增加,同时漏源电压迅速下降,这些行为表明器件已经失去栅极控制和电压阻挡的功能。

-

表 2所示的SiC MOSFET沟道载流子迁移率模型集成了界面态电荷密度Qtrap,因而可以利用所建立的失效模型探究Qtrap对SiC MOSFET短路失效行为的影响。

减小SiC/SiO2界面陷阱密度较为有效的方式是在高温环境下采用氮钝化的工艺来降低SiC/SiO2界面的悬挂键。由于已封装的SiC MOSFET无法有效测量其SiC/SiO2界面陷阱密度,只能通过测量在相同环境下制备的SiC MOS电容的SiC/SiO2界面陷阱密度来衡量。本文根据文献[17]在高温氮环境下不同的钝化时间所测量到3条界面陷阱密度(Dit),在能级(E)中分布曲线来讨论SiC/SiO2界面陷阱密度对SiC MOSFET短路特性的影响。3条曲线[17]如图 6所示,是在1 175 ℃环境下分别经过0、15、120 min的钝化结果。表 2中的界面电荷Qtrap通过式(7)计算[15]。

$${Q_{{\rm{trap}}}} = \int_{{\rm{ }}{E_{\rm{i}}}}^{{\rm{ }}{E_{\rm{c}}}} {{D_{{\rm{it}}}}(E){\rm{d}}E} $$ (7) 式中,Ei为表面本征费米能级;Ec为导带能级。

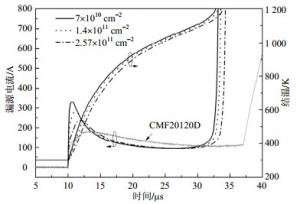

经式(7)计算出来的3种界面态电荷密度分别为7×1010 cm-2、1.40×1011 cm-2和2.57×1011 cm-2。

图 7示出了3种界面态电荷情况下SiC MOSFET在直流偏置电压为400 V时发生短路失效的漏源电流和短路过程中结温的变化曲线。由图可以看出,3种界面态电荷情况下,SiC MOSFET分别经历了21.6 μs、22.1 μs和22.8 μs短路压力后出现了失效行为。此时器件的结温也达到了1 200 K左右,在此温度下,传递到器件表面的温度引起SiC MOSFET氧化层和金属电极的熔化,器件失去了栅极控制和电压阻挡的功能。

图 7也示出了第一代碳化硅MOSFET产品(型号为CMF20120D,1.2 kV /42 A)在相同的直流偏置电压和短路条件下实验所测到的短路失效电流,在短路发生后经历了大约27 μs,器件出现了短路失效行为。对于中低压的碳化硅MOSFET产品,在技术更新过程中一个重要的方向是努力降低SiC/SiO2界面陷阱密度。尽管无法测到两代碳化硅MOSFET产品具体的界面陷阱密度,但是可以肯定,第二代SiC产品的界面陷阱密度比第一代SiC产品的低。

由图 7可以看出,与验证C2M0080120D失效模型的界面电荷密度为2.57×1011 cm-2时的短路电流相比,CMF20120D在短路刚开始的电流上升率明显变慢,饱和电流的峰值也变小,发生短路失效的时间相应延长,这一点也证明了本文所建立的包含了界面态电荷的SiC MOSFET失效模型的准确性。

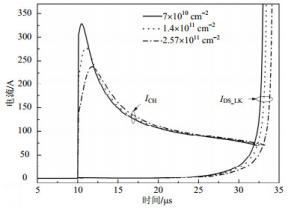

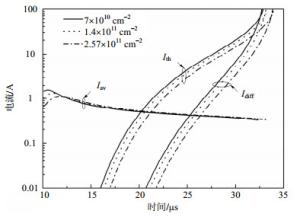

为了探究界面电荷影响SiC MOSFET短路失效行为的机理,本文从图 1失效模型结构中组成漏源电流的成分中分离出3种界面电荷的沟道电流ICH和反偏PN结的泄漏电流IDS_LK,其结果如图 8所示。

从图中可以看出,随着界面态电荷密度的增加,SiC MOSFET的ICH减小,这是因为一方面界面态陷阱捕获了SiC MOSFET沟道中的自由电子,导致ICH减少,另一方面所形成的呈负电性的界面态电荷对自由电子形成散射作用,阻碍了自由电子的运动、降低了自由电子的迁移率,因而在相同的直流偏置电压下,SiC MOSFET的ICH减小。ICH的减小抑制了器件的自热效应,因而图 7中器件结温的上升也得到了抑制。

低界面态电荷密度导致SiC MOSFET在短路发生时,沟道电流快速饱和,随后迅速下降,而高密度的界面态电荷由于前述的对沟道载流子的阻碍作用,沟道电流上升要缓慢一些,并且饱和电流的峰值也要小一些。3种界面态电荷所对应的沟道电流,都是出现饱和后快速下降,这是由于SiC MOSFET沟道载流子在不同温度下的散射机制不同。短路故障刚开始时,器件的温度并不高,沟道自由电子的散射是由库伦散射主导,其迁移率为正温系数,因而ICH增加;随着短路的持续进行,图 7所示的器件温度快速上升,当达到550~600 K时,沟道内自由电子的散射由声光子散射主导,其迁移率表现为负温系数,因而ICH减小。

进一步,本文从图 8中的泄漏电流IDS_LK中分离出组成这种电流的3个分量,3种不同界面态电荷所对应的Ith、Idiff、Iav以对数的形式在图 9中展示。

从图可以看出,3种不同界面态电荷所对应的反偏PN结泄漏电流的3个电流分量,和温度有紧密关系的热产生电流Ith最大,和温度弱相关的扩散电流Idiff其次,而与温度几乎不相关、由反偏电压决定的Iav则在整个短路故障过程中几乎保持不变,并且受界面态电荷密度的影响也非常小。Ith和Idiff则随着界面态电荷密度增加而减小,这是因为在直流偏置电压和器件掺杂浓度一定的情况下,这两个电流分量几乎由温度来决定,而界面态电荷密度的增加抑制了器件的温度上升,因而这两个电流分量的上升也受到了相应的抑制。

-

本文建立了SiC MOSFET在短路故障电路中的失效模型,引入了N-漂移区和P基区之间PN结的泄漏电流,包含SiC/SiO2界面态电荷的载流子迁移率模型。同时,本文在短路状态下验证了失效模型的准确性,讨论了界面态电荷对SiC MOSFET短路耐受能力的影响。

结果表明,SiC MOSFET的SiC/SiO2界面态陷阱密度的减少降低了SiC MOSFET的短路耐受能力,这主要是由于界面态电荷的减少抬升了沟道电流密度,从而加速了短路状态下SiC MOSFET温度的上升,这导致了与温度有关的泄漏电流增加;泄漏电流的增加又抬升了SiC MOSFET器件内的温度。这种相互作用机制加速了SiC MOSFET的短路失效。

Research on the Impact of Trapped Charges at SiC/SiO2 Interface on the Short-circuit Performances of SiC MOSFET

-

摘要: 碳化硅/二氧化硅(SiC/SiO2)界面态电荷数量的减少有利于降低碳化硅金属-氧化物-半导体场效应晶体管(SiCMOSFET)的通态电阻和开关损耗,然而沟道电流的提升会给遭遇短路故障的SiC MOSFET带来更大的电流应力。在传统的SiCMOSFET等效电路模型的基础上建立了SiC MOSFET的短路失效模型,该模型考虑了强电流应力下器件内的泄漏电流,并引入了包含界面态电荷的沟道载流子迁移率。利用该模型讨论了SiC/SiO2界面态电荷对SiC MOSFET短路特性的影响,结果显示界面态电荷的减少缩短了SiC MOSFET短路耐受时间。随后通过从失效电流中分离出不同产生机制下的泄漏电流分量,讨论了界面态电荷对SiC MOSFET短路特性影响的机理。Abstract: The decrease in the trapped charges at SiC/SiO2 interface is helpful to lower the on-state resistance and switching loss of SiC MOSFET, however, the lift of channel current brings higher current stress to SiC MOSFET during short-circuit case. On the basis of the traditional equivalent circuit model for SiC MOSFET, a short-circuit failure model of SiC MOSFET has been developed. The model introduces the leakage current across the PN junction between N-drift region and P base region of SiC MOSFET, and employs an advance carrier mobility model with the trapped charges at the SiC/SiO2 interface. By the developed failure model, the influence brought by the interface trapped charges on the short-circuit performances has been exploited, and the result shows that the reduction of interface trapped charge shortens the time of SiC MOSFET withstanding short-circuit stress. Further, the mechanism of interface trapped charges affecting the short-circuit withstanding time has been discussed by separating the leakage current components from the failure current.

-

Key words:

- carrier mobility /

- current stress /

- interface trapped charge /

- leakage current /

- SiC MOSFET

-

表 1 泄漏电流分量表达式及其符号取值

表达式 符号取值或表达式 ${I_{{\rm{th}}}} = \frac{{qS{n_{\rm{i}}}}}{{{\tau _{\rm{g}}}}}\sqrt {\frac{{2{\varepsilon _{{\rm{SiC}}}}}}{q}\left( {\frac{{{N_{\rm{D}}} + {N_{\rm{A}}}}}{{{N_{\rm{A}}}{N_{\rm{D}}}}}} \right){V_{{\rm{DS}}}}} $ NA=3.5×1017 cm-3

ND=7.5×1015 cm-3

τg=2 ns S=0.124 cm2

${n_{\rm{i}}} = 1.7 \times {10^{16}}{T^{3/2}}{\operatorname{e} ^{ - 2.08 \times {{10}^4}/T}}{\rm{c}}{{\rm{m}}^{ - 3}}$${I_{{\rm{diff}}}} = q{S_{}}\left( {\frac{{n_{\rm{i}}^{\rm{2}}{D_{\rm{n}}}}}{{{L_{\rm{n}}}{N_{\rm{A}}}}} + \frac{{n_{\rm{i}}^{\rm{2}}{D_{\rm{p}}}}}{{{L_{\rm{p}}}{N_{\rm{D}}}}}} \right)$ ${D_{\rm{n}}} = \frac{{kT}}{q}{\mu _{\rm{n}}}$ ${D_{\rm{p}}} = \frac{{kT}}{q}{\mu _{\rm{p}}}$

${L_{\rm{n}}} = \sqrt {{D_n}{\tau _{\rm{n}}}} {\rm{ }}$ ${L_{\rm{p}}} = \sqrt {{D_{\rm{p}}}{\tau _{\rm{p}}}} {\rm{ }}$${\alpha _{\rm{n}}} = 4.6 \times {10^5}\exp \left( { - \frac{{1.78 \times {{10}^7}}}{E}} \right){\rm{ c}}{{\rm{m}}^{ - 1}}$

εSiC=9.7×8.854×10-14 F·cm-1表 2 SiC MOSFET沟道电子迁移率表达式

分量 表达式 取值 μB ${\mu _{{\rm{min}}}} + \frac{{{\mu _{{\rm{max}}}} - {\mu _{{\rm{min}}}}}}{{1 + \frac{{N{}_{\rm{A}}}}{{{N_{{\rm{REF}}}}}}}}$ μmax=950 cm2/V s

μmin=40 cm2/V s

NA=6×1017 cm-3

NREF=2×1017 cm-3μAC $\frac{B}{{{E_ \bot }}} + \frac{{CN_{\rm{A}}^{{\rm{ \mathsf{ α} }}1}}}{{TE_ \bot ^{{\rm{1/3}}}}}$ B=1.0×106 cm/s

α1=0.0284

C=3.23×106 K cm/s·(V/cm)-2/3μSR $\frac{{{D_{\rm{1}}}}}{{E_ \bot ^2}}$ D1=5.82×1014 cm2/V·s (V/cm)2 μC $N{T^{\rm{ \mathsf{ α} }}}\frac{{Q_{{\rm{inv}}}^{\rm{ \mathsf{ β} }}}}{{{Q_{{\rm{trap}}}}}}$ α=1 β=1

N=0.007 525 cm2/V·s表 3 C2M0080120D的14阶Foster网络模型的RC参数

热阻Rth/mK·W-1 热容Cth/mJ·K-1 Rth1=13.30 Cth1=0.424 Rth2=13.30 Cth2=0.341 Rth3=37.80 Cth3=1.320 Rth4=36.90 Cth4=1.580 Rth5=8.36 Cth5=1.880 Rth6=5.84 Cth6=2.640 Rth7=4.32 Cth7=8.500 Rth8=5.12 Cth8=14.200 Rth9=5.19 Cth9=26.000 Rth10=4.75 Cth10=47.800 Rth11=4.66 Cth11=102.000 Rth12=5.87 Cth12=165.000 Rth13=4.08 Cth13=282.000 Rth14=1.04 Cth14=2 410.000 -

[1] 张林, 肖剑, 邱彦章, 等. Ni/4H-SiC SBD电离辐照探测器的实验研究[J].电子科技大学学报, 2012, 41(3):467-470. doi: 10.3969/j.issn.1001-0548.2012.03.028 ZHANG Lin, XIAO Jian, QIU Yan-zhang, et al. Experiment study of Ni/4H-SiC Schottky diode ionization radiation detector[J]. Journal of University of Electronic Science and Technology of China, 2012, 41(3):467-470. doi: 10.3969/j.issn.1001-0548.2012.03.028 [2] 周郁明, 靳爱津, 冯德仁.钒补偿度对SiC光导开关特性影响的研究[J].电子科技大学学报, 2012, 41(6):937-940. http://www.juestc.uestc.edu.cn/CN/abstract/abstract1466.shtml ZHOU Yu-ming, JIN Ai-jin, FENG De-ren. Simulation of vanadium doped concentration on the effect of characteristics of SiC photoconducting switches[J]. Journal of University of Electronic Science and Technology of China, 2012, 41(6):937-940. http://www.juestc.uestc.edu.cn/CN/abstract/abstract1466.shtml [3] CECCARELLI L, REIGOSA P D, IANNUZZO F, et al. A survey of SiC power MOSFETs short-circuit robustness and failure mode analysis[J]. Microelectronics Reliability, 2017, 76-77:272-276. doi: 10.1016/j.microrel.2017.06.093 [4] NAMAI M, AN J, YANO H, et al. Investigation of short-circuit failure mechanisms of SiC MOSFETs by varying DC bus voltage[J]. Japanese Journal of Applied Physics, 2018, 57(7):074102. doi: 10.7567/JJAP.57.074102 [5] WANG Z, SHI X, TOLBERT L M, et al. Temperaturedependent short-circuit capability of silicon carbide power MOSFETS[J]. IEEE Transactions on Power Electronics, 2016, 31(2):1555-1566. doi: 10.1109/TPEL.2015.2416358 [6] IONITA C, NAWAZ M, ILVES K. On the short-circuit and avalanche ruggedness reliability assessment of SiC MOSFET modules[J]. Microelectronics Reliability, 2017, 71:6-16. doi: 10.1016/j.microrel.2017.02.004 [7] ROMANO G, FAYYAZ A, RICCIO M, et al. A comprehensive study of short-circuit ruggedness of silicon carbide power MOSFETS[J]. IEEE Journal of Emerging & Selected Topics in Power Electronics, 2016, 4(3):978-987. http://www.wanfangdata.com.cn/details/detail.do?_type=perio&id=10d2182619fcac7f0d5461ae7fc7b702 [8] SCHROCK J A, PUSHPAKARAN B N, BILBAO A V, et al. Failure analysis of 1200-V/150-A SiC MOSFET under repetitive pulsed overcurrent conditions[J]. IEEE Transactions on Power Electronics, 2015, 31(3):1816-1821. http://www.wanfangdata.com.cn/details/detail.do?_type=perio&id=1175526a066ad0db0048354dcae6f511 [9] TANIMOTO Y, SAITO A, MATSUURA K, et al. Power-loss prediction of high-voltage SiC-MOSFET circuits with compact model including carrier-trap influences[J]. IEEE Transactions on Power Electronics, 2016, 31(6):4509-4516. doi: 10.1109/TPEL.2015.2477413 [10] ZHOU Y M, LIU H Z, YANG T T, et al. SPICE modeling of SiC MOSFET considering interface-trap influence[J]. CPSS Transactions on Power Electronics and Application, 2018, 3(1):56-64. doi: 10.24295/CPSSTPEA.2018.00006 [11] 周郁明, 刘航志, 杨婷婷, 等.碳化硅MOSFET的Matlab/Simulink建模及其温度特性评估[J].南京航空航天大学学报, 2017, 49(6):851-857. http://www.wanfangdata.com.cn/details/detail.do?_type=perio&id=njhkht201706015 ZHOU Yu-ming, LIU Hang-zhi, YANG Ting-ting, et al. Matlab/Simulink modeling and temperature characteristics evaluation of SiC MOSFET[J]. Journal of Nanjing University of Aeronautics & Astronautics, 2017, 49(6):851-857. http://www.wanfangdata.com.cn/details/detail.do?_type=perio&id=njhkht201706015 [12] 孙凯, 陆珏晶, 吴红飞, 等.碳化硅MOSFET的变温度参数建模[J].中国电机工程学报, 2013, 33(3):37-43. http://d.old.wanfangdata.com.cn/Periodical/zgdjgcxb201303005 SU Kai, LU Ju-jing, WU Hong-fei, et al. Modeling of SiC MOSFET with temperature dependent parameters[J]. Proceedings of the CSEE, 2013, 33(3):540-544. http://d.old.wanfangdata.com.cn/Periodical/zgdjgcxb201303005 [13] WANG J, ZHOU X H, Li J, et al. 10-kV SiC MOSFET-based boost converter[J]. IEEE Transactions on Industrial Application. 2009, 45(6):2056-2063. doi: 10.1109/TIA.2009.2031915 [14] 周郁明, 刘航志, 杨婷婷, 等. SiC JFET与SiC MOSFET失效模型及其短路特性对比[J].电子学报, 2019, 47(3):726-733. http://d.old.wanfangdata.com.cn/Periodical/dianzixb201903030 ZHOU Yu-ming, LIU Hang-zhi, YANG Ting-ting, et al. Failure models and comparison in short-circuit performances for SiC JFET and SiC MOSFET[J]. Acta Electronica Sinica, 2019, 47(3):726-733. http://d.old.wanfangdata.com.cn/Periodical/dianzixb201903030 [15] PÉREZ-TOMÁS A, BROSSELARD P, GODIGNON P, et al. Field-effect mobility temperature modeling of 4H-SiC metal-oxide-semiconductor transistors[J]. Journal of Applied Physics, 2006, 100(11):114508. doi: 10.1063/1.2395597 [16] 周郁明, 李勇杰, 鲍观甲, 等.基于先进迁移率模型的4H-SiC MOSFET Spice模型研究[J].中国科学技术大学学报, 2017, 47(10):878-884. doi: 10.3969/j.issn.0253-2778.2017.10.011 ZHOU Yu-ming, LI Yong-jie, BAO Guan-jia, et al. Spice modeling of 4H-SiC MOSFET based on advanced mobility model[J]. Journal of University of Science and Technology of China, 2017, 47(10):878-884. doi: 10.3969/j.issn.0253-2778.2017.10.011 [17] ROZEN J, DHAR S, ZVANUT M E, et al. Density of interface states, electron traps, and hole traps as a function of the nitrogen density in SiO2 on SiC[J]. Journal of Applied Physics, 2009, 105(12):658-662. http://www.wanfangdata.com.cn/details/detail.do?_type=perio&id=40b5d3472e303d251ff177925fbc65e5 -

ISSN

ISSN

下载:

下载: