-

摩尔定律已经逼近物理极限,未来的发展趋势是将延续摩尔定律和超越摩尔定律结合起来,实现更高级的系统——微系统[1-4]。

微系统是一种利用微纳加工技术在微纳尺度上制备而成的电子系统。它涵盖了微电子、光电子、MEMS等多种电子元器件,同时涉及架构、软件以及算法等多种要素,具有体积小、高度集成等特点[5-8]。

本文设计了一种新型三维集成射频模拟数字一体化微系统,变频部分采用直接变频架构,从方案和实现两方面详细介绍了微系统的架构、设计、工艺和验证,重点介绍了一种全新的散热方案。

-

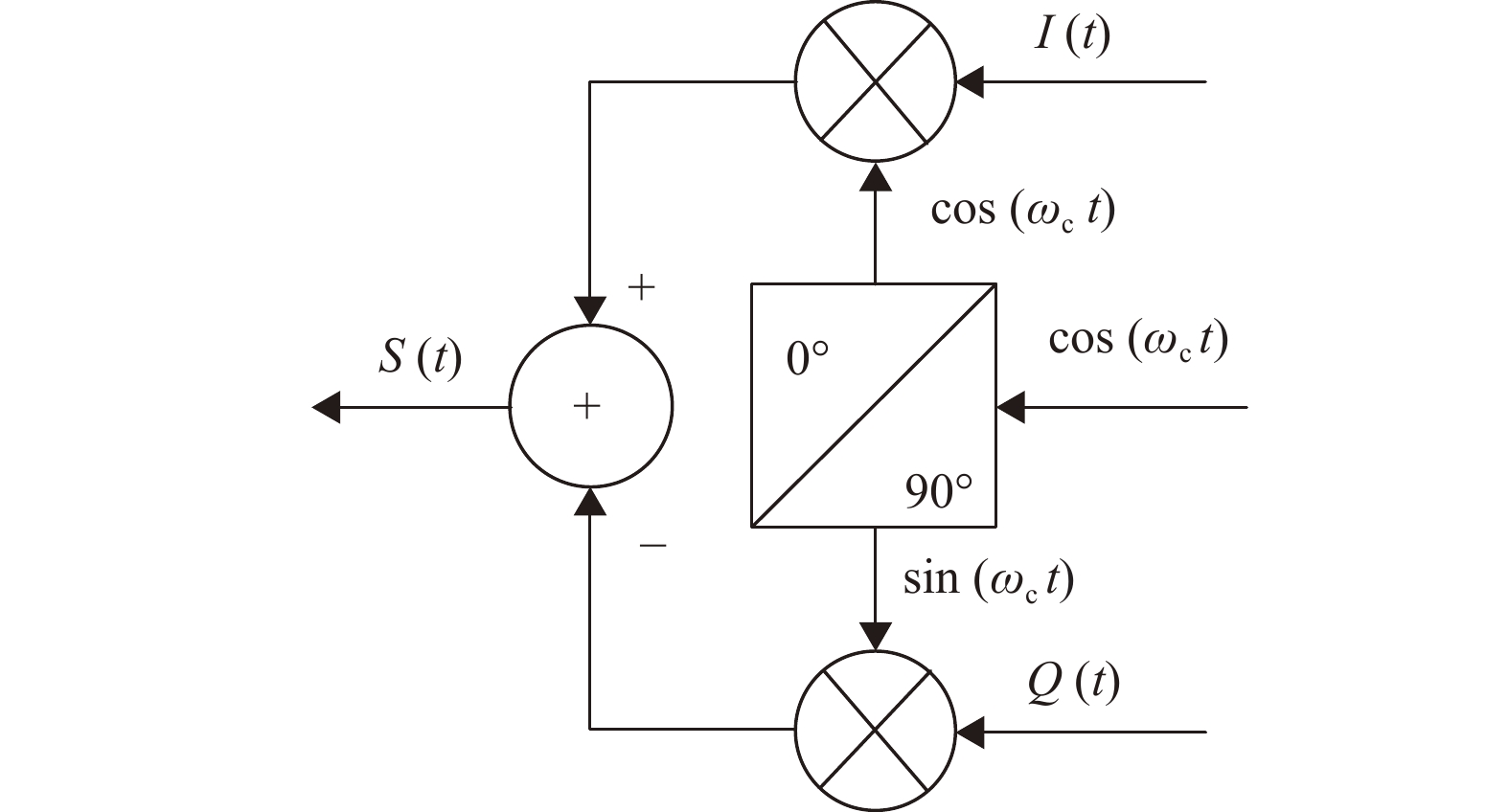

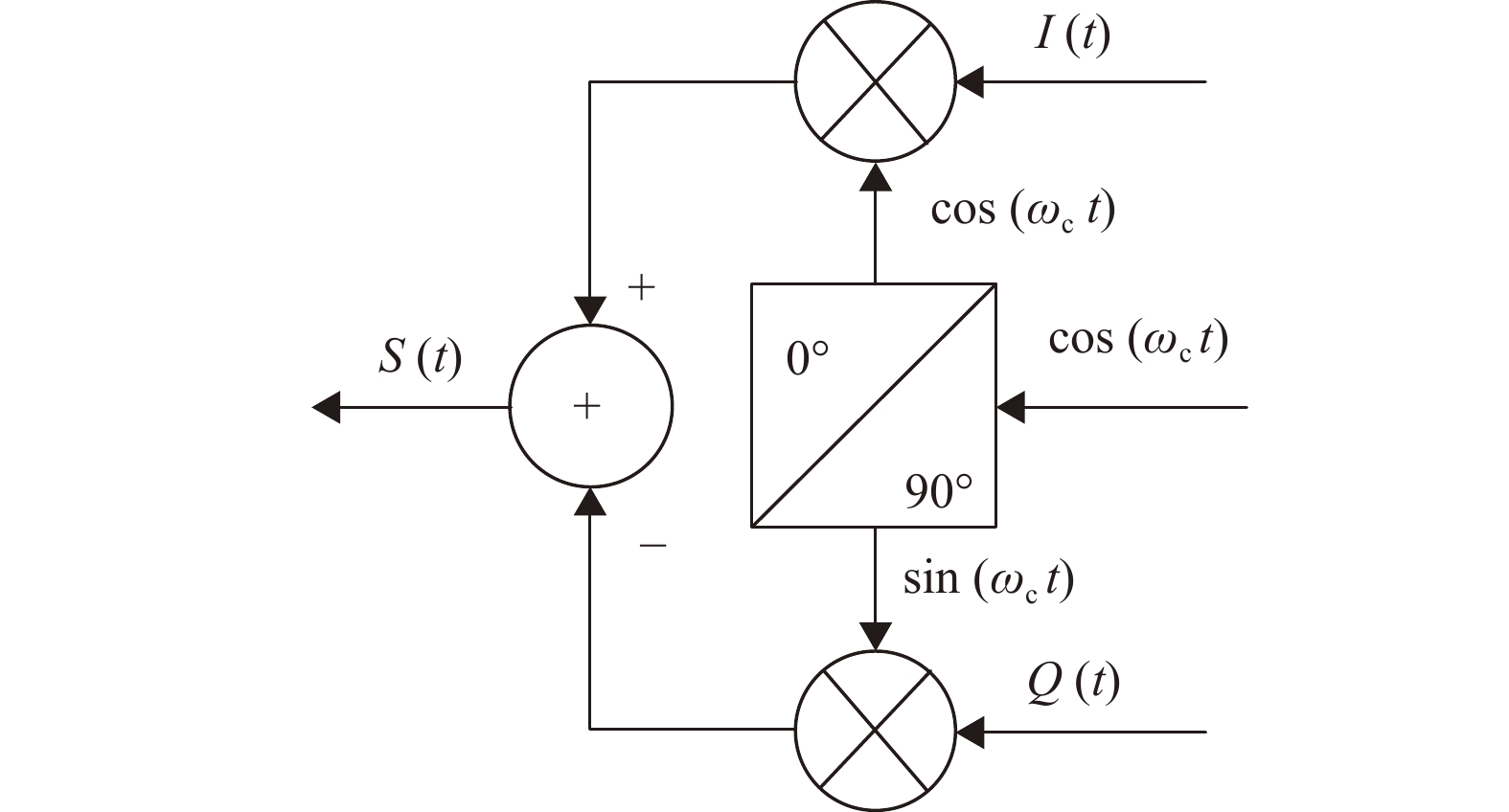

一个典型的直接变频发射机架构如图1所示,其中

$ I({{t}}) $ 和$ Q({{t}}) $ 是两路正交基带信号,$ \cos (\omega t) $ 和$ \sin (\omega t) $ 是两路正交的载波信号,$ S({{t}}) $ 为输出信号:理想的直接变频发射机输出是一个单边带信号,不存在边带泄露和载波泄露问题。实际的集成电路具有离散性和非线性特征,导致直接变频发射机不是理想状态,输入的I/Q信号存在幅相不平衡、直流失调等问题,因此输出信号也存在幅相不平衡,所以传统的直接变频发射机存在边带泄露和载波泄露等问题。

为了便于分析问题,将基带信号和载波信号表示成带误差变量的形式:

整理后得到:

式中,

${S_{{\rm{usb}}}}({{t}})$ 是有用的上边带信号;${S_{{\rm{dsb}}}}({{t}})$ 是干扰的下边带信号;${S_{{\rm{cl}}}}({{t}})$ 是干扰的载波泄露信号;${S_{{\rm{bl}}}}({{t}})$ 是干扰的基带泄露信号;${S_{{\rm{dc}}}}({{t}})$ 是干扰的直流偏移信号。由式(5)可知,边带镜像来源于I/Q信号和载波信号的幅相不平衡;由式(6)可知,载波泄露来源于I/Q信号的直流失调和载波信号的幅相不平衡;由式(7)可知,基带泄露来源于载波信号的直流失调和I/Q信号的幅相不平衡;由式(8)可知,直流偏移来源于载波信号和I/Q信号的直流失调。

传统的直接变频架构中,存在式(3)所包含的基带泄露、直流泄露、载波泄露和边带镜像,恶化了误差矢量幅度(error vector magnitude, EVM)和相邻信道功率比(adjacent channel power ratio, ACPR)。

-

直接变频架构收发器已经存在很多年,但I/Q平衡、镜像抑制、LO泄漏和直流失调等问题限制了其应用。ADI公司首先采用智能硅片设计和高级校准算法,克服了上述缺点[9]。直接变频收发器不但会在初始化时自动跟踪并校正这些误差,还能随着时间、温度、电源和流程自动跟踪和校正。设计中可以存在影响信号路径的因素,但智能硅片设计将这些影响降到最低,误差通过正交误差校正(orthogonal error correction, QEC)算法消除。

在直接变频收发器上,QEC算法在片内ARM处理器中执行。它实时监测内部信号路径、射频输出、输入信号和外部系统环境的信息,智能预测信号路径,而不是做出本能的被动式反应。该算法性能出色,以数字方式辅助模拟信号路径发挥最佳性能。

-

传统的射频微系统仅仅是射频前端的小型化,不包含FPGA等基带处理电路,无法实现基带信号处理功能。

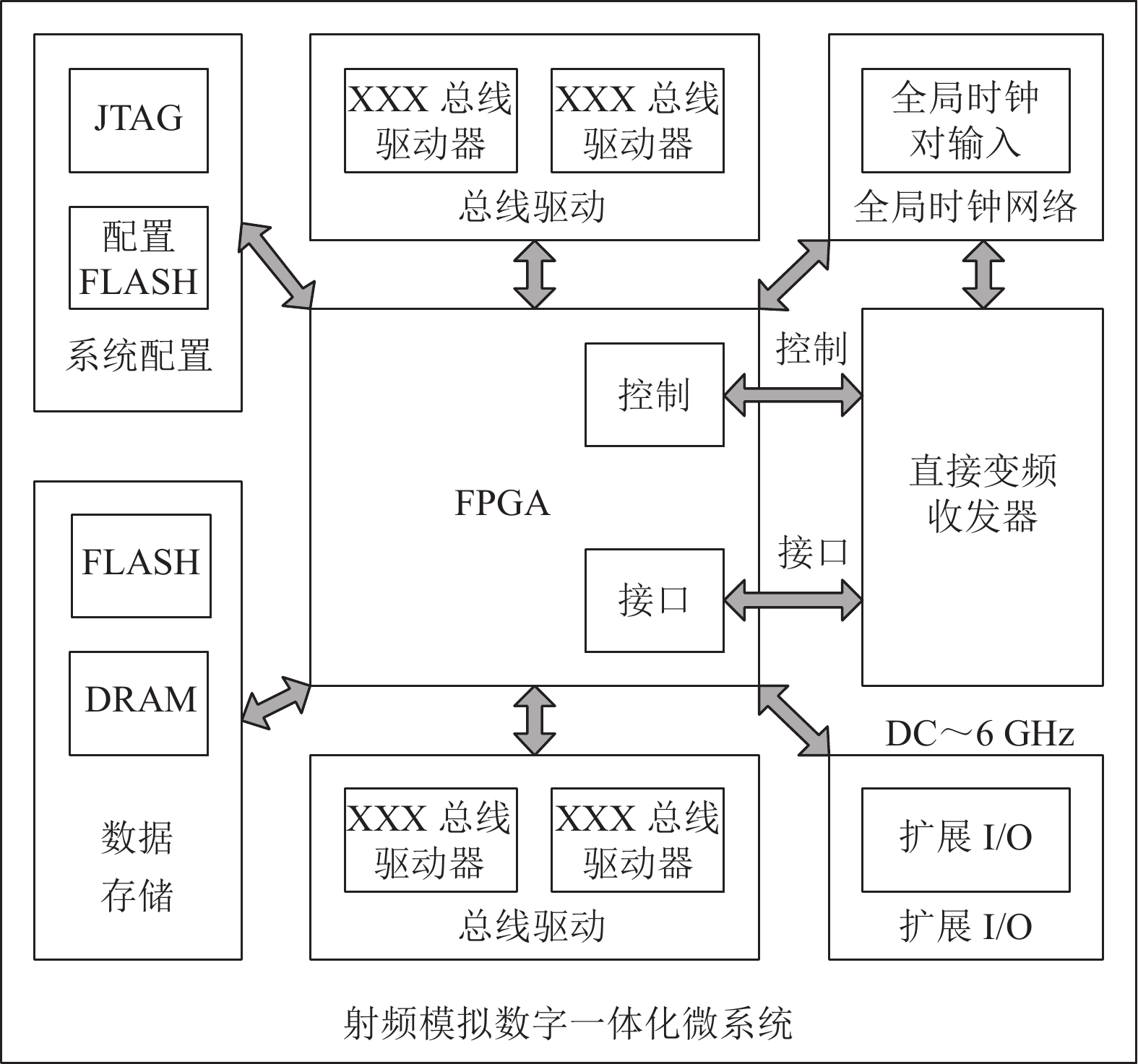

本文基于系统级射频模拟数字一体化设计思想,采用“直接变频收发器+FPGA”的核心架构,设计了一款新型的射频微系统。和传统的全模拟信号射频微系统相比,硬件上增加了基带处理电路、存储电路和驱动电路等数字电路,软件上增加了信号处理算法。整个微系统跨越射频模拟数字全信号链路,是真正意义上的微系统,其架构如图2所示。

-

由于应用场景对射频前端的尺寸、体积要求非常高,传统射频前端无法满足要求,因此必须开展微系统集成工作。

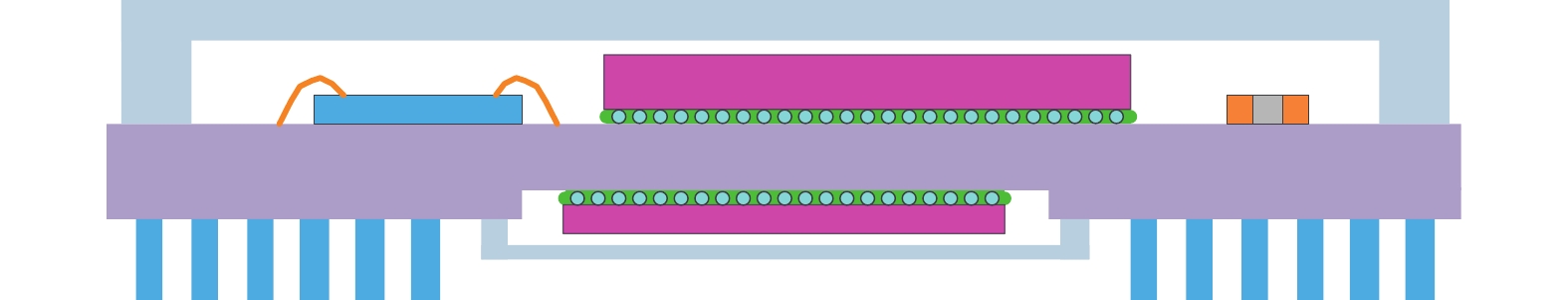

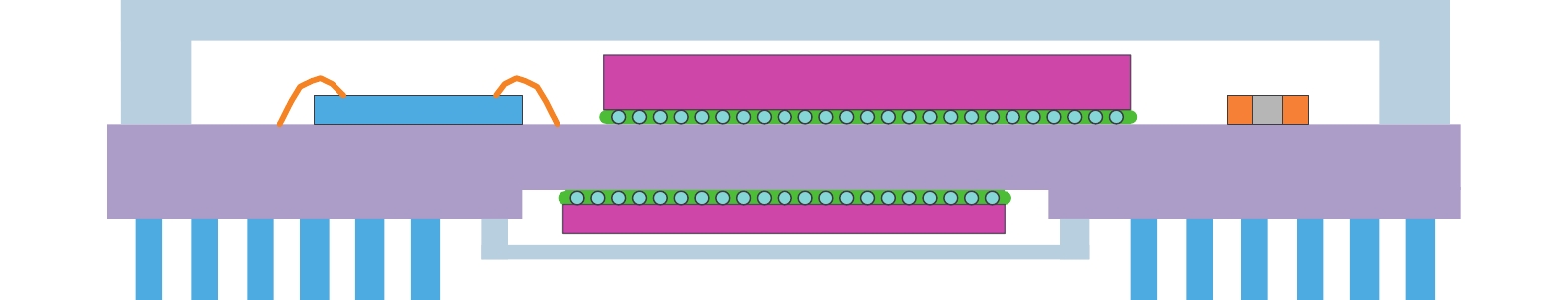

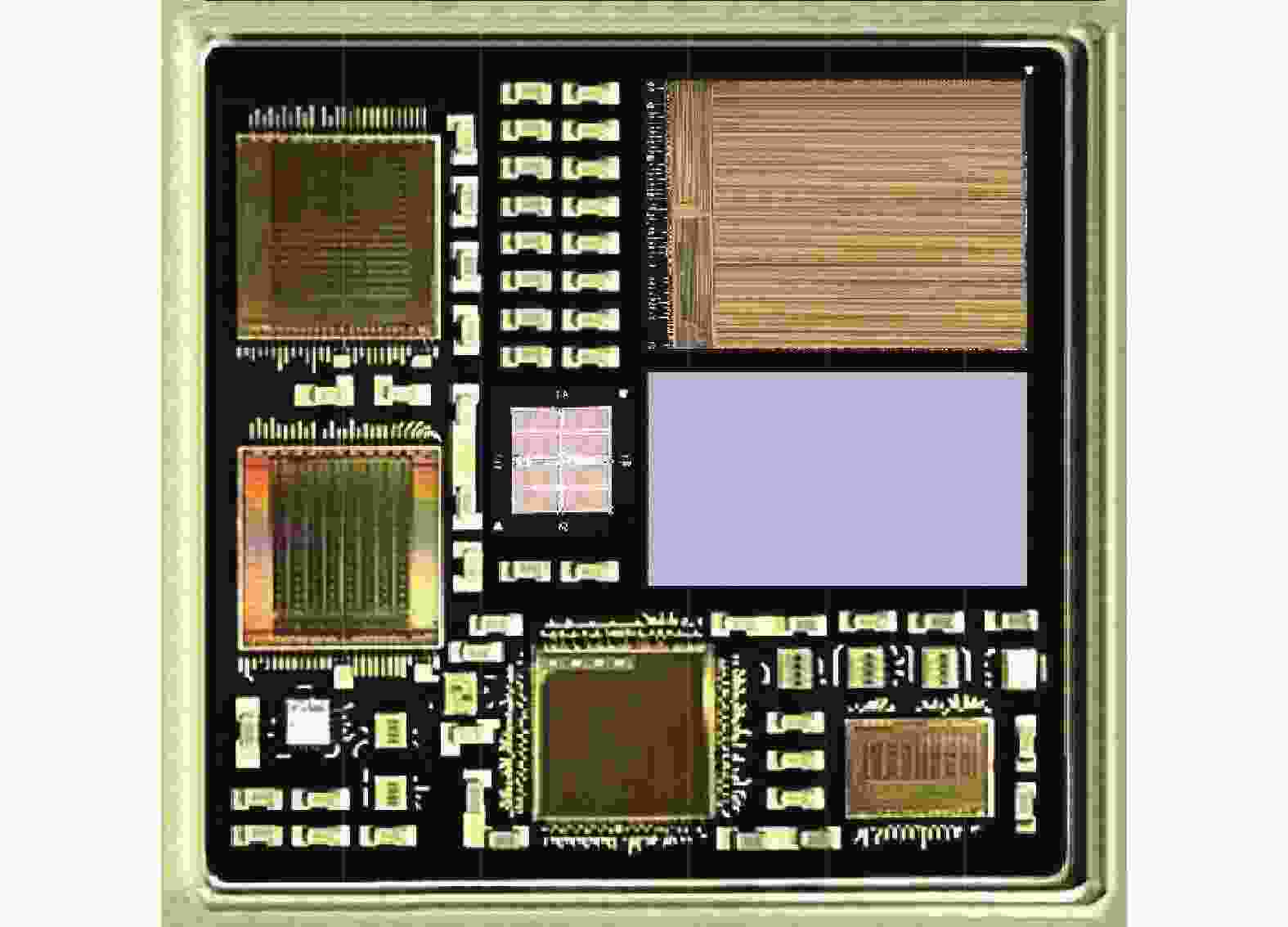

微系统需要集成多种裸芯片和一定数量的无源器件,并实现内部信号的电气互连。为了满足封装气密性、热匹配性等可靠性要求,综合考虑采用一体化陶瓷三维封装架构,如图3所示。

微系统封装方案具体设计如下。

1) 封装类型。采用HTCC陶瓷封装,设计成双面腔体结构,其中正面腔体集成数字电路,背面腔体集成射频数模混合电路,适用于高可靠气密性的应用场景[10]。

2) 扇出结构。采用成CCGA封装形式,有效解决二次装配时的热应力问题[11],进一步保证板级装配的可靠性。

3) 封装工艺。采用混合装配工艺,包括倒装焊、键合和表贴等成熟工艺,管壳封帽采用双面平行缝焊方式。

-

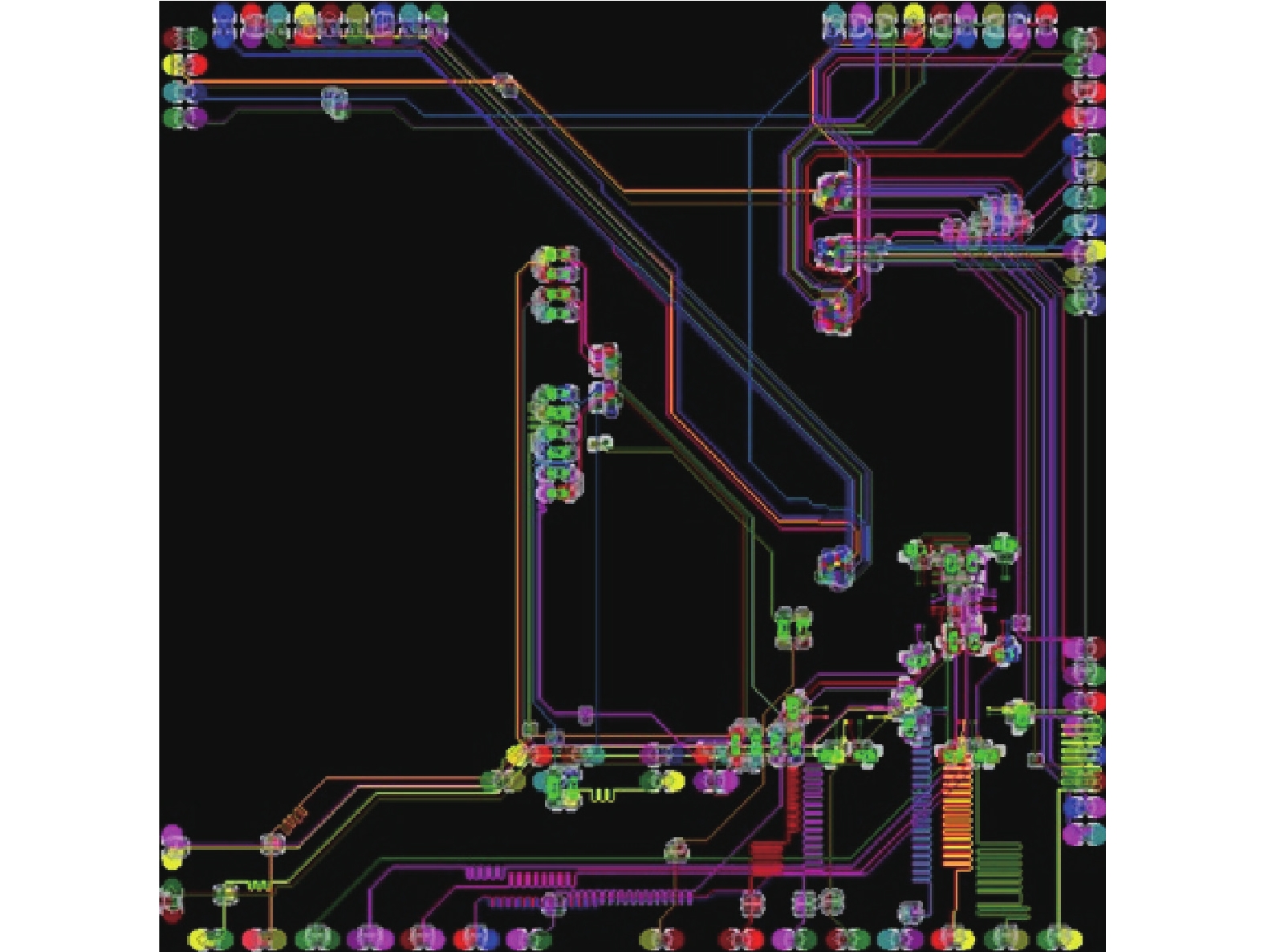

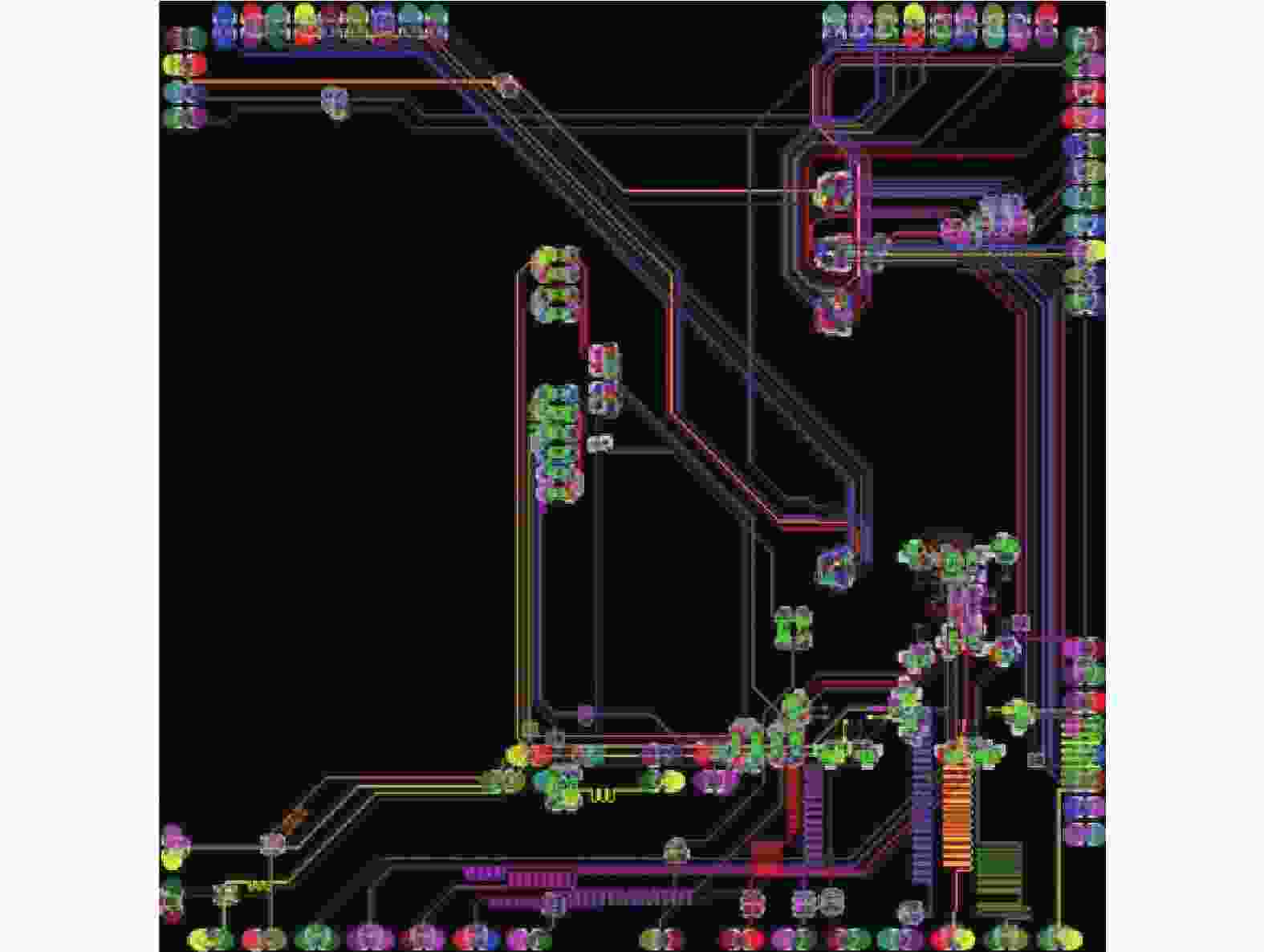

在微系统电学设计中,层叠结构规划、高密度多层布线、电源/地平面布局等是进行电学设计重点关注的问题。

1) 层叠结构规划。陶瓷封装采用40层的层叠结构,每层厚度为50 μm。总厚度控制在2 mm左右,腔深1 mm。信号线采用G-S-G结构,即金属-信号线-金属形式。

2) 高密度多层布线。微系统内部互连节点数量众多,超过8 000个,需要在多层陶瓷封装内部进行高密度布线,实现内部信号互联。

3) 电源/地平面布局。在多层布线过程中,合理地规划、设计参考电源/地平面,在保证信号回流路径最短、电磁兼容和阻抗匹配等的基础上,优化封装的结构。

-

微系统电学仿真主要包括信号完整性仿真和电源完整性仿真。

1) 信号完整性仿真

信号完整性仿真主要包括传输线信号速度和阻抗匹配计算、关键信号完整性仿真建模和串扰仿真分析。

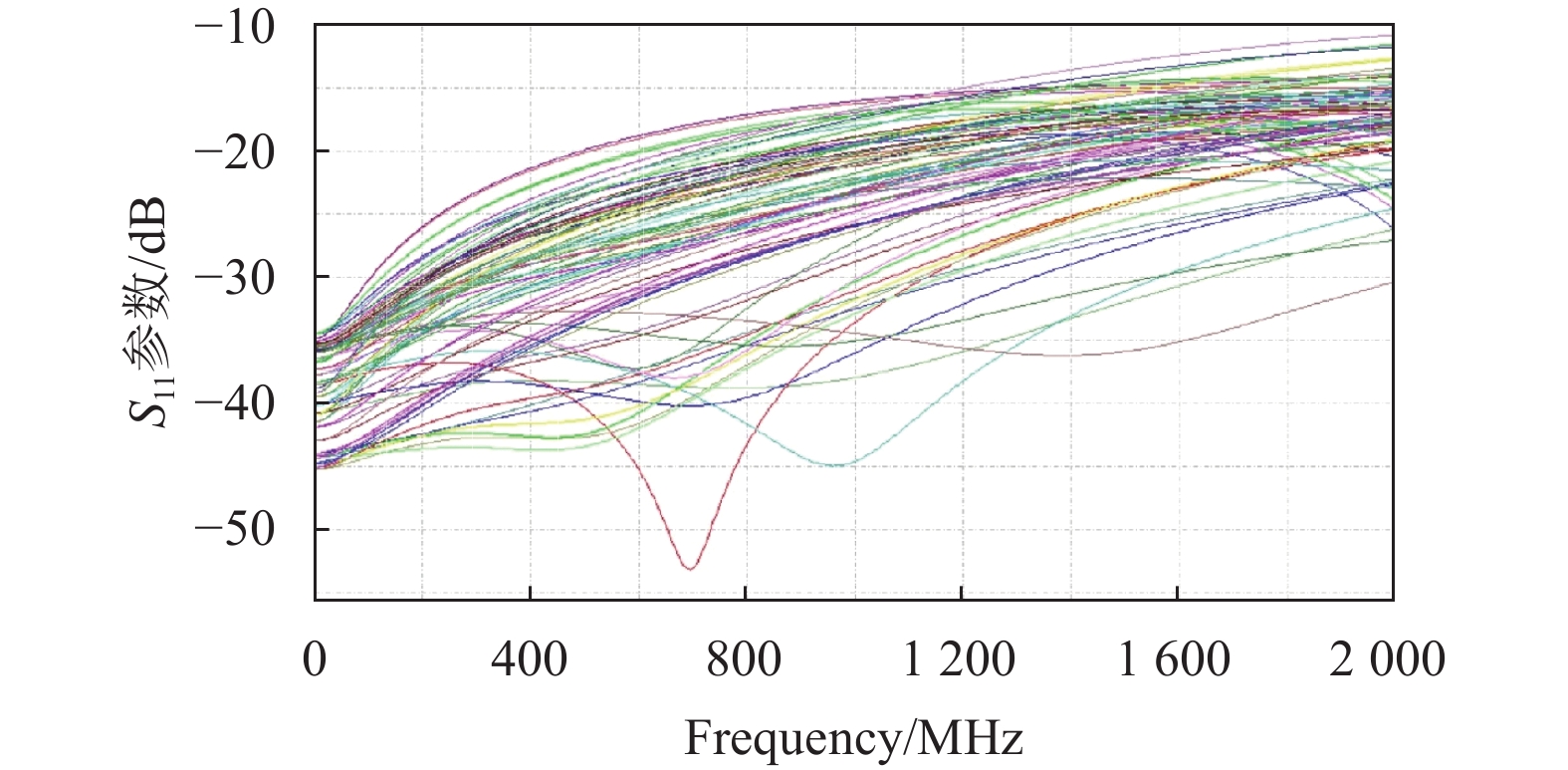

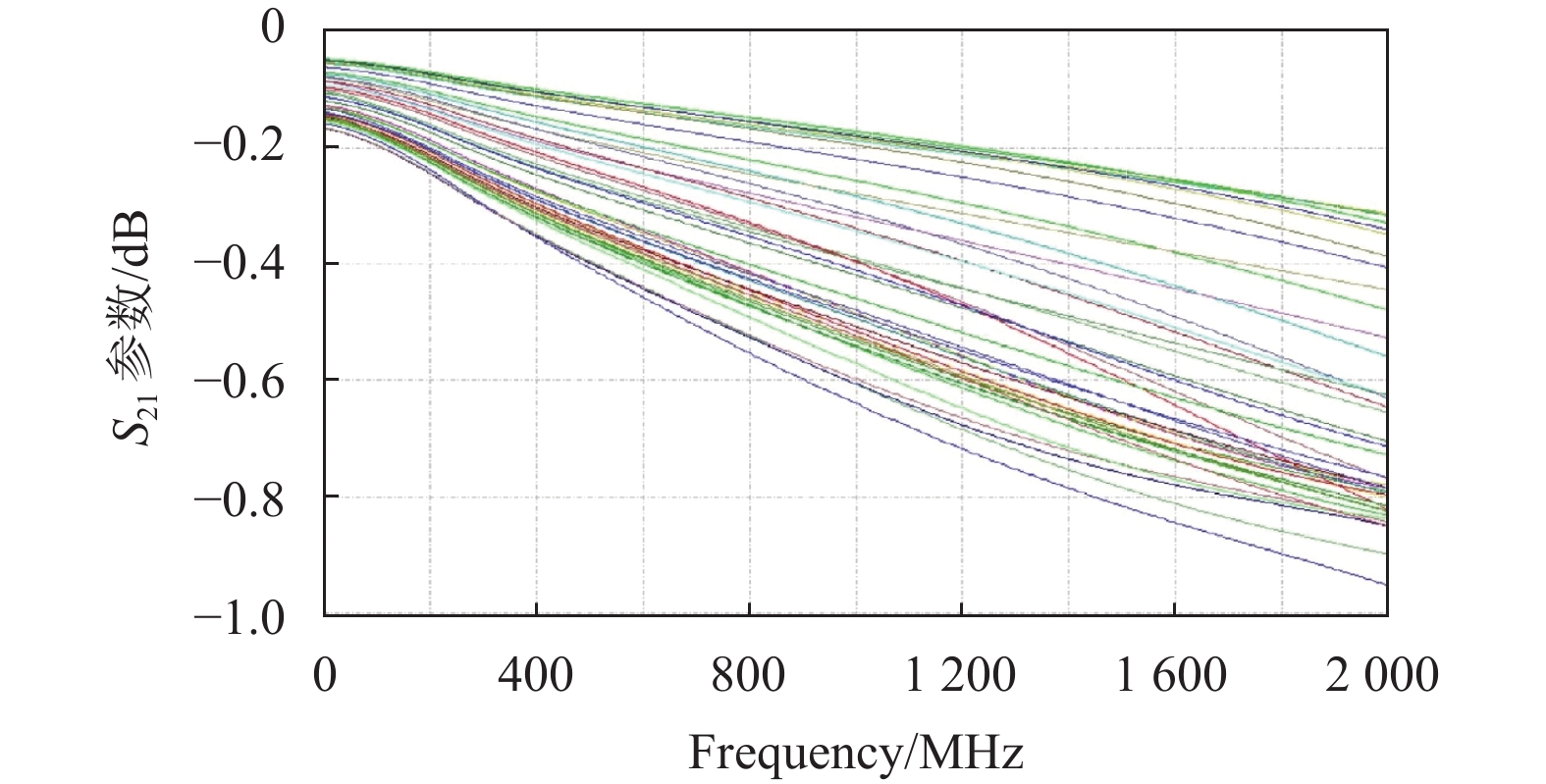

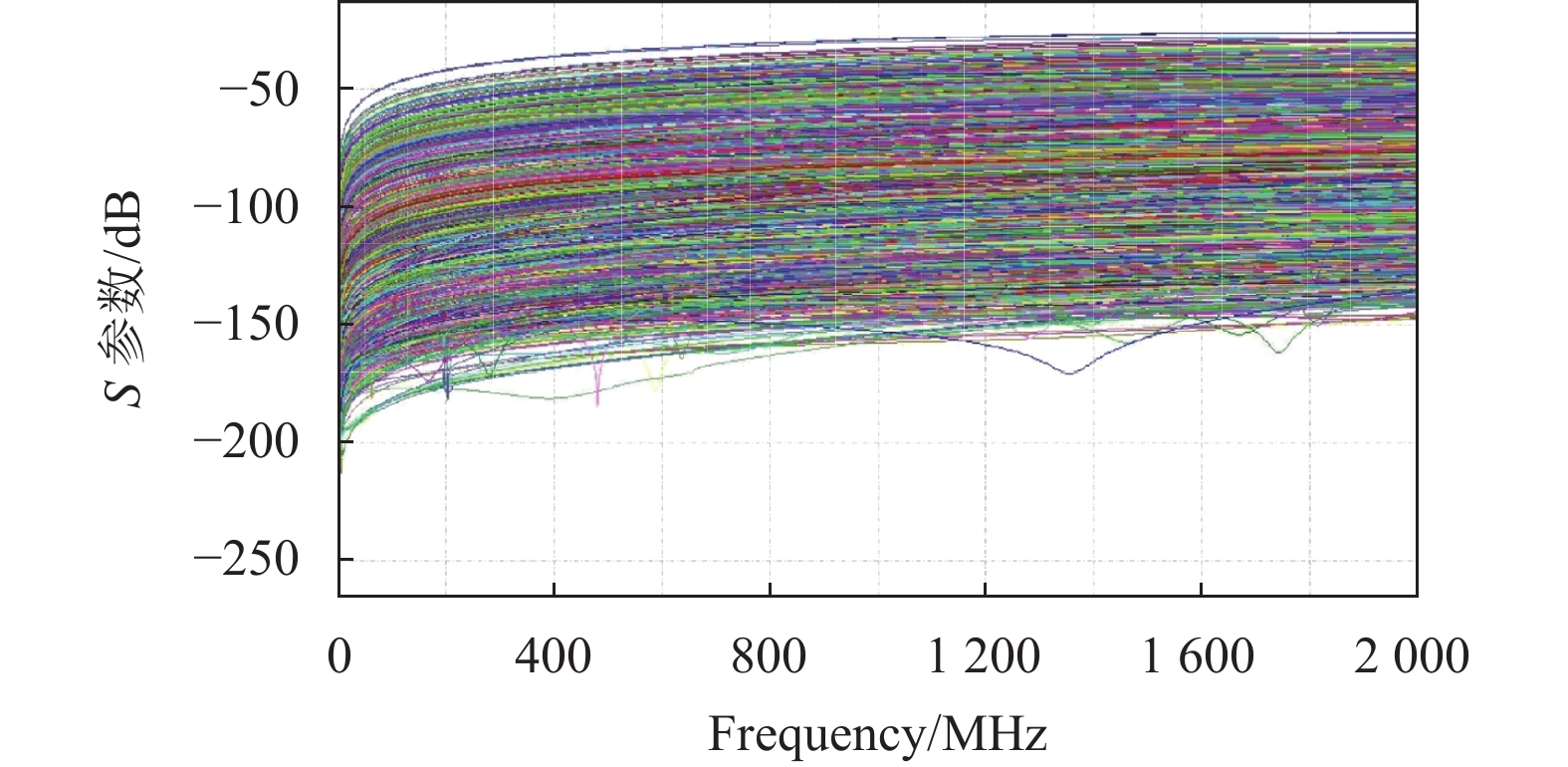

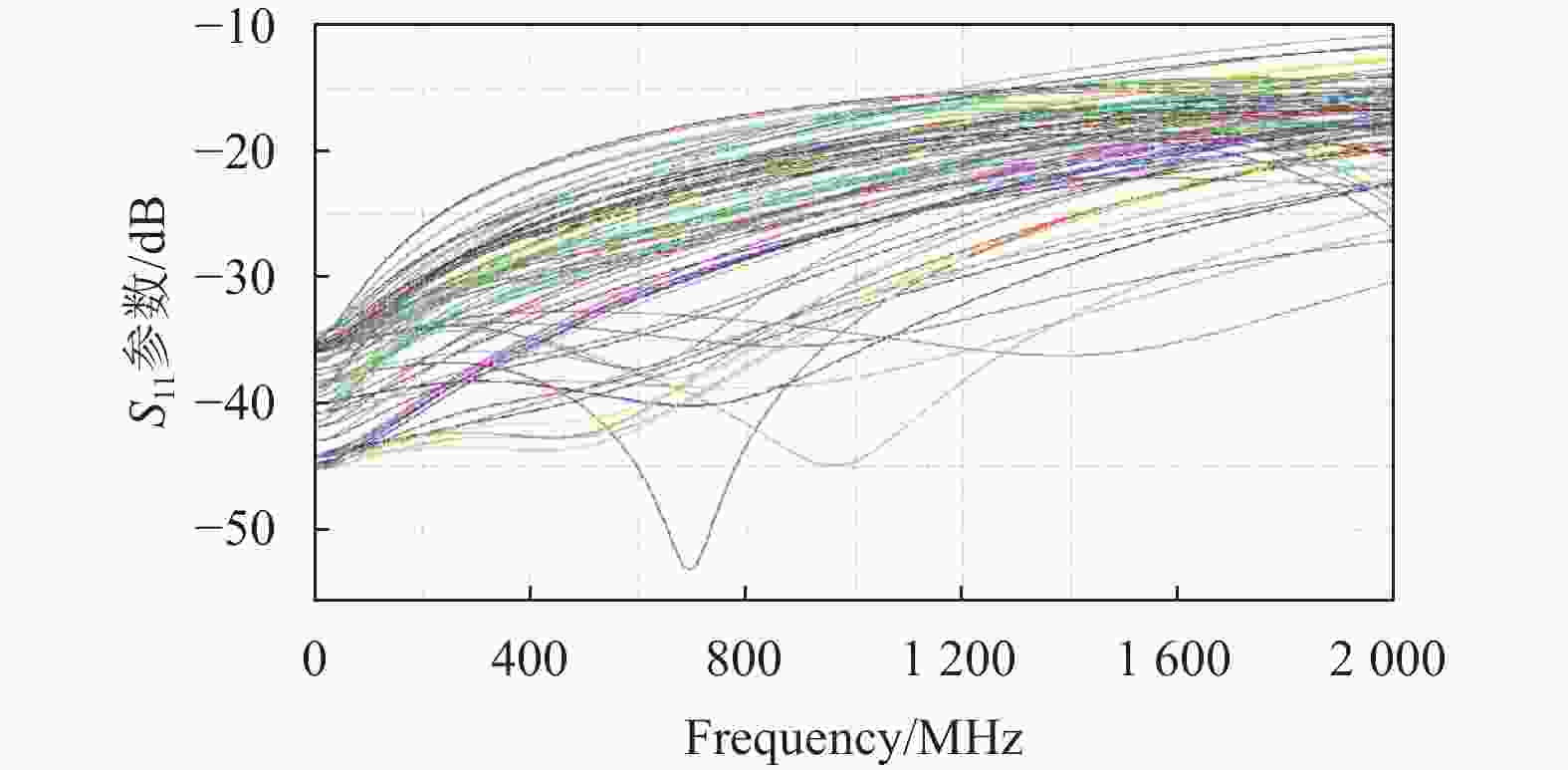

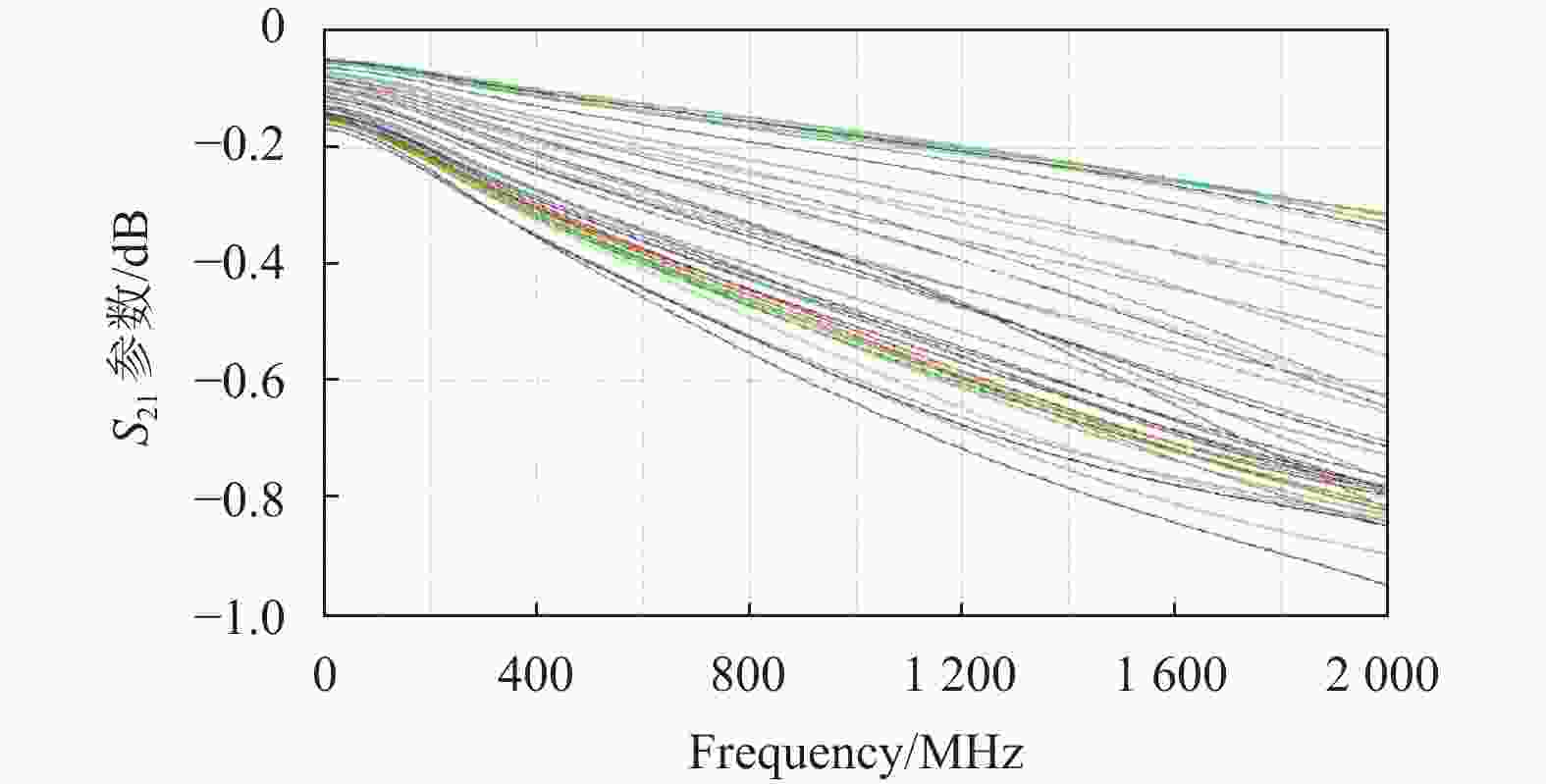

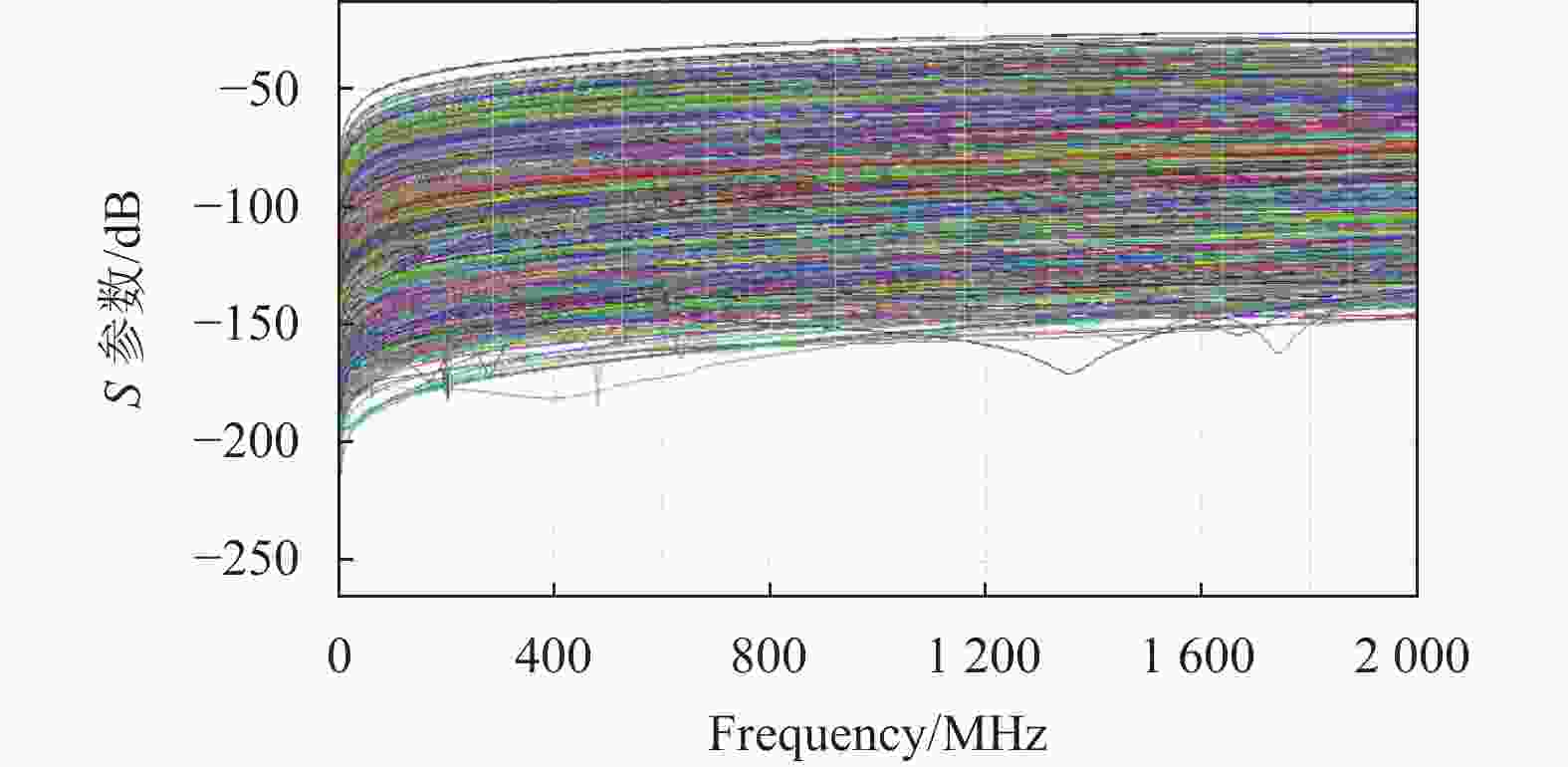

图4~图7为本封装某关键差分信号及其路径的S参数仿真结果,从图中可以看出,其仿真插入损耗S21≥−1 dB,回波损耗S11≤−10 dB,整个频率范围内的串扰S≤−20 dB,满足信号完整性的要求。

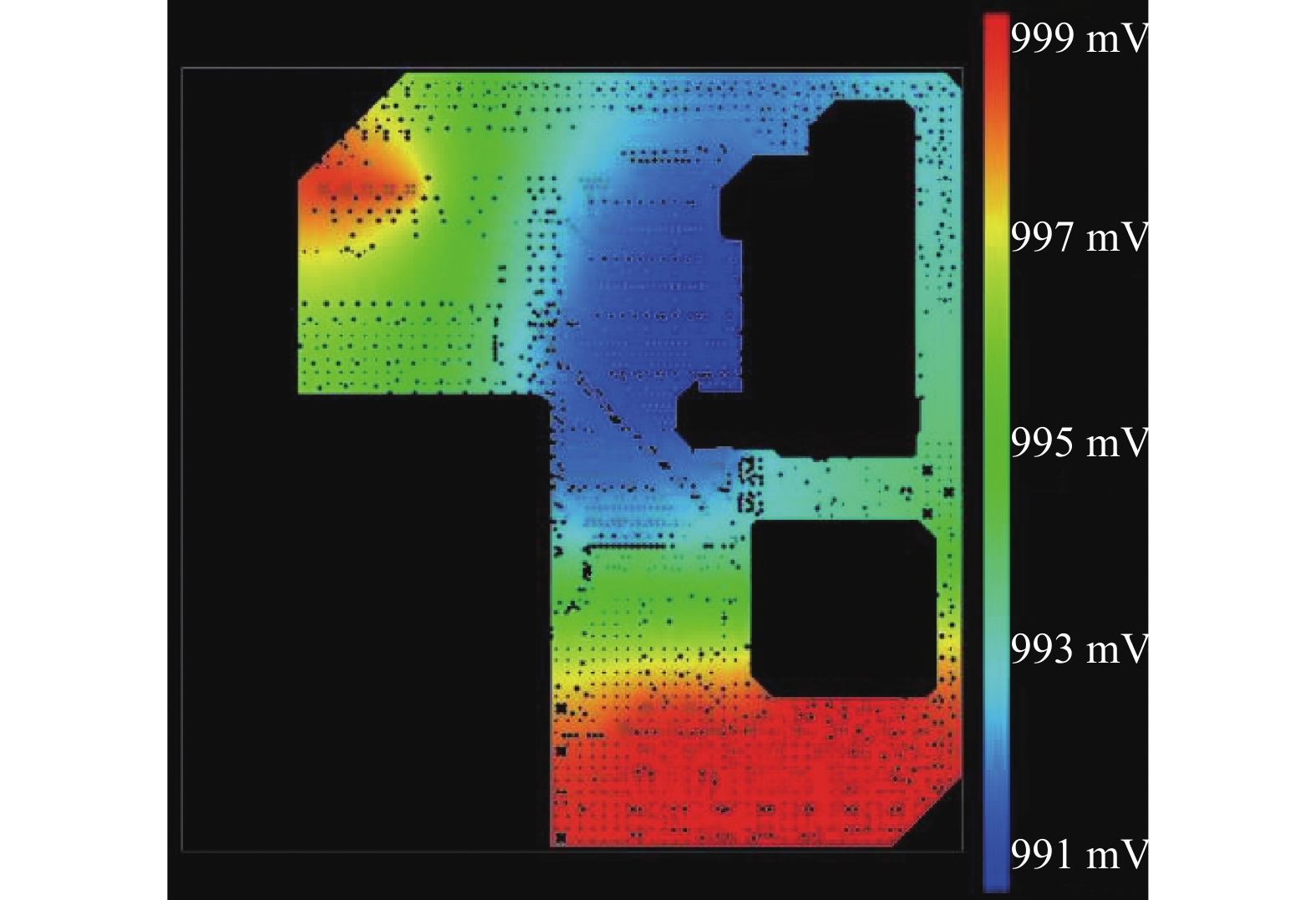

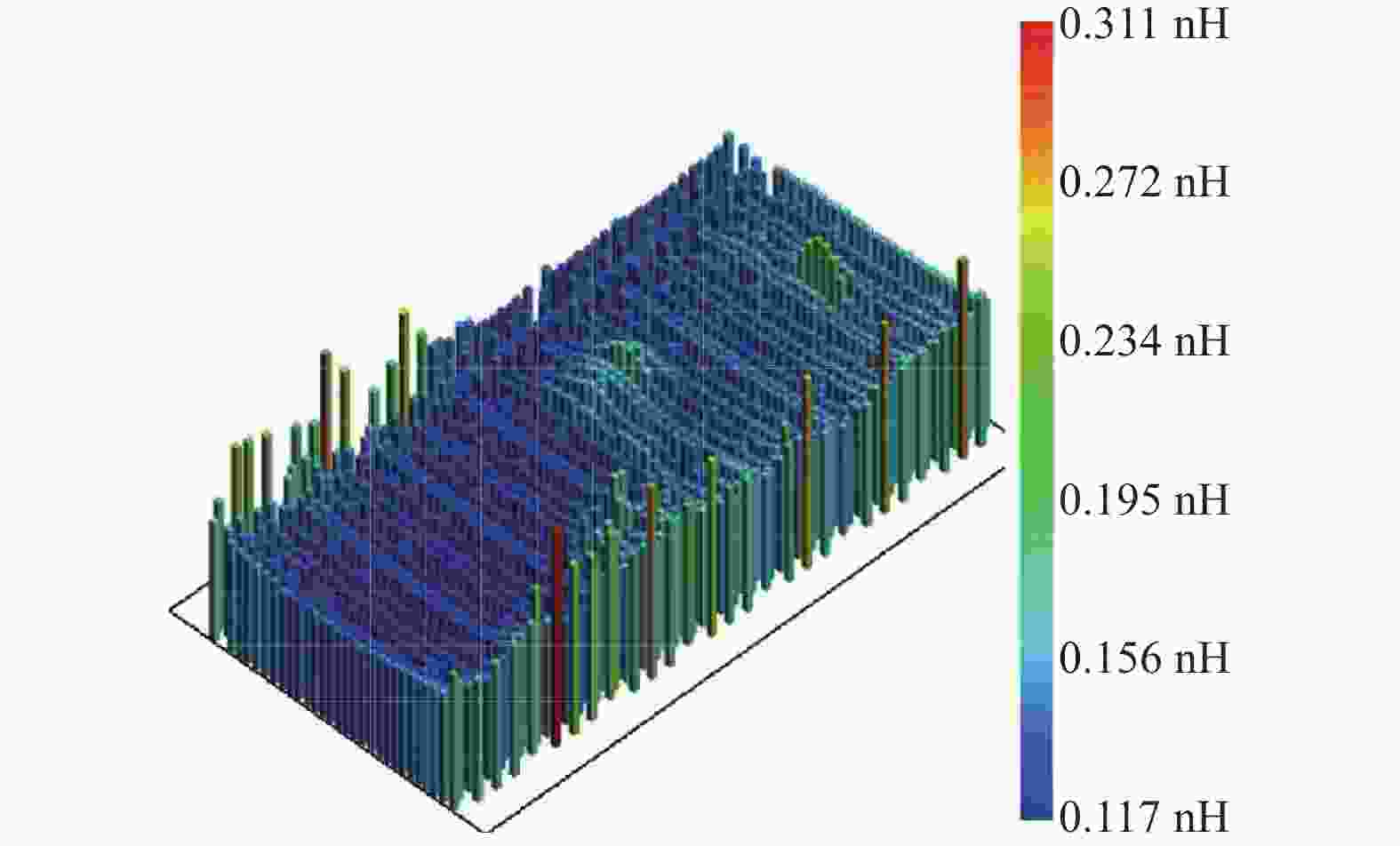

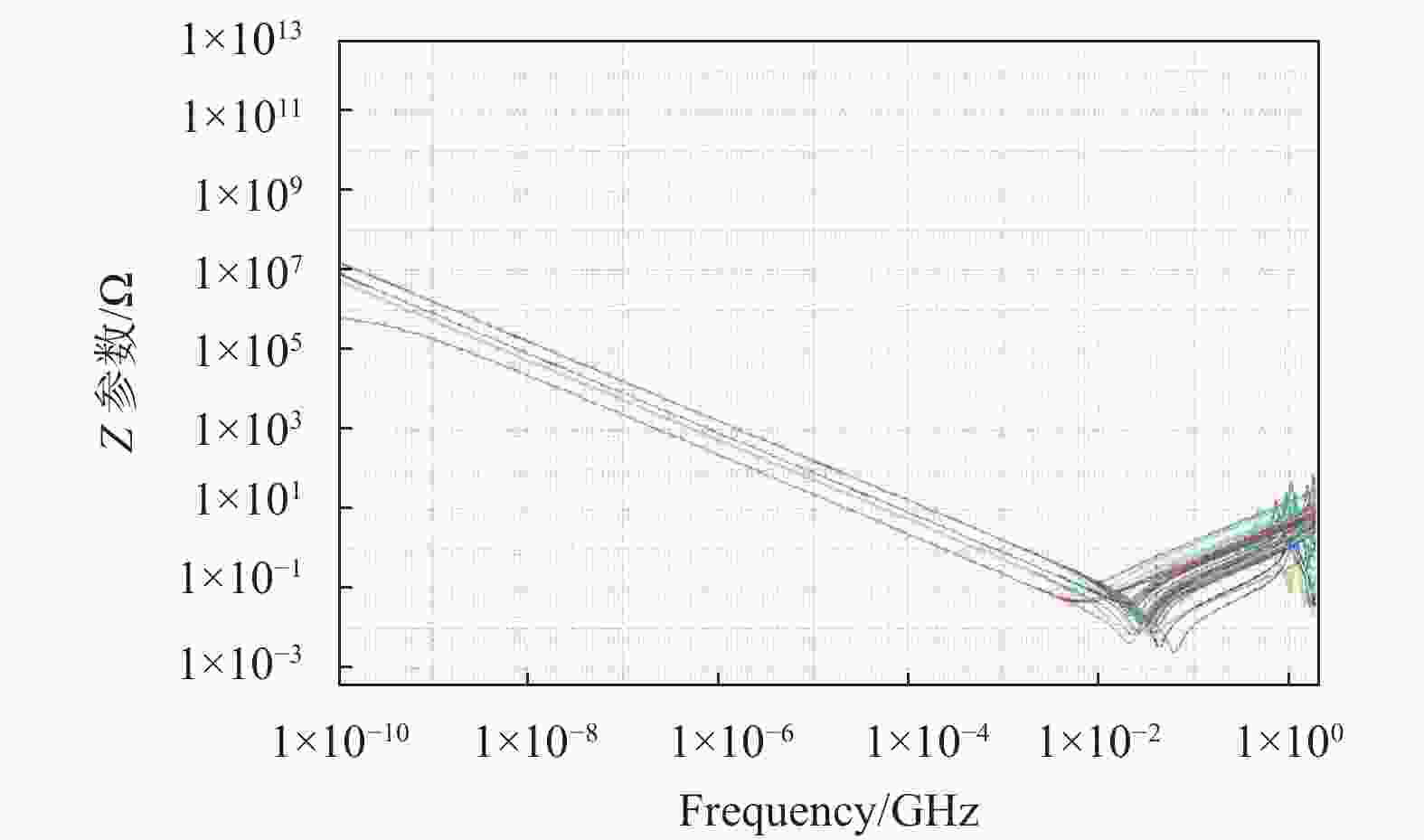

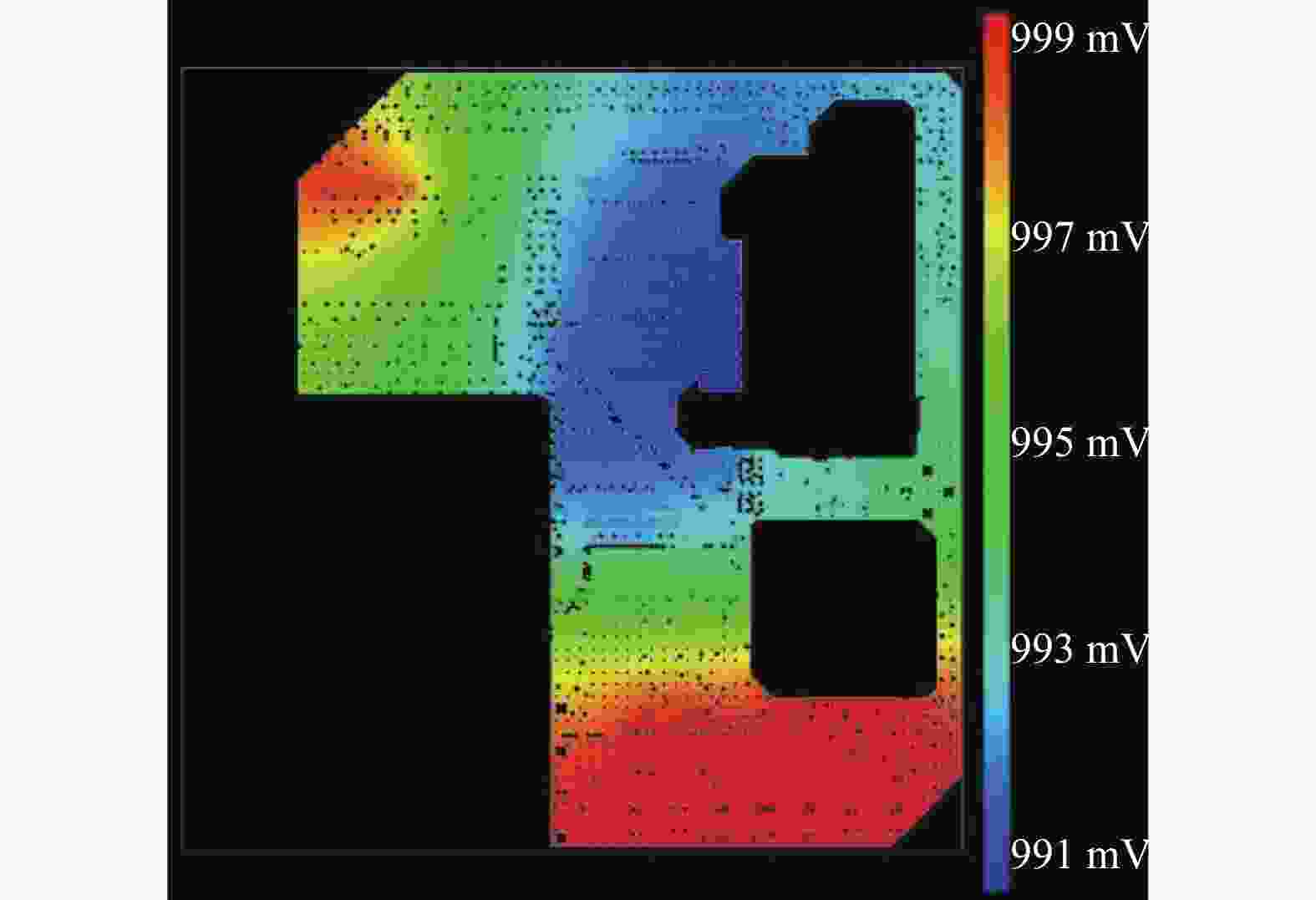

2) 电源完整性仿真

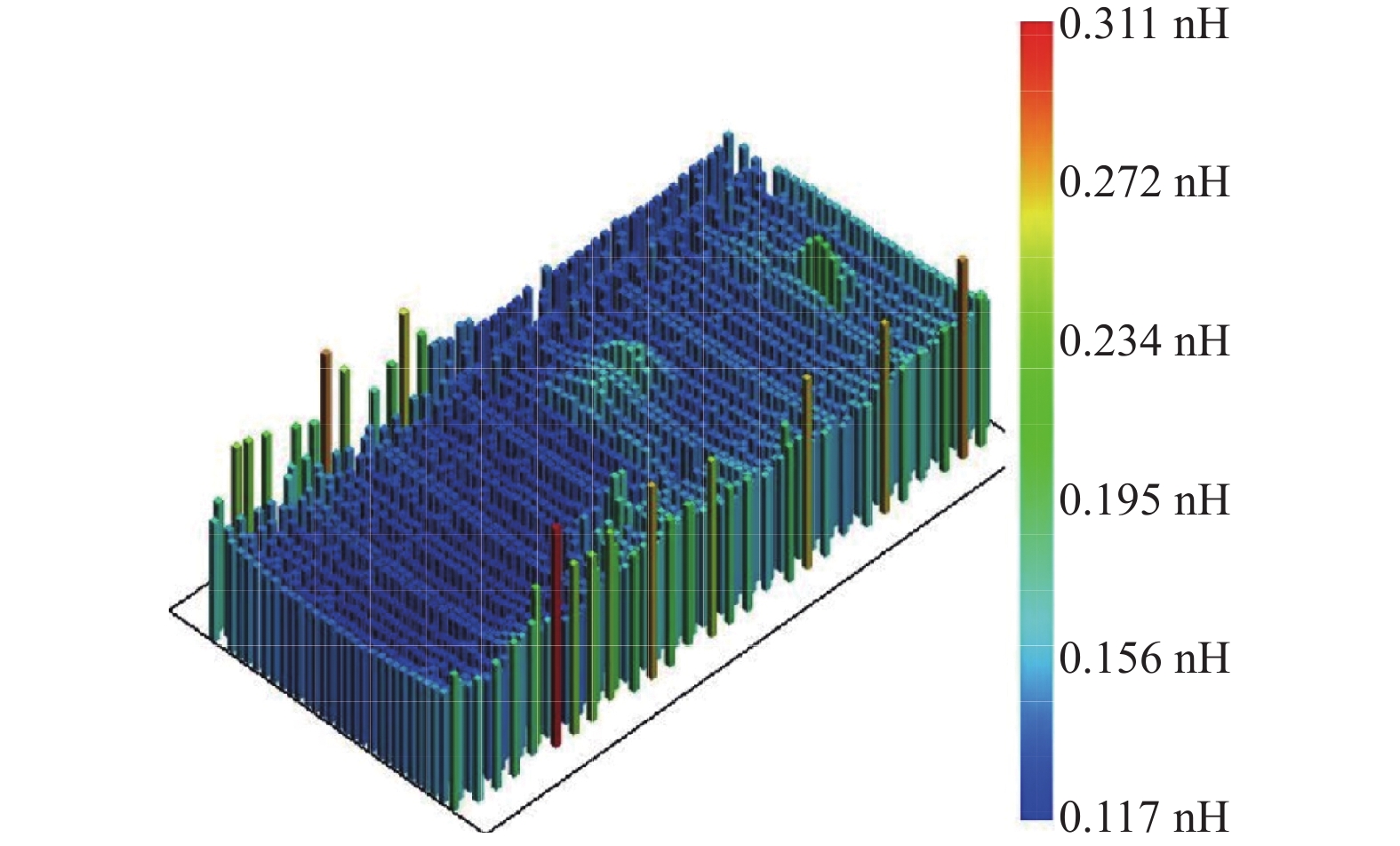

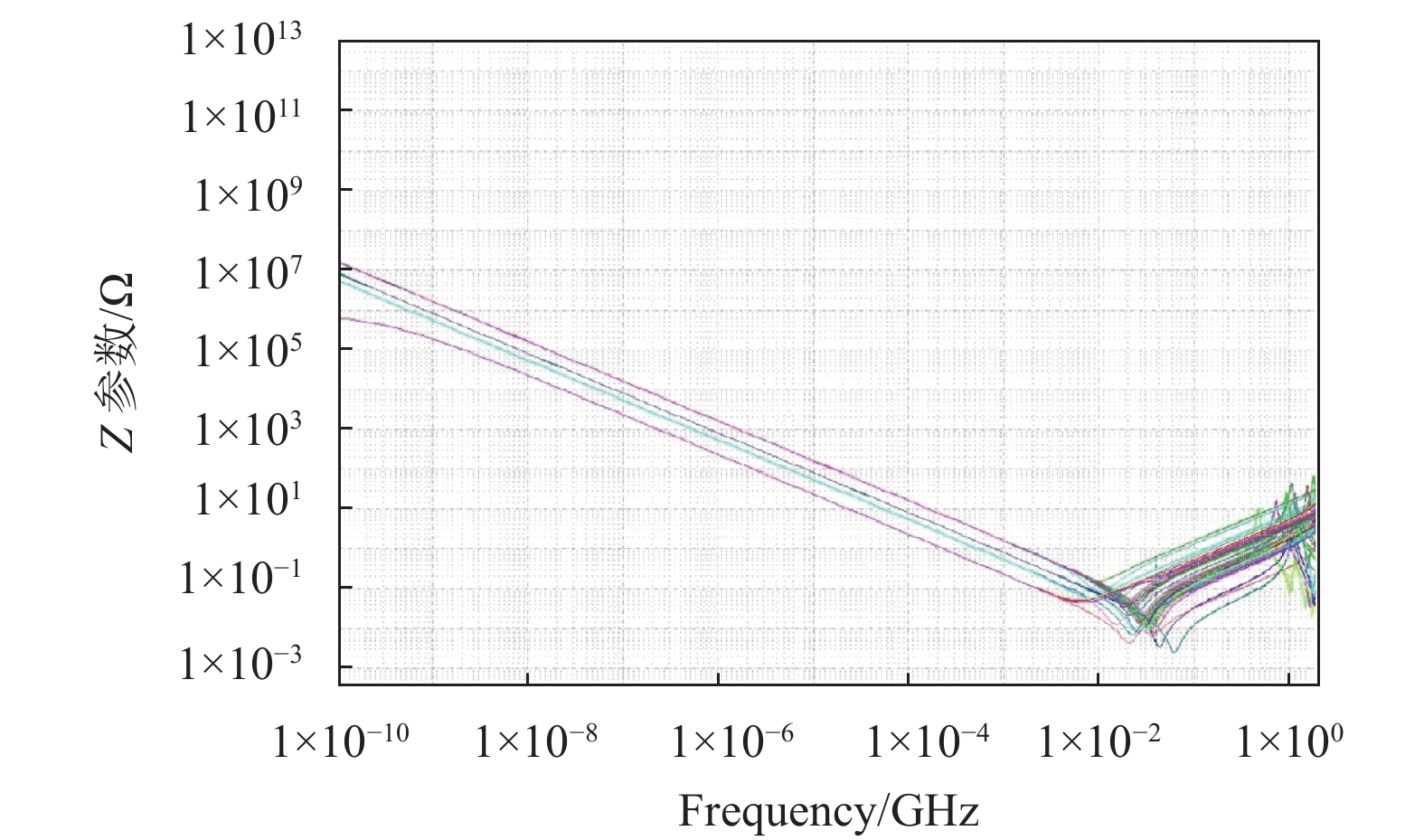

电源完整性仿真主要包括电源自回路电感仿真、电源阻抗仿真和直流压降仿真等。通过电源完整性仿真验证使电源系统更加稳健可靠。

-

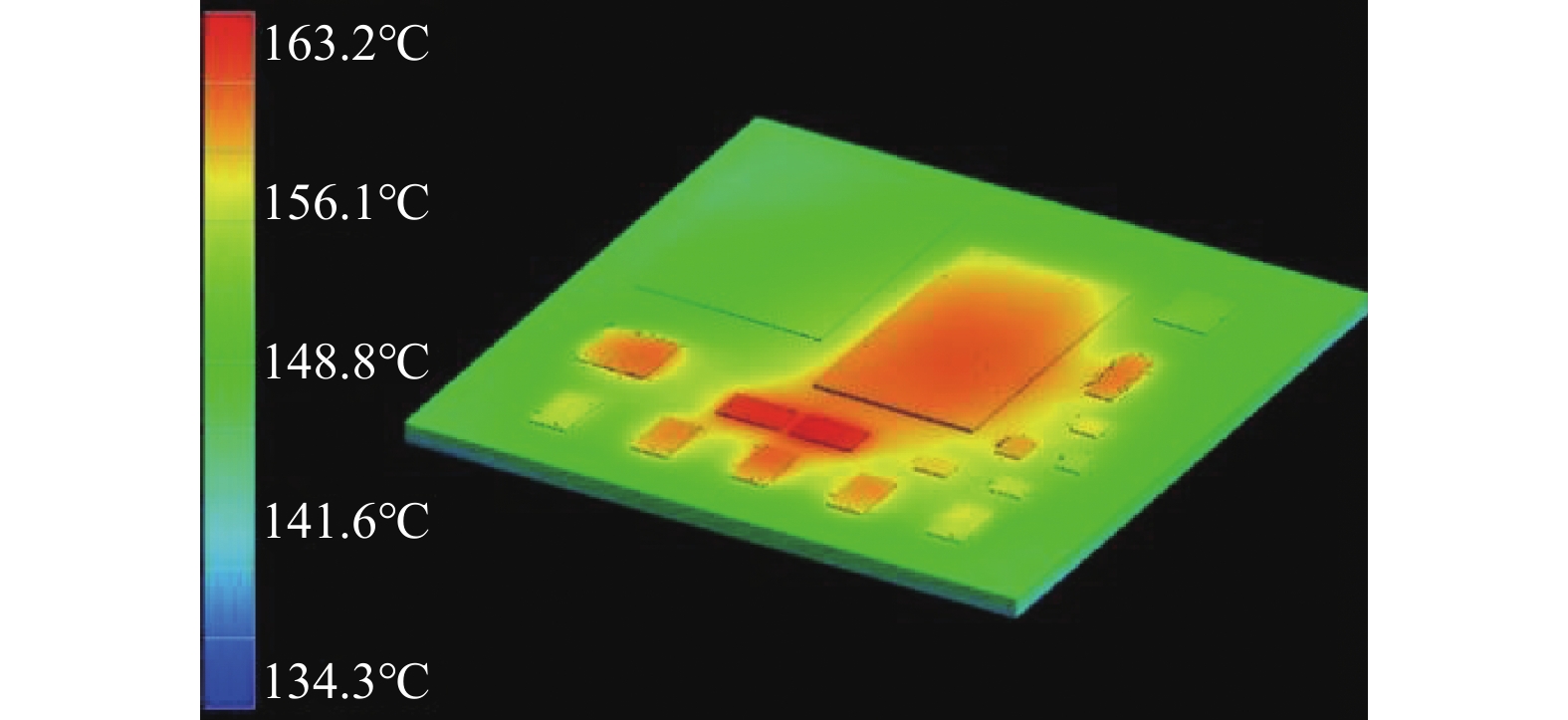

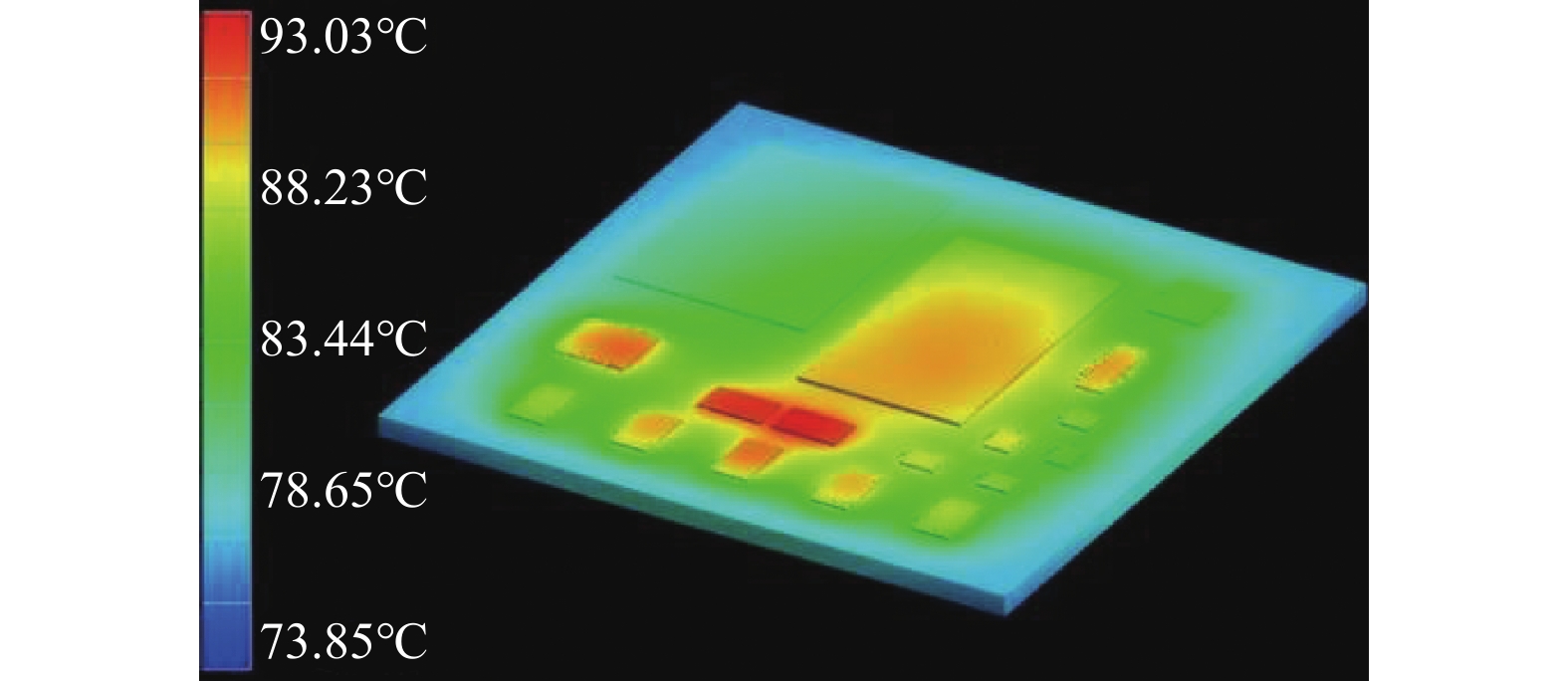

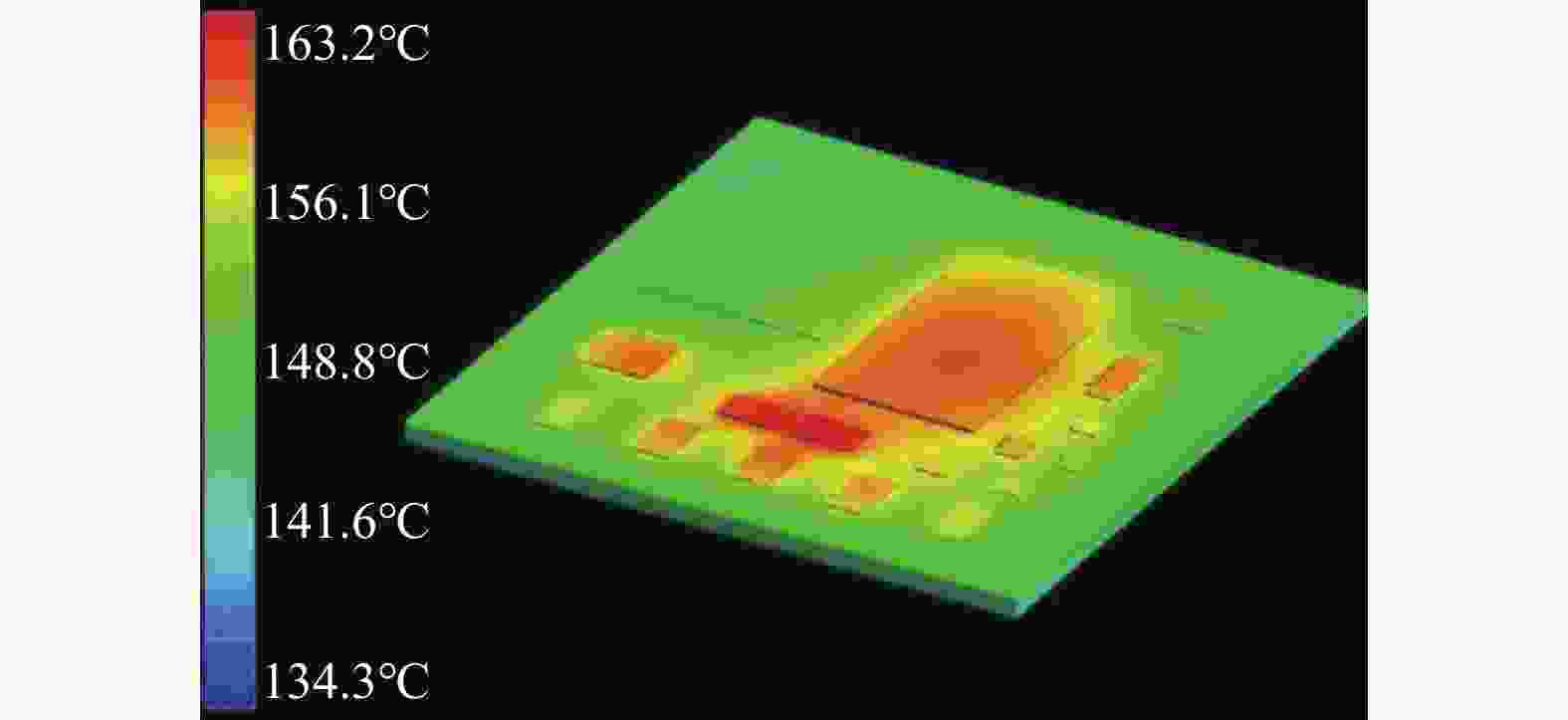

通过热设计仿真分析可以优化散热系统的设计,满足系统热设计要求。

本次仿真中,主要是评估当前热功耗及结构下,整体芯片的散热情况。图11为无散热器情况下的热仿真结果,图12为添加散热器情况下的热仿真结果,可以看出无散热片情况下芯片最高结温163.2℃;有散热片情况下芯片最高结温93.03℃。

-

为了满足封装气密性要求,陶瓷封装采用双面腔体结构,双面平行缝焊工艺封帽,具有高可靠性。

本文采用了CCGA封装结构,和CBGA相比具有更优的热疲劳性能。微系统采用直径0.51 mm/长度2.54 mm的标准焊柱,设计成1.0 mm的节距。

-

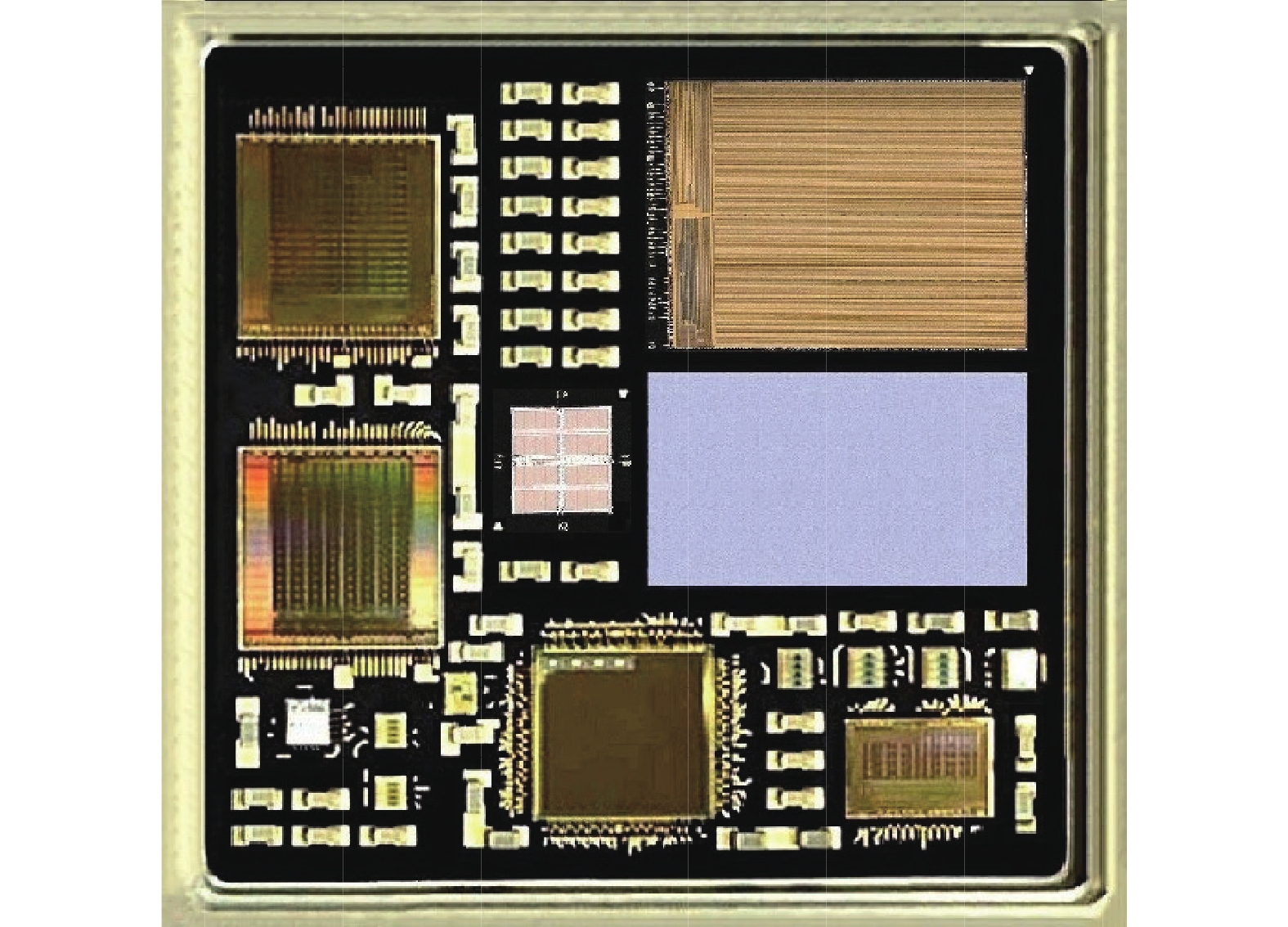

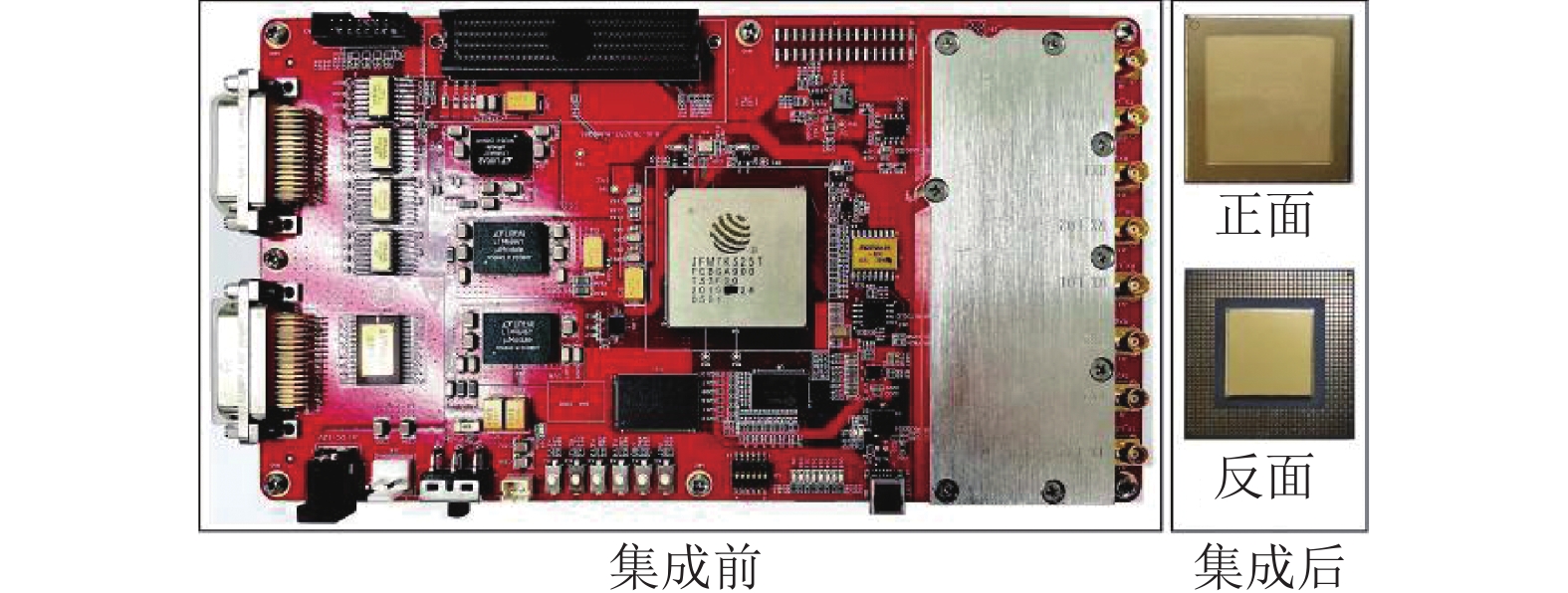

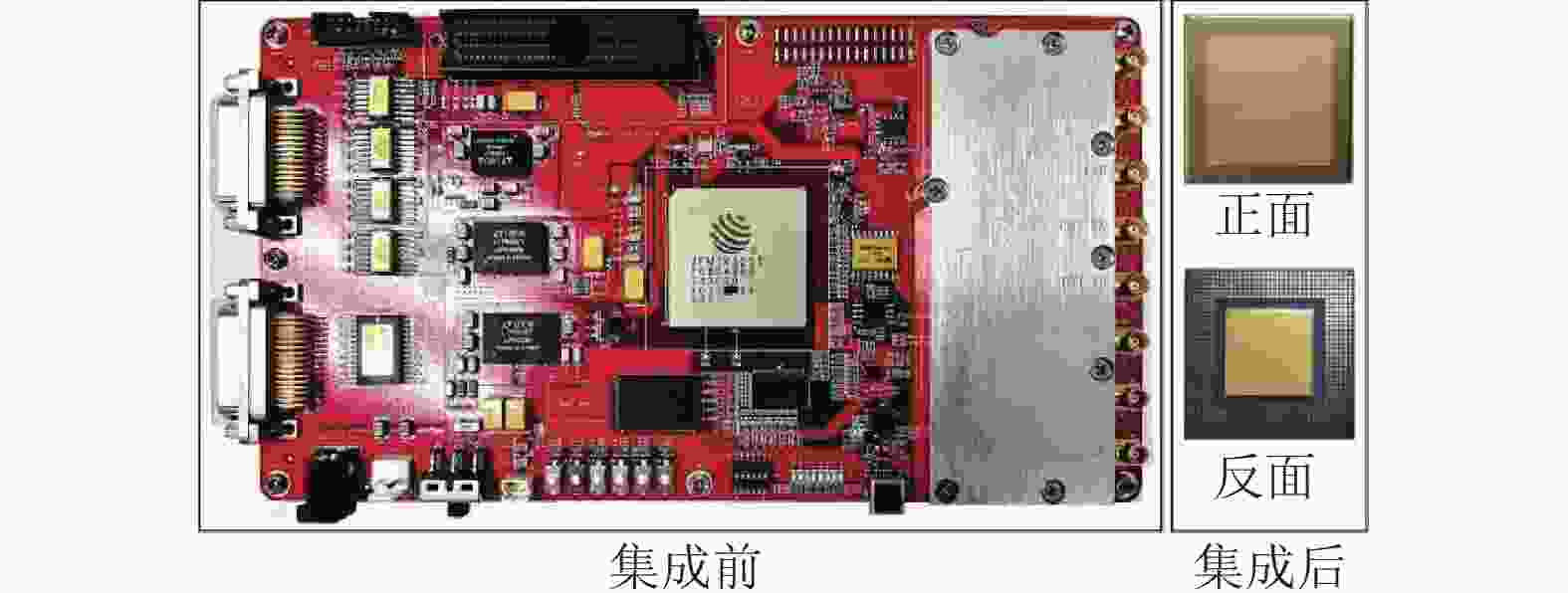

微系统集成前的尺寸为250 mm×120 mm,集成后的尺寸仅为37 mm×37 mm,面积减小95%,如图15所示。

-

1) 无人平台点对点窄带通信主要技术指标如下。

① 频率范围:S波段;

② 信源速率≥6 Mbps;

③ 载波抑制>35 dBc;

④ 镜频抑制>35 dBc。

2) 原型验证

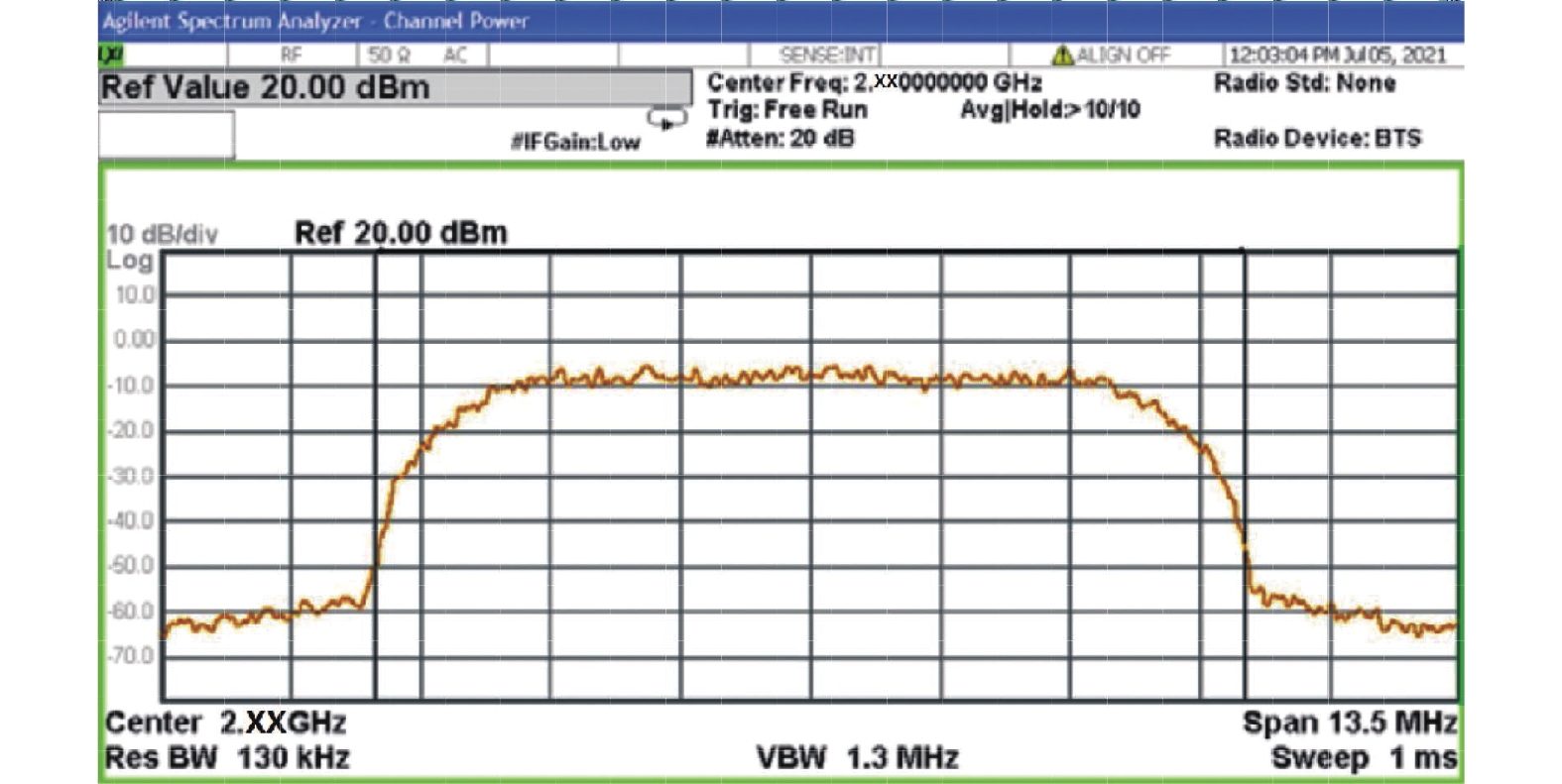

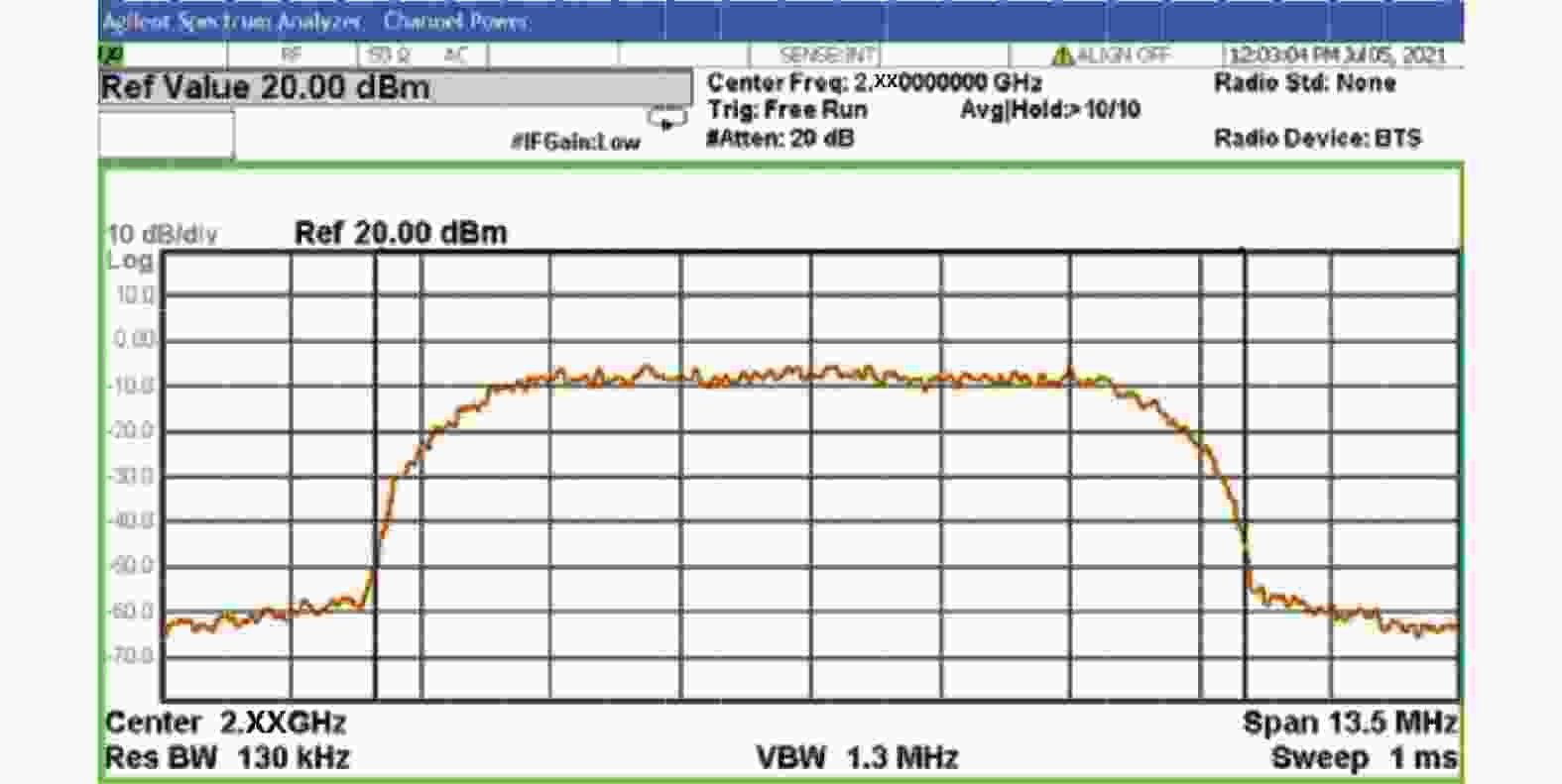

经过测试,发射信号频谱中心频率在2.XX GHz,带宽>8 MHz,因此指标①②满足要求,如图16所示。

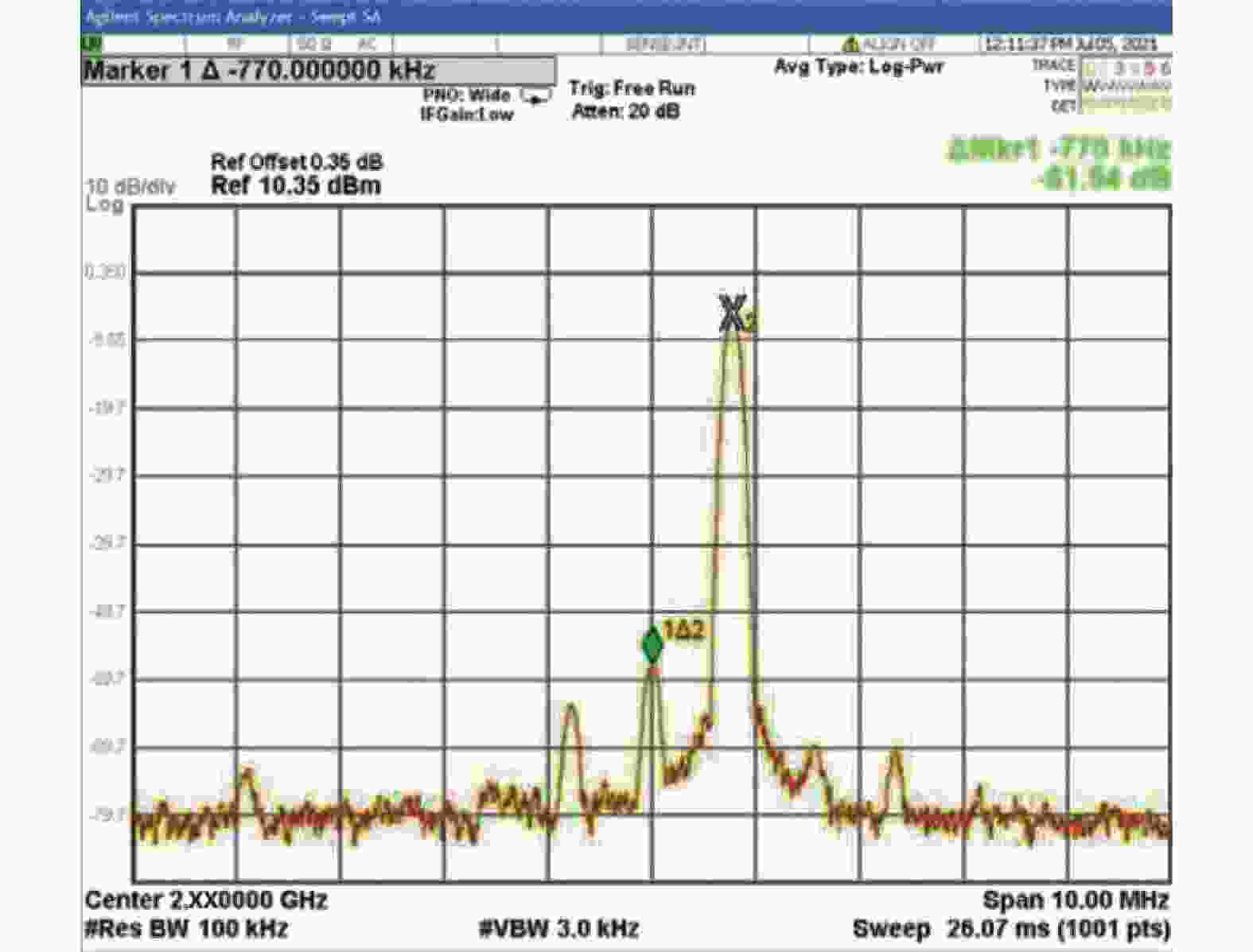

发射信号载波抑制实测值为51.54 dB,满足要求指标③,如图17所示。

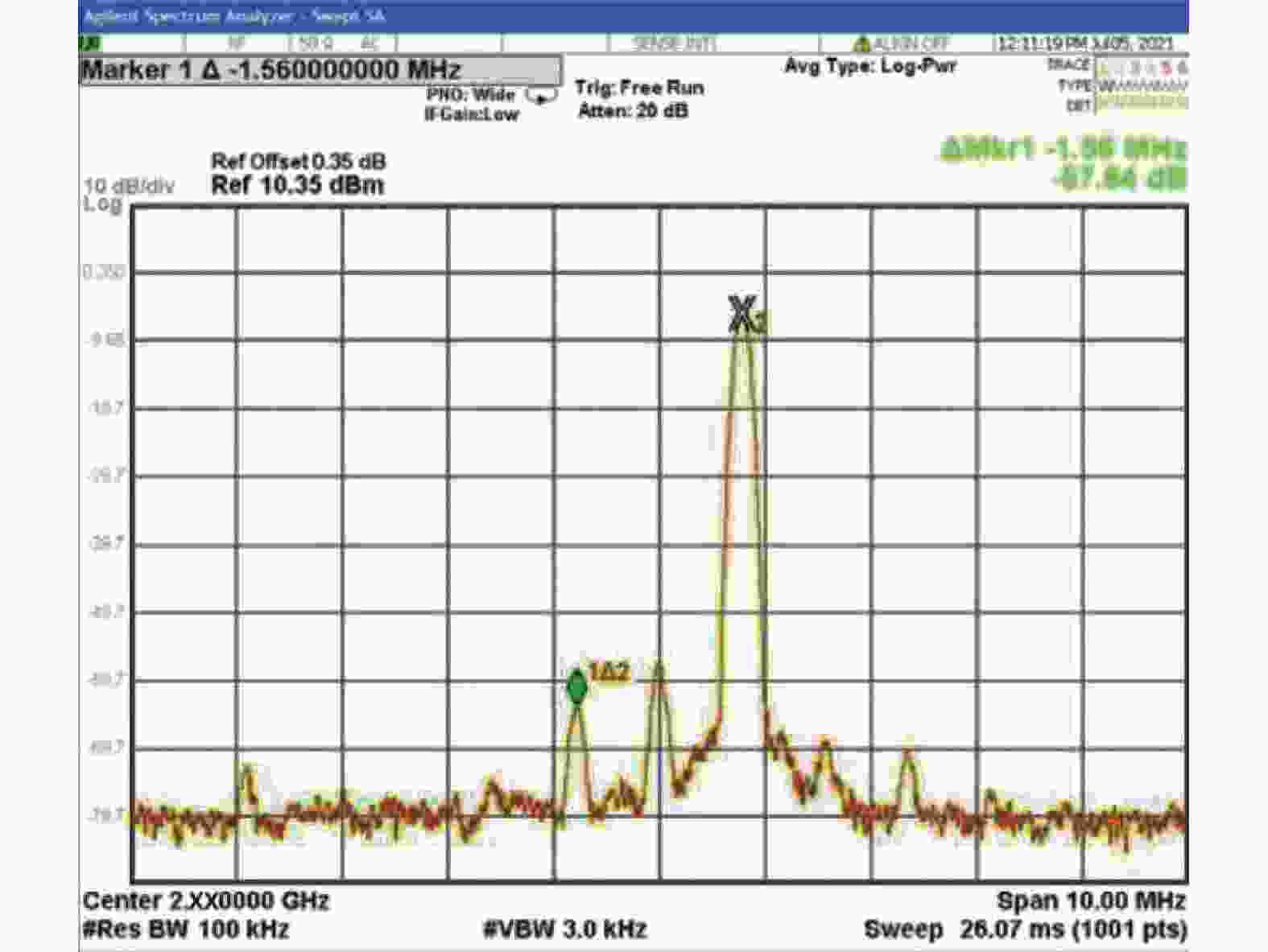

发射信号镜频抑制实测值为57.64 dB,因此满足要求指标④,如图18所示。

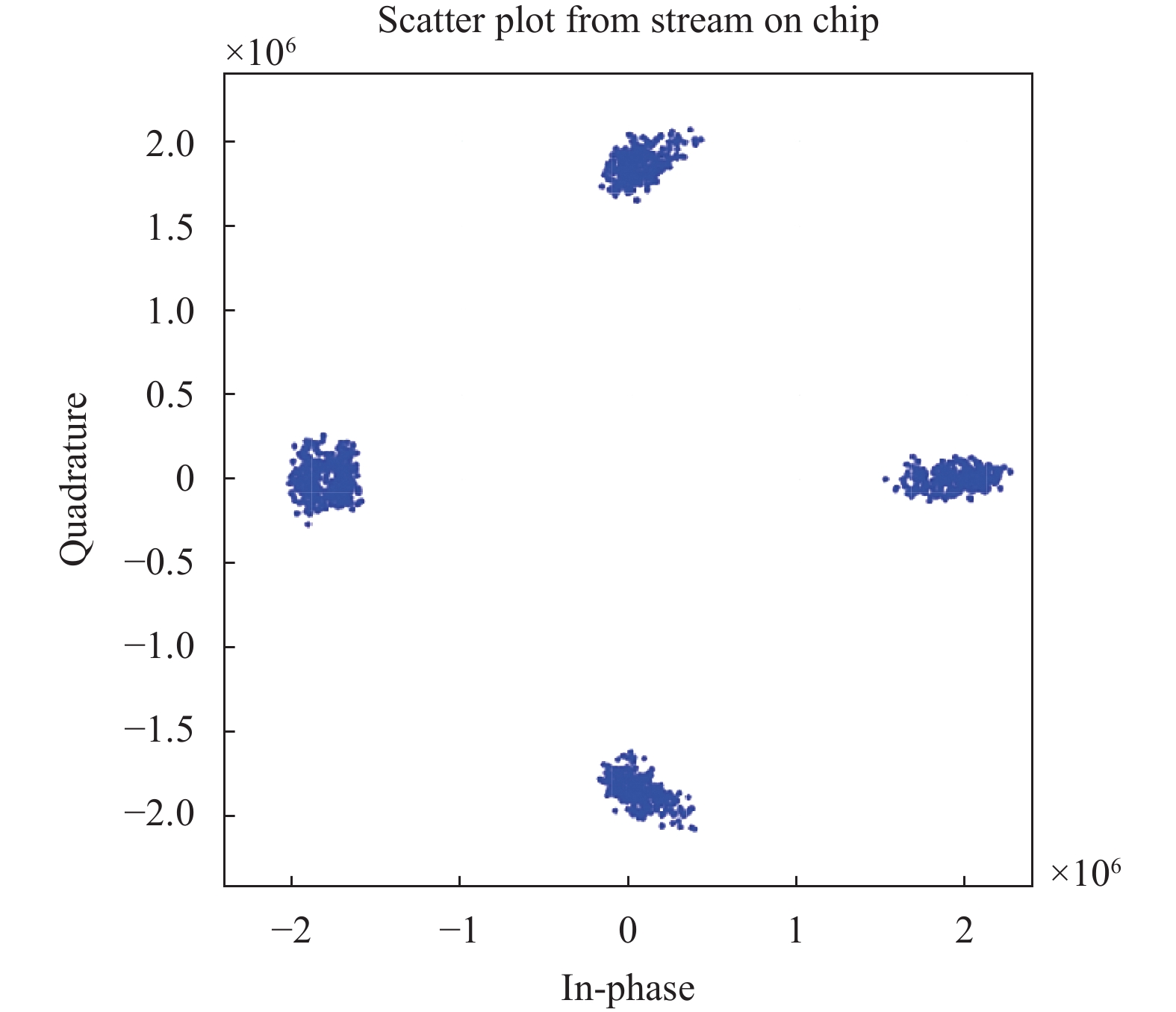

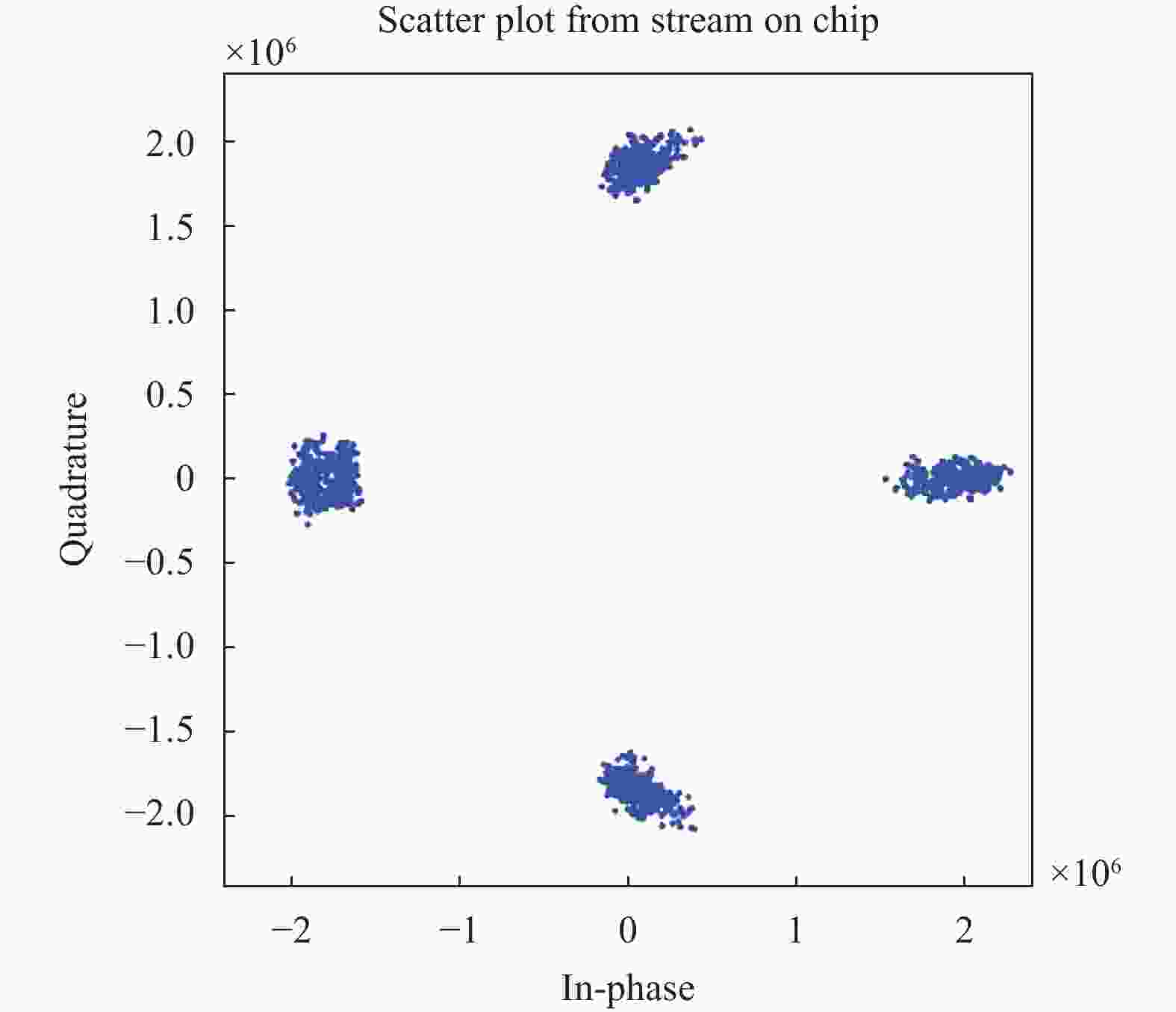

经过数据采集和频谱分析后,得到解调后的星座图。从图中可以看出,星座图落于4个坐标轴,集中收敛,说明解调器性能良好,如图19所示。

-

陶瓷封装封帽后,需要进行气密性检测。检漏包括细检漏和粗检漏。经过检漏实验,微系统满足最大漏泄率为1.013×10−3 Pa.cm3/s条件下的细检漏,满足气密性要求。

-

热管理设计是微系统设计的重中之重[12-15],本文采用了一种全新的散热方案。

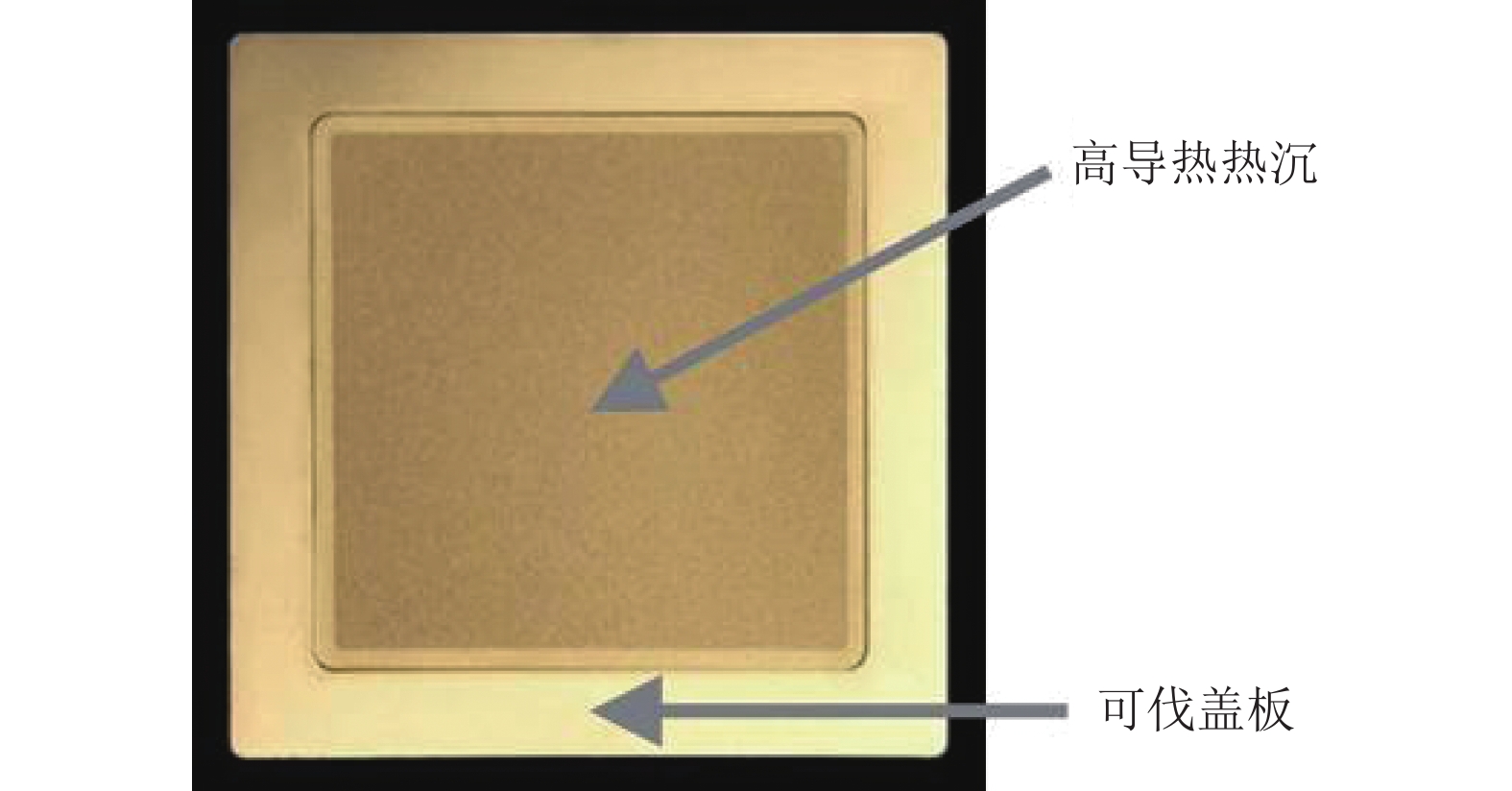

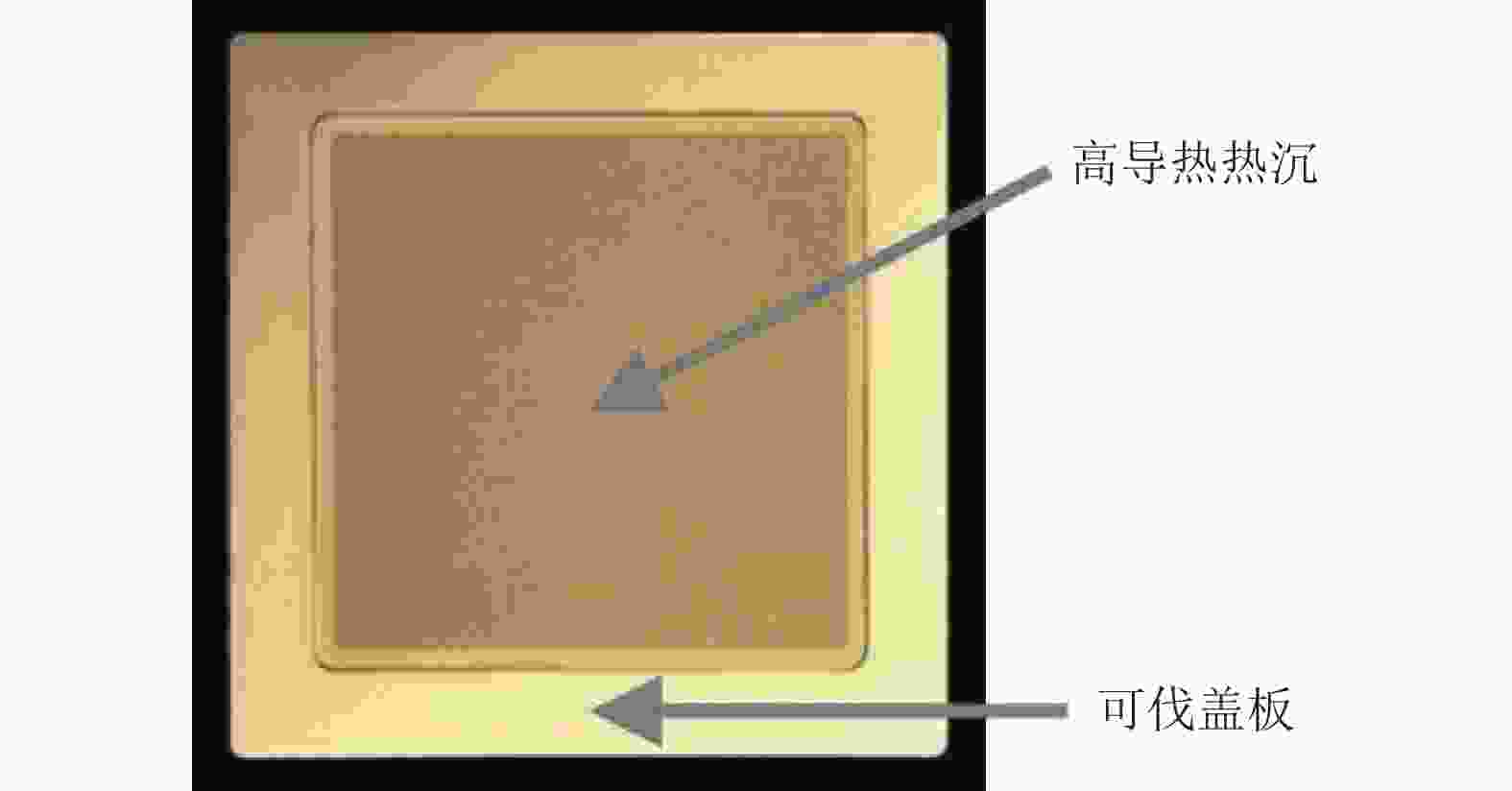

根据前期热仿真的结果,得出增加散热器可以有效降低芯片结温的结论。但是,传统的高可靠陶瓷封装都是采用平行缝焊工艺封帽,可伐盖板和内部裸芯片之间没有直接接触,缺乏有效地将裸芯片的热量传递到封装体表面的散热途径。此外,传统的盖板是单一的可伐材质,热导率很低(只有15 W/(m·K)),即使添加了散热器,散热效果也不理想。

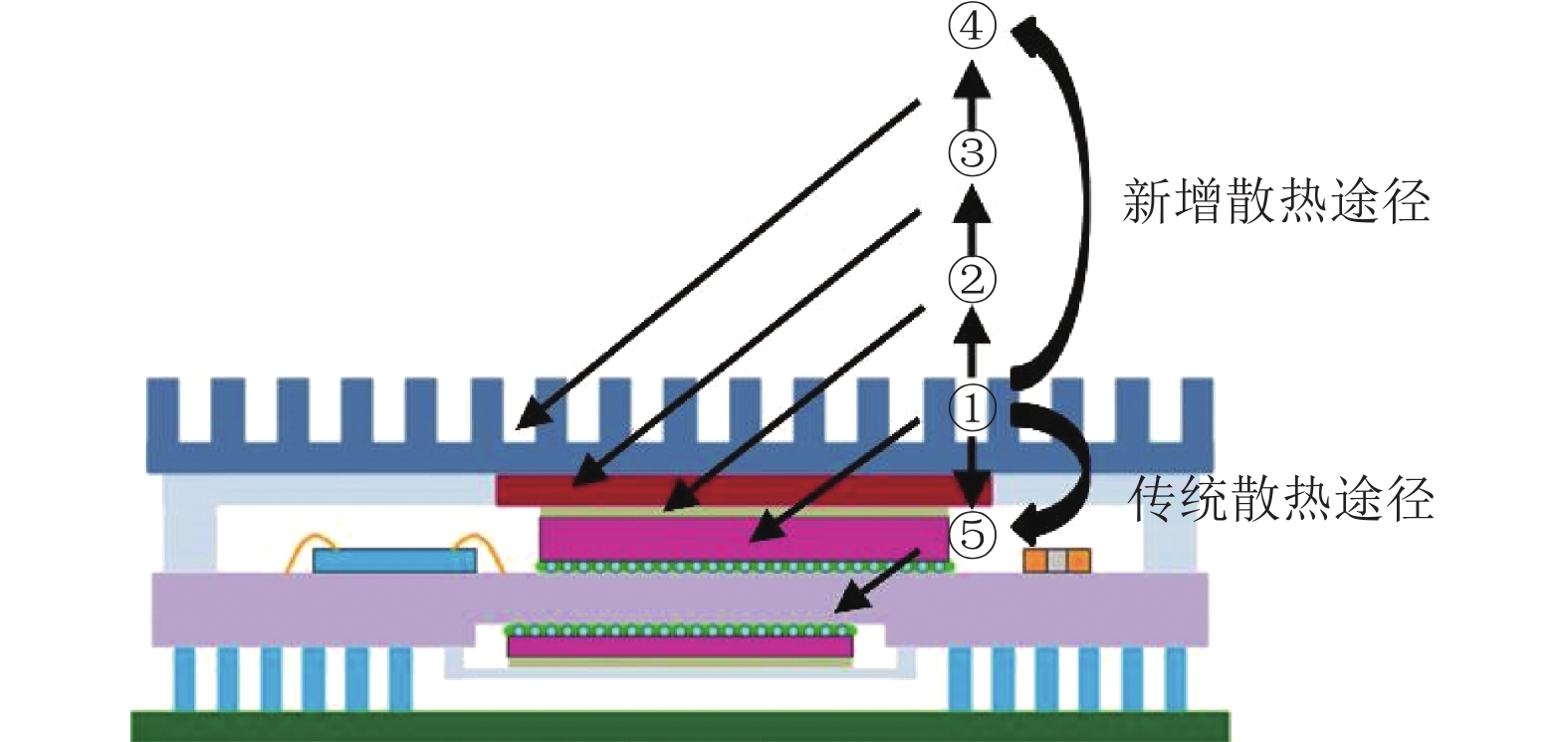

为了解决上述问题,本文定制开发了一种高导热复合热沉盖板,内嵌高导热钼铜热沉,热导率从15 W/(m·K)提升至150 W/(m·K)以上,通过技术攻关,盖板平整度/共面性可以控制在10 μm以内。根据微系统内部芯片布局和热源分布,设计内嵌热沉的形状、位置,以达到高效散热的需求,如图20所示。封帽前,在FPGA裸芯片和盖板之间填充导热硅胶;封帽后,复合热沉盖板上方,增加散热器辅助散热。

这样,针对FPGA裸芯片(FC形态)的散热,增加了一条从①FC芯片→②导热硅胶→③导热热沉→④散热器的散热途径,达到快速、高效导热+均热的效果。

此外,ALN陶瓷管壳本身具有高导热特性,支持几十瓦的功耗散热,FPGA裸片功耗较大,有源面焊接到管壳上,利用管壳本身进行散热,存在一条传统的散热途径:①FC芯片→⑤陶瓷管壳,如图21所示。

整个散热方案在满足传统陶瓷封装气密性的同时,极大地提升了整体封装散热性能。

-

本文提出了一种基于一体化陶瓷三维封装方案的射频模拟数字一体化微系统,变频部分采用直接变频架构,从方案和实现两方面详细介绍了微系统的架构、设计、工艺和验证。未来,随着芯片水平的提高和集成工艺的成熟,一体化微系统有望采用射频直采架构和硅基三维集成工艺来实现。

New Three-Dimensional Integrated RF-Analog-Digital Microsystem

doi: 10.12178/1001-0548.2022236

- Received Date: 2022-07-15

- Rev Recd Date: 2022-10-03

- Available Online: 2023-05-26

- Publish Date: 2023-05-28

-

Key words:

- integration /

- microsystem /

- RF analog digital /

- three-dimensional integration

Abstract: Recent years, microsystem has become one of the hot issues in electronic information field. This paper introduces a new three-dimensional integrated radio frequency (RF)-analog-digital microsystem. The architecture, process and verification of the microsystem are described in detail from the aspects of scheme and implementation. The traditional RF frontend is 250 mm × 120 mm size, while the microsystem is only 37 mm × 37 mm size, reducing its area by 95%. Based on the integrated ceramic three-dimensional package architecture, the microsystem integrates a variety of bare chips and passive devices to realize the electrical interconnection of internal signals. A new heat dissipation scheme is adopted to customize and develop a high thermal conductivity composite heat sink cover plate. The thermal conductivity is increased from 15 W/(m·K) to 150 W/(m·K) above. The thermal conductive silica gel is filled between the FC bare chip and the cover plate to form a new heat dissipation route and achieve efficient heat dissipation.

| Citation: | ZHANG Junzhi, YANG Jin, ZHANG Qiang, CAO Xuesong, ZHU Jian. New Three-Dimensional Integrated RF-Analog-Digital Microsystem[J]. Journal of University of Electronic Science and Technology of China, 2023, 52(3): 372-378. doi: 10.12178/1001-0548.2022236 |

ISSN

ISSN

DownLoad:

DownLoad: