-

低速至中速采样率、高分辨率(14位以上)模数转换器(Analog-to-Digital Converter, ADC)在电力测量与保护、电机控制、自动测试设备、多路数据采集系统等场景中有广泛应用。逐次逼近寄存器型(Successive Approximation Register, SAR)ADC转换延迟小、功耗低,非常适合上述应用。然而,采样保持电路、数模转换器(Digital-to-Analog Converter, DAC)和比较器等关键电路的性能是制约SAR ADC获得高动态范围、高线性度以及低功耗的瓶颈,相关的电路设计得到持续关注和广泛研究[1-6]。

文献[1]设计了一种混合结构的电容型数模转换器(Capacitor Digital-to-Analog converter, CDAC),通过灵活编程方式补偿增益误差以及电容失配误差。文献[2]针对电容失配影响ADC线性度的问题提出了二进制窗口DAC切换以及电容随机交换方案,在无需校准时获得100 dB的SFDR,但该方法需要增加额外的译码电路和复杂的DAC控制逻辑。针对CDAC切换能耗的问题,文献[3]采用了混合电容切换方法设计了一款10位SAR ADC,文献[4]基于GND采样的单调电容切换方法设计了一款12位ADC,有效降低了功耗。针对比较器噪声,文献[5]采用基于压控振荡器的比较器自适应地根据输入电压大小调整积分时间,在功耗和噪声性能之间进行折中。文献[6]在逐次逼近过程的前若干周期使用低功耗但噪声大的比较器,剩余若干周期使用高功耗但噪声小的比较器,并增加一位冗余电容消除大噪声比较器进行转换引入的误差,减少了由比较器产生的总功耗。

本文设计了一款16位SAR ADC,针对线性度、功耗以及噪声方面的设计挑战,提出了改进的采样保持电路结构,优化采样线性度和噪声性能。采用分段电容阵列及分段式基准源驱动方案改善CDAC输出稳定速度,并采用混合电容切换方案降低能耗。比较器采用了两级预放大加锁存器的结构以及输出失调存储,显著降低了噪声和失调电压。ADC采用异步时序控制,在0.18 μm工艺上进行了流片验证,测试结果表明,采用上述改进的技术有效提升了ADC的线性度,并获得了良好的功耗和噪声性能。

-

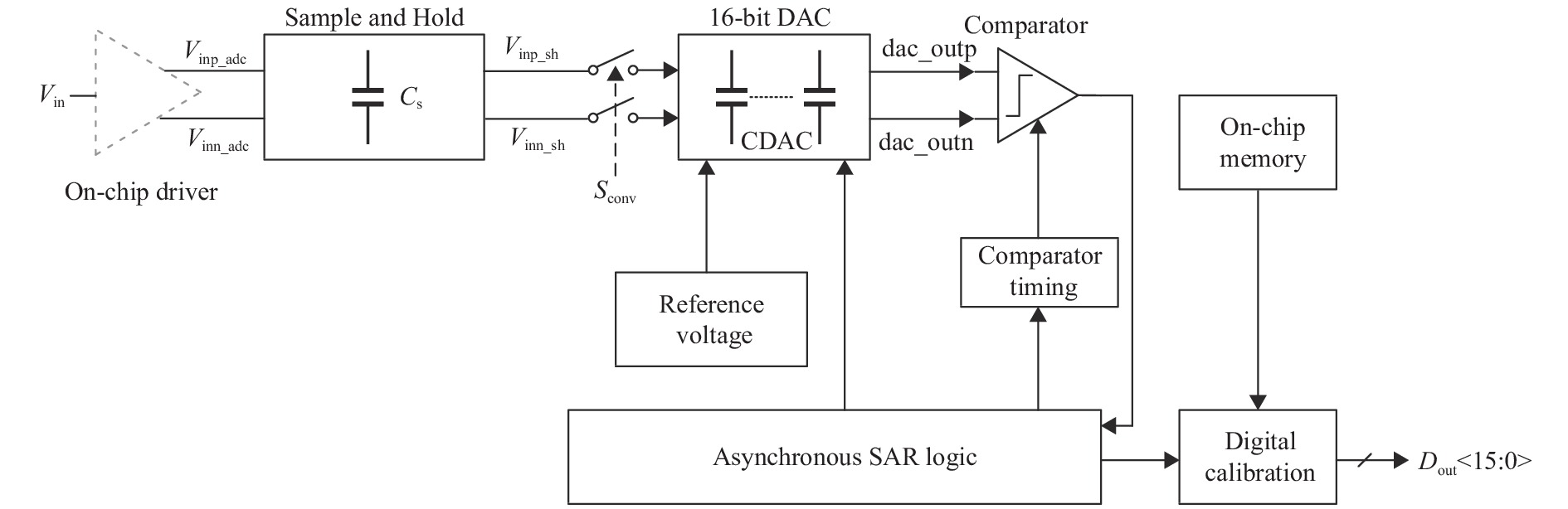

图1为本文提出的SAR ADC架构框图,整体为差分结构,包括采样保持电路、CDAC、比较器、基准电压、异步逐次逼近逻辑、比较器时序控制以及数字校准等部分。片上驱动器用于将单端输入信号转换为差分输出并驱动采样电容CS。异步逻辑省去不必要的转换等待时间,提升了转换速度。片上数字校准完成CDAC的电容实际权重计算、失调和增益校准以及非线性校准,其中校准所需的参数通过在校准模式下将测试数据在片外进行计算后得到,然后再写入片上存储器中。

将采样保持电容CS和CDAC分开设计有两个考虑:1)本ADC的目标应用为多通道数据采集系统,ADC前端有多个采样保持器分别将多路输入信号采样并保持在各通道对应的CS上,在转换阶段由Sconv信号分时复用CDAC依次进行模数转换,其好处是可保证各通道转换性能的一致性并减少功耗;2)SAR ADC的比较器采用1.8 V低压管设计以提升速度和噪声性能,为了满足比较器输入电压处于器件安全耐压范围内,CS和CDAC在转换期间通过电荷分享,对采样到的信号幅度进行衰减,使CDAC输出的共模电平满足比较器输入要求。

-

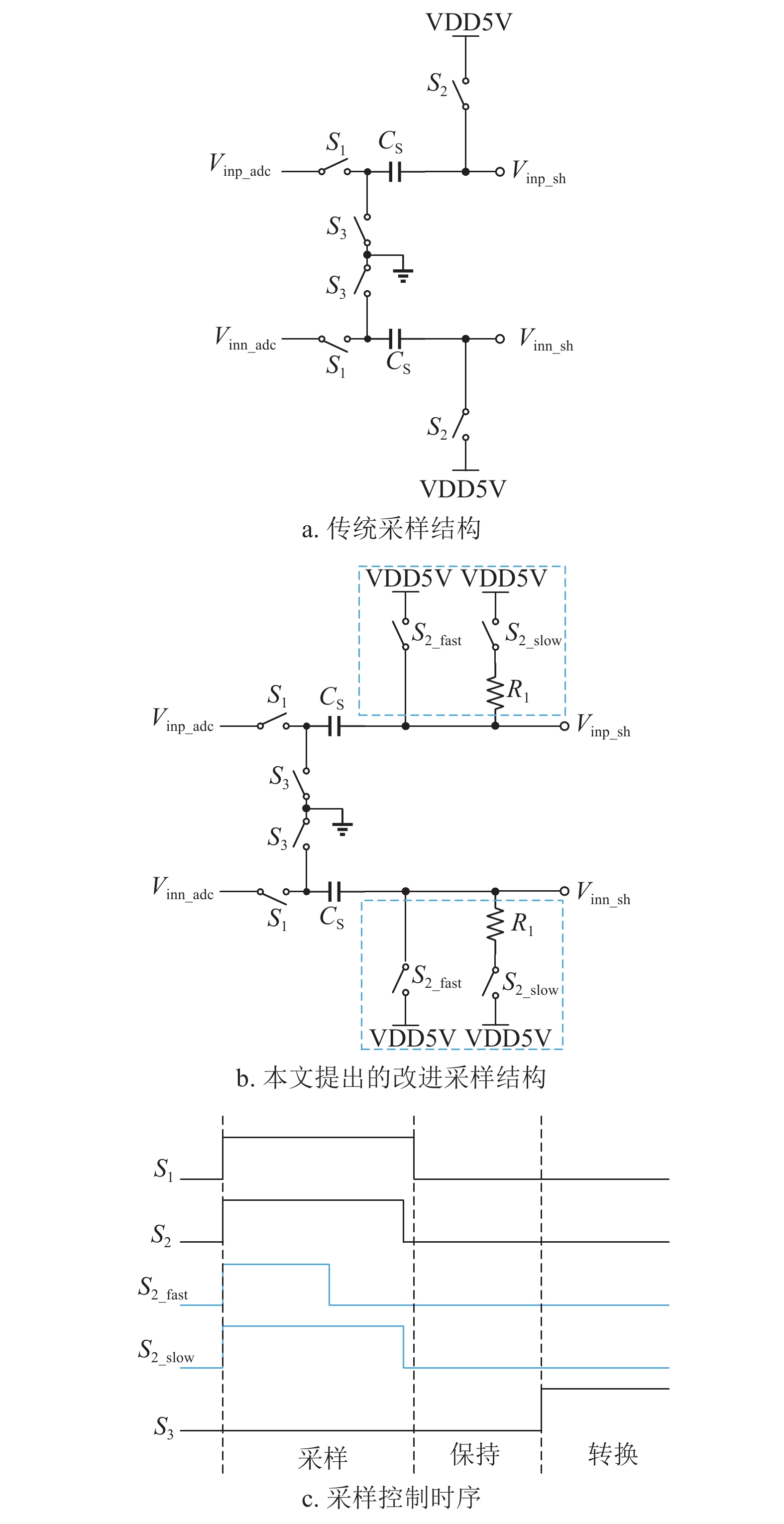

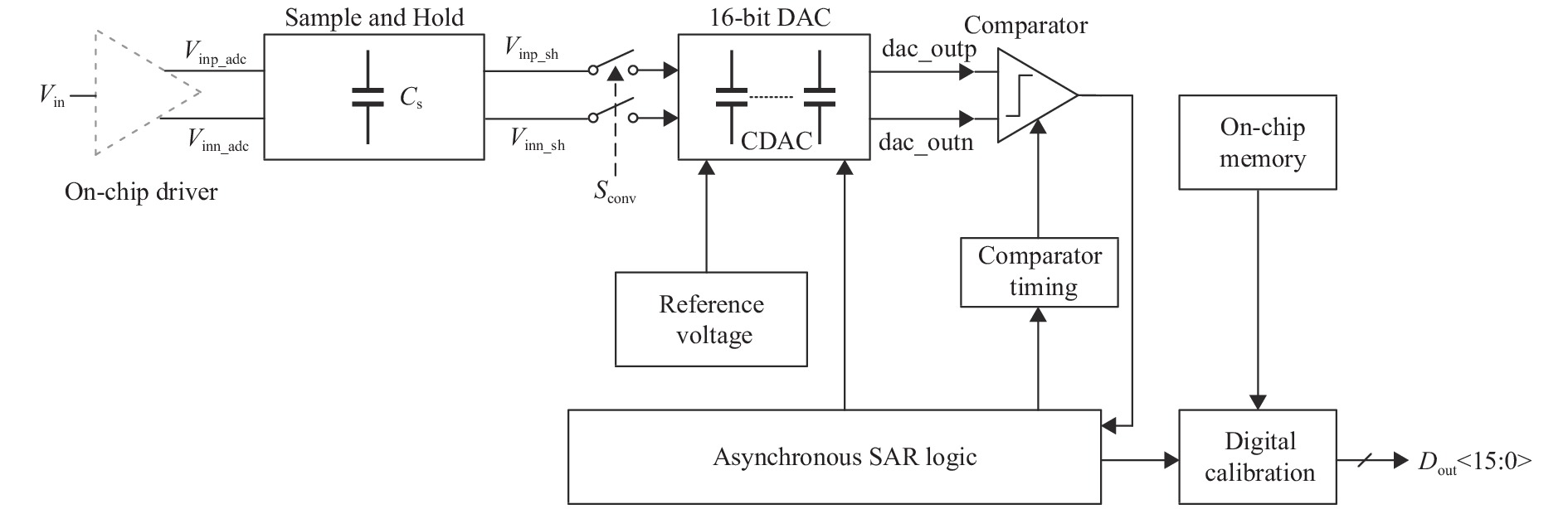

高精度ADC常使用下极板采样以降低金属氧化物半导体(MOS)开关管电荷注入产生的非线性。图2a为传统的下极板采样电路,开关S1和S2闭合时,差分输入信号Vinp_adc和Vinn_adc分别接入采样电容CS的下极板,上极板连接至电源VDD5V。采样结束后,S2和S1依次断开,当S3闭合时ADC开始转换。根据理论分析的近似,S2断开时,在电容CS上极板注入的电荷量为:

式中,

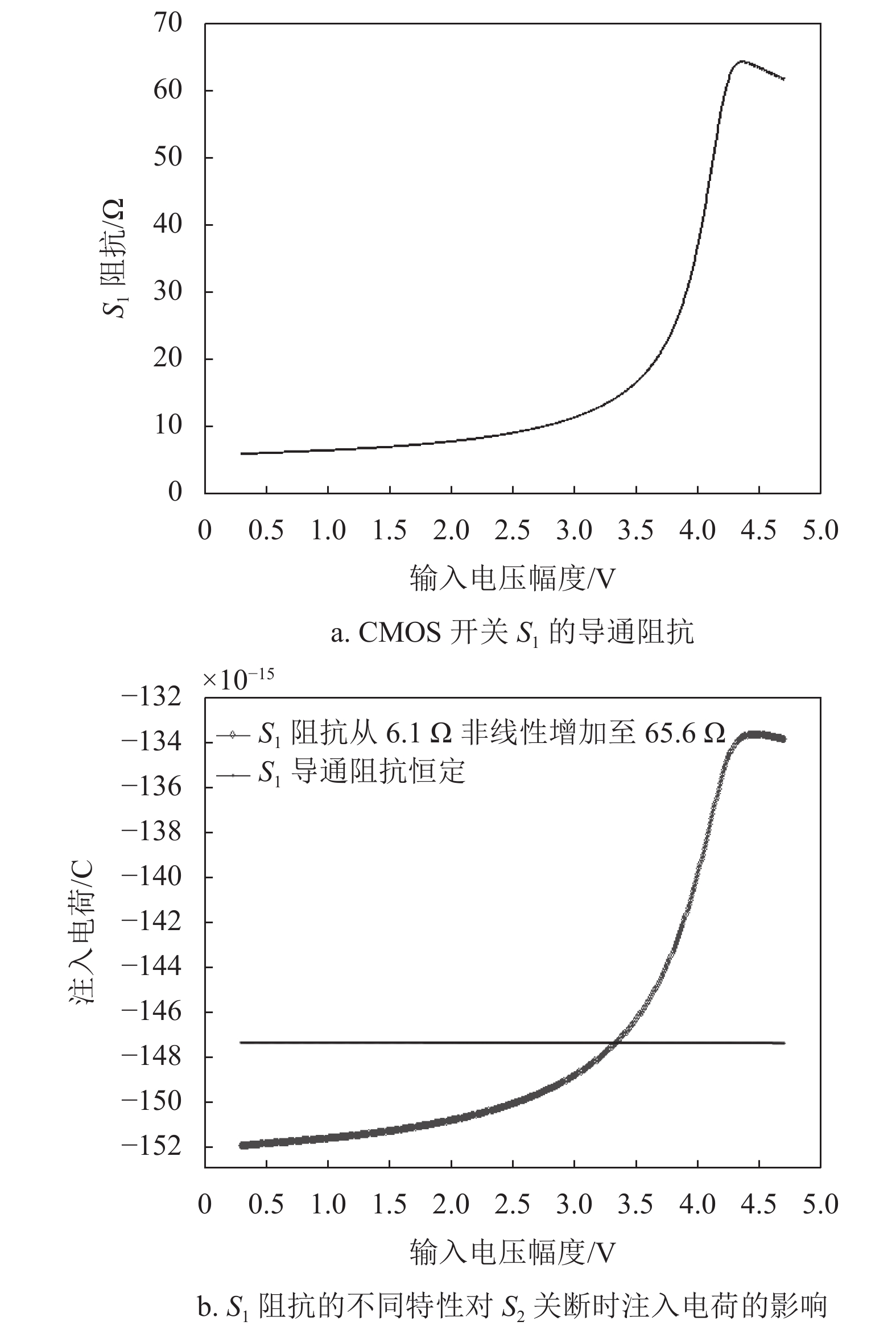

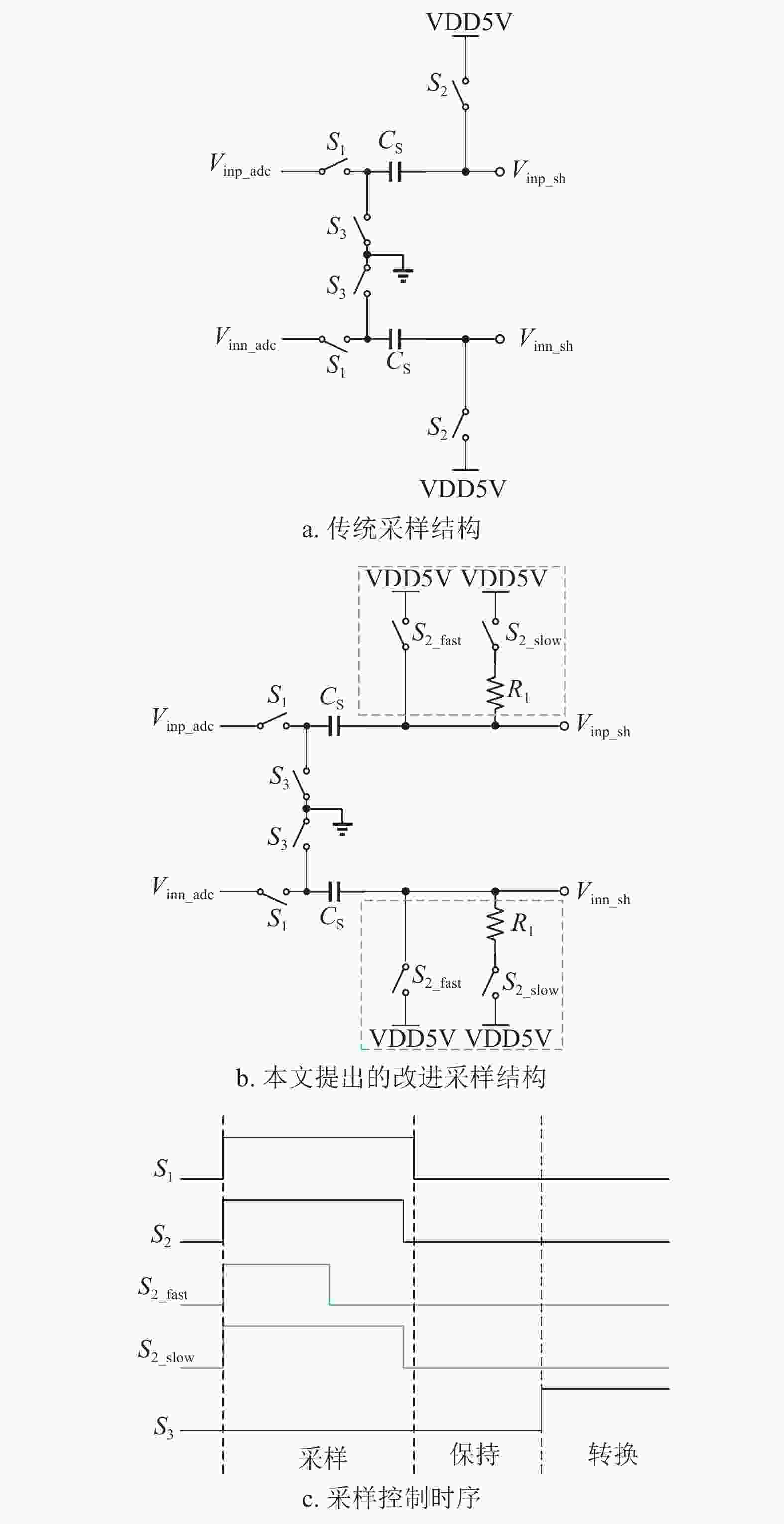

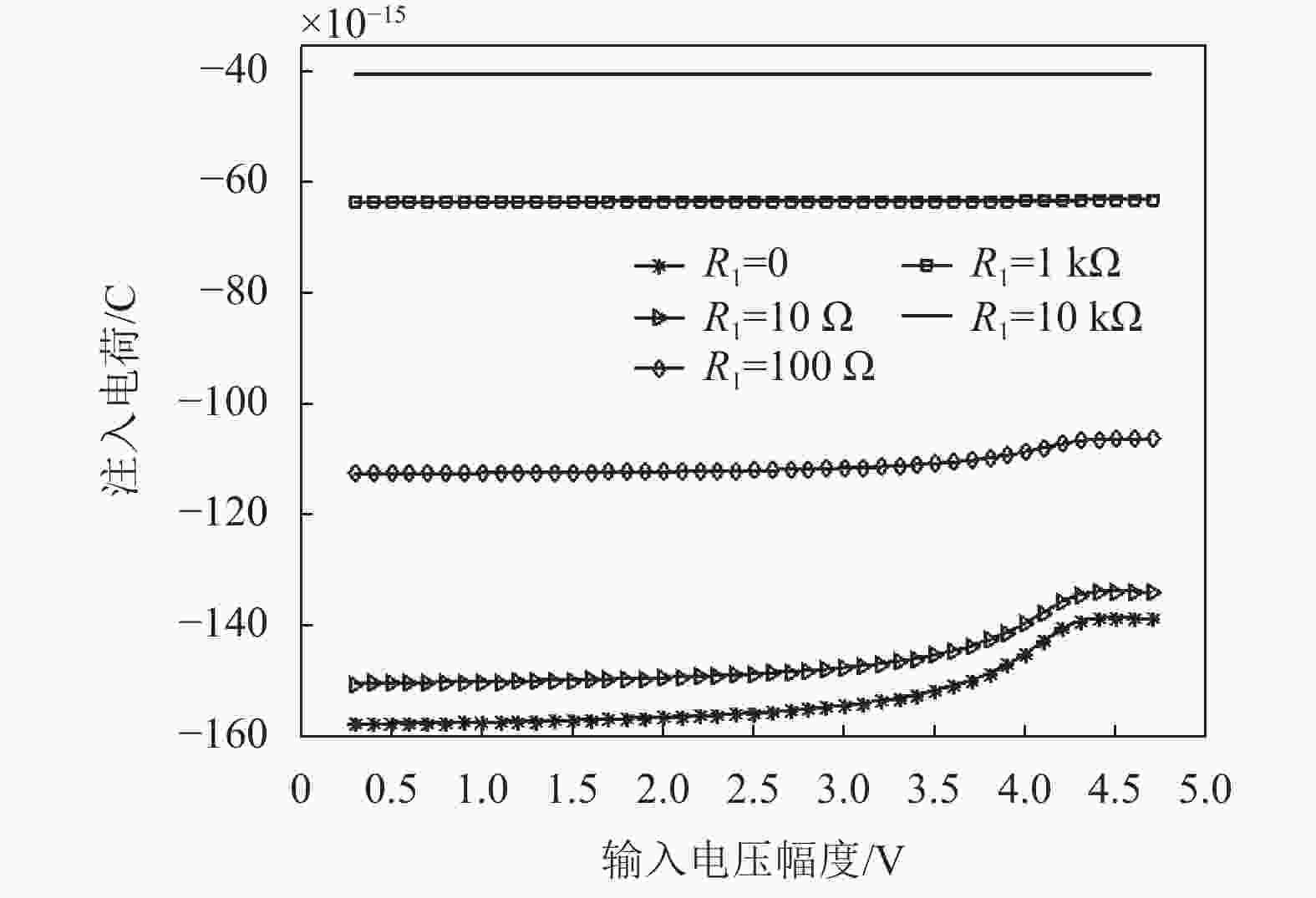

$ \alpha $ 为工艺相关的系数;WL为MOS开关栅极面积(W和L分别为沟道宽度和长度);Cox为单位面积的栅极电容;$ {\phi}_{{H}} $ 为控制S2的栅源电压;Vt为开关的阈值电压。根据式(1),S2关断时注入电荷量与输入信号无关,因此不产生非线性,其在上极板引入的失调也可通过差分结构消除。对于较低精度ADC的采样需求而言上述近似是合理的。然而,实际电路中控制开关关断的信号速度总是有限的,S2关断时其沟道内的电荷会根据晶体管源漏两端的阻抗差异重新分配。当S1采用互补金属氧化物半导体(CMOS)开关实现时,其导通阻抗与输入信号幅度呈现非线性相关,因此S2关断时在CS注入的电荷也和输入信号相关,表现出非线性,对高精度ADC的影响不可忽略。图3显示了S1的导通阻抗和S2断开时在CS注入的电荷随输入信号幅度变化的仿真结果。当输入信号幅度从0.3 V增加到4.7 V时,S1的阻抗从6.1 Ω非线性增加至65.6 Ω,注入的电荷从−152×10−15 C非线性增加至−134×10−15 C,其趋势和S1阻抗的非线性一致。而当S1的导通阻抗恒定时,注入电荷的变化量小于0.05×10−15 C,非线性可忽略。

采用自举开关可以提升采样线性度,但是自举电路增加了电路设计复杂度。本文基于非自举采样方式,在传统下极板采样电路基础上,提出了如图2b所示的改进电路结构。将上极板开关S2分为S2_fast和S2_slow两路,S2_fast用于加速采样电容上极板电压的建立。在S2_slow和CS上极板之间引入电阻R1,其目的是当开关S2_slow断开时向CS上极板看到的阻抗更加趋于线性,从而降低S2_slow电荷注入的非线性。采样控制时序如图2c所示,其中S2_slow的控制时序与传统方案中的S2时序相同,S2_fast先于S2_slow断开,S2_fast注入的非线性电荷可由S2_slow通路消除。图4为不同R1阻值条件下,S2_slow的注入电荷随输入幅度变化的仿真结果。可以看到,R1减小了电荷注入的非线性,且R1阻值越大,非线性越小。当R1大于1 kΩ时,注入电荷变化量小于0.4×10−15 C。此外,R1还与CS构成了一阶低通滤波器,可滤除片上信号驱动器和采样开关的带外噪声,提升ADC的信噪比(SNR)。实际设计中,R1的取值需在CS上极板稳定速度(影响采样精度)、电荷注入量以及噪声滤波性能之间折中考虑。此外,为了减小电阻失配影响差分两端采样精度,电阻版图面积取值相对较大,且进行了交叉匹配设计。仿真结果表明,采用改进后的采样电路,ADC的SNR从90.3 dB提升至94.7 dB,SFDR从93.5 dB提升至111.6 dB。

-

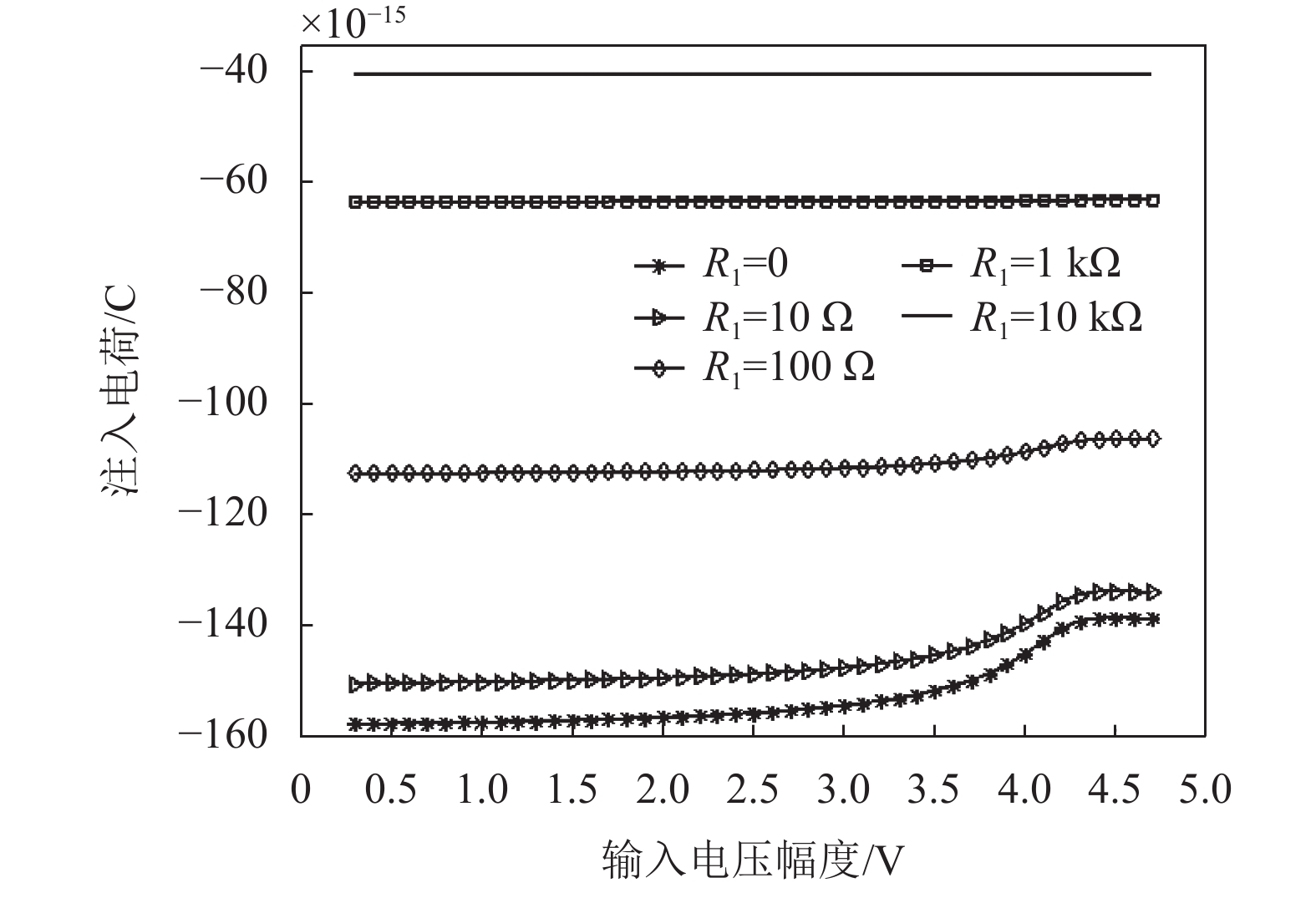

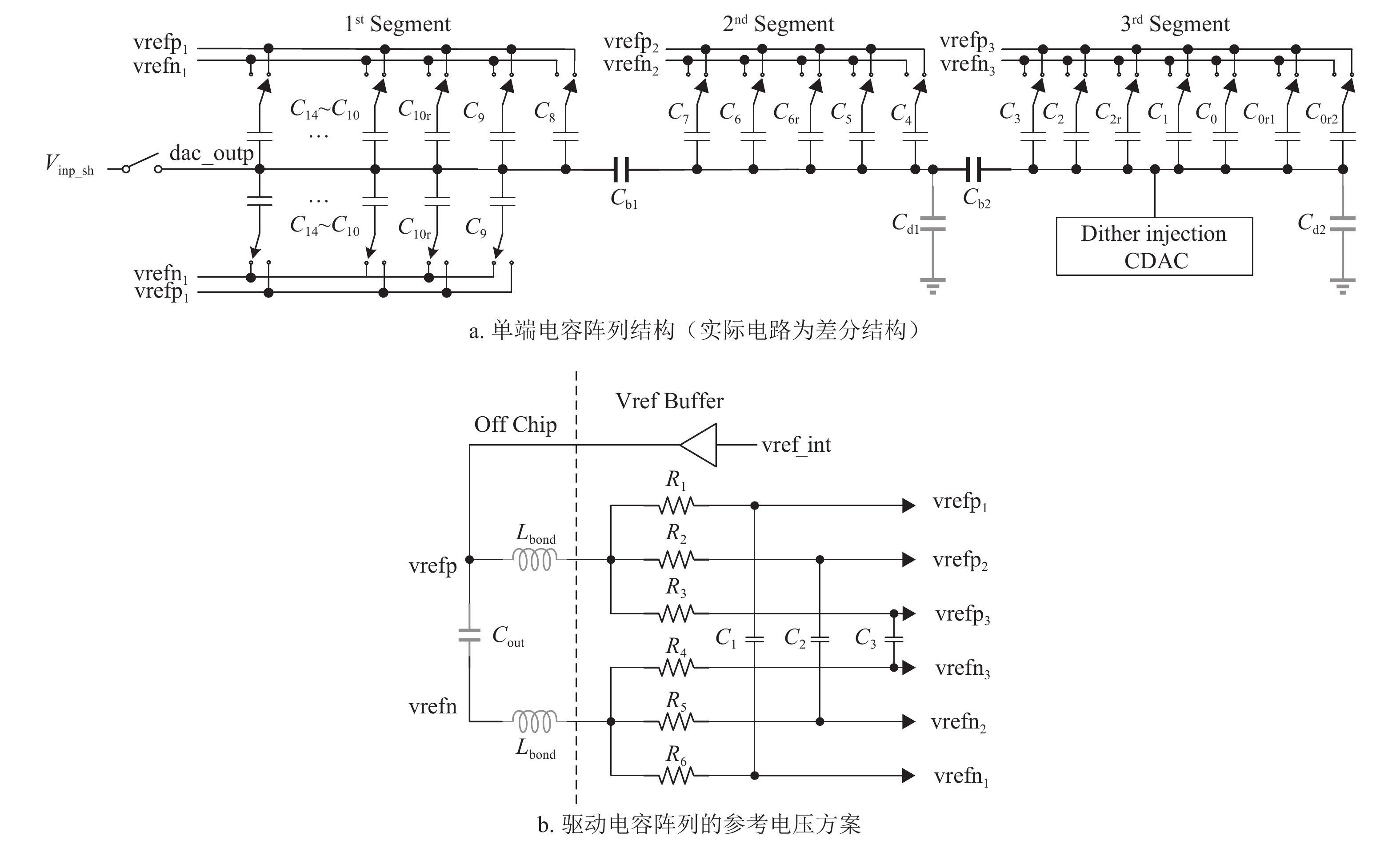

传统二进制电容阵列的结构所需单位电容的数目随ADC分辨率增加而指数增长,耗费巨大的面积,且增加基准电压源的驱动功耗和版图匹配难度,不适用于高精度ADC设计。采用分段式CDAC设计可有效降低电容面积及芯片功耗[5, 7]。本文提出的CDAC采用图5a所示的三段式结构(图中所示电容下极板的连接方式为采样状态),其中C14~C0为二进制权重常规电容,C10r、C6r、C2r、C0r1和C0r2为二进制权重冗余电容,用于纠正转换过程中DAC输出电压建立误差、电容权重误差等导致的转换错误,保证转换结束时DAC输出电压收敛至0.5 LSB以内。

$C_{{\rm{b}}_1} $ 和$C_{{\rm{b}}_2} $ 为桥接电容,$C_{{\rm{d}}_1} $ 和$C_{{\rm{d}}_2} $ 为辅助电容,下极板接地,在转换过程中不进行切换。$C_{{\rm{d}}_1} $ 和$C_{{\rm{d}}_2} $ 的值经过合理设计后可保证桥接电容取值为单位电容的整数倍,有利于在版图上实现桥接电容和其他电容之间较好的匹配。$C_{{\rm{d}}_1} $ 和$C_{{\rm{d}}_2} $ 的取值依据是要保证参与切换的二进制电容在DAC输出端的等效权重符合理论值。以两段式电容结构为例,假设Cu为单位电容,Cb为桥接电容,CLT为低位分段电容总和,Cd为辅助电容,CMT为高位分段电容总和,CMLSB为高位分段电容中参与切换的最低权重电容,CMLSB=kCu(k为整数),CLMSB为低位分段电容中参与切换的最高权重电容,CLMSB=(L−1)Cu(L为整数)。从CDAC输出端看,CMLSB切换产生的输出电压变化量dVO1应为CLMSB切换产生的输出电压变化量dVO2的两倍,据此,可以推导出式(2),在已知Cb、L和k时,可以求得CLT,减去低位分段电容中参与切换的二进制权重电容即为Cd的值。扰动注入(Dither Injection)CDAC为总权重为3.5 LSB的电容阵列,其作用是采样阶段通过在该DAC下极板注入3位随机扰动信号,实现在输入信号上叠加一个小幅度随机扰动信号,改善因电容失配导致的ADC微分非线性(DNL)性能下降。由于注入扰动信号的电容权重非常小,其对输入信号的动态范围影响可以忽略。

三段电容阵列采用同一幅度的基准电压源进行驱动,以减少基准电压数量。图5b为产生驱动CDAC的基准电压方案。vref_int为芯片内部产生的低噪声基准电压,经过片上缓冲器驱动片外电容Cout,Cout两端的电压差vrefp-vrefn作为驱动内部CDAC的基准电压源。与CDAC结构相对应,本设计在内部产生3组基准电压(vrefp1|vrefn1、vrefp2|vrefn2和vrefp3|vrefn3)分别驱动3段CDAC的电容下极板。考虑到封装引线寄生电感的影响,分别使用去耦电容C1~C3增加内部基准源的瞬时驱动能力,加速CDAC切换时基准源的稳定速度,减少基准电压波动带来的CDAC建立误差。电阻R1~R6用于消除电感和电容产生的谐振。由于第二段和第三段CDAC中高权重位电容的容值较大,采用本设计的基准电压驱动方案有利于加快这些电容下极板切换时CDAC输出电压的稳定速度。

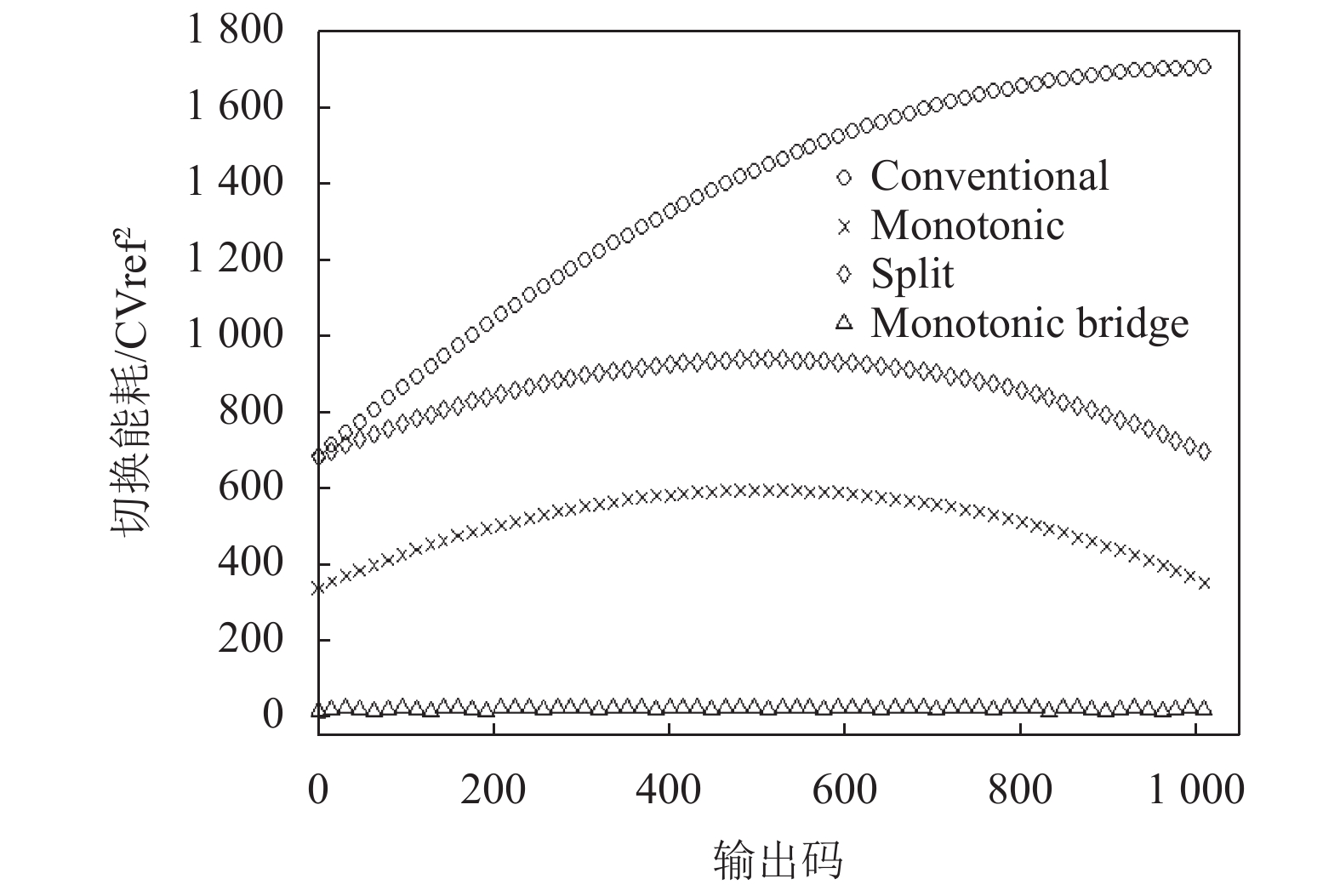

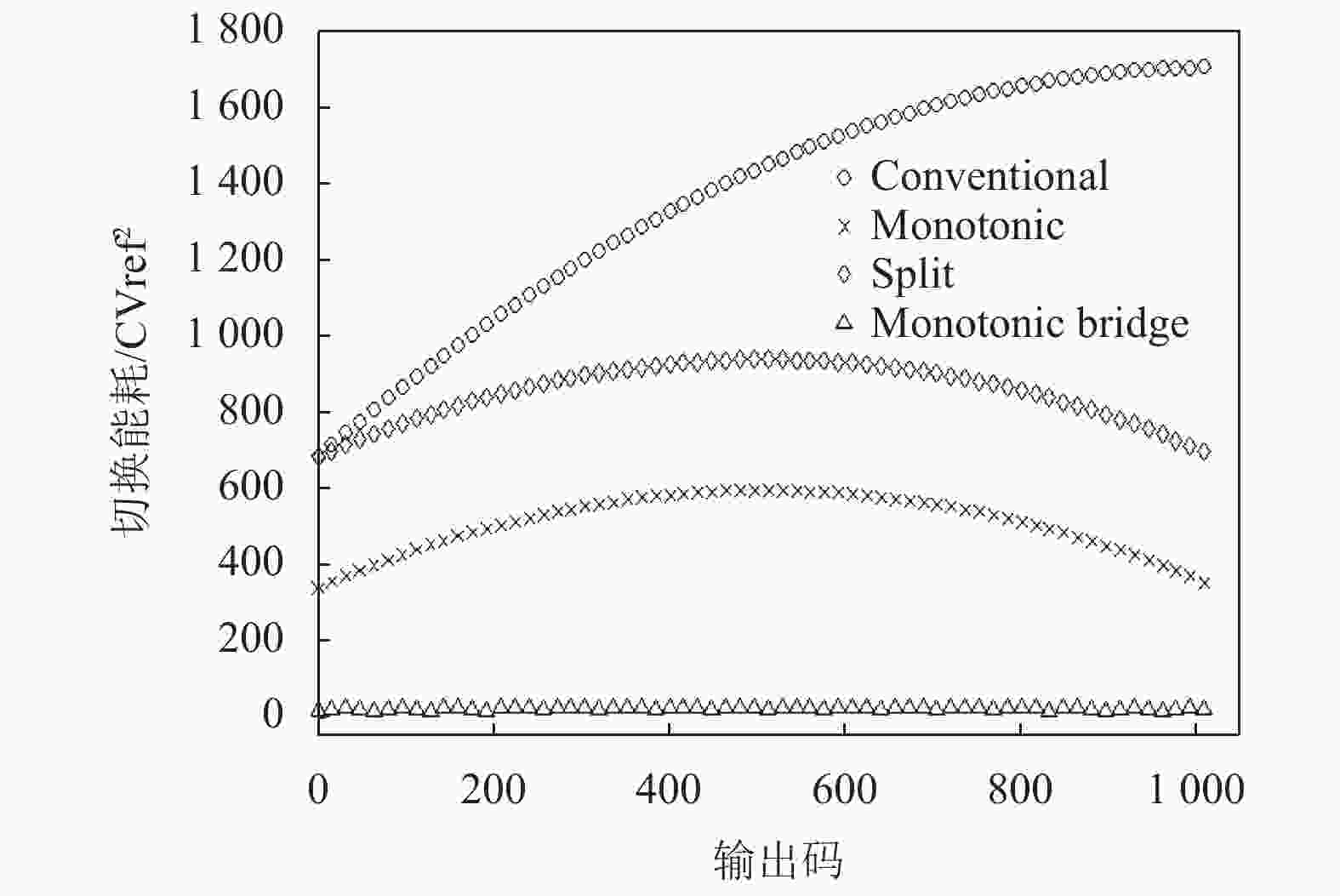

电容阵列切换时的能量消耗影响ADC功耗和驱动CDAC的基准电压源的稳定度。文献[8]提出的单调开关切换方式相对于传统切换方式可减小81%的能量消耗,但是在转换过程中DAC输出共模电平不断减小,对于本设计采用1.8 V低压管的比较器(见2.3节),共模电平降低会压缩第一级预放大器中差分输入对管的电压裕度,导致输入失调电压随共模电平发生变化,降低失调校准的精度和ADC性能。采用分裂式结构设计的CDAC(如图5a中C14~C9,一半电容下极板接vrefp1,另一半电容下极板接vrefn1)在电容切换过程中可保证输出共模电压保持稳定,与基于共模电平的开关切换方式类似[9-10],且相对传统方式也降低了开关切换能耗。图6以10位ADC为例,显示了非分段电容在传统切换方式、分裂式切换、单调切换以及分段电容结构结合单调切换方式所消耗的能量仿真结果对比(基于相同的单位电容),可以看到分裂式切换、单调切换相比传统切换方式均可以大幅缩减切换能耗,而分段电容结合单调切换方式可以获得最低的能耗,相比传统CDAC切换方式的总能耗减小了98.3%。

综合考虑电容面积、CDAC输出共模电平稳定性以及开关能耗等因素,本文提出的分段CDAC结构及混合电容切换方式(C14~C9电容采用分裂式切换,其余电容采用单调切换)既兼顾了比较器输入共模电压的稳定性,又大幅减小了CDAC切换功耗,降低了对基准电压源驱动力的要求。其中,电容采用寄生效应较小的金属−绝缘层−金属(MIM)电容设计,同时在分裂电容上还采用了背靠背的物理连接方式,消除了电容的一阶电压效应影响。

-

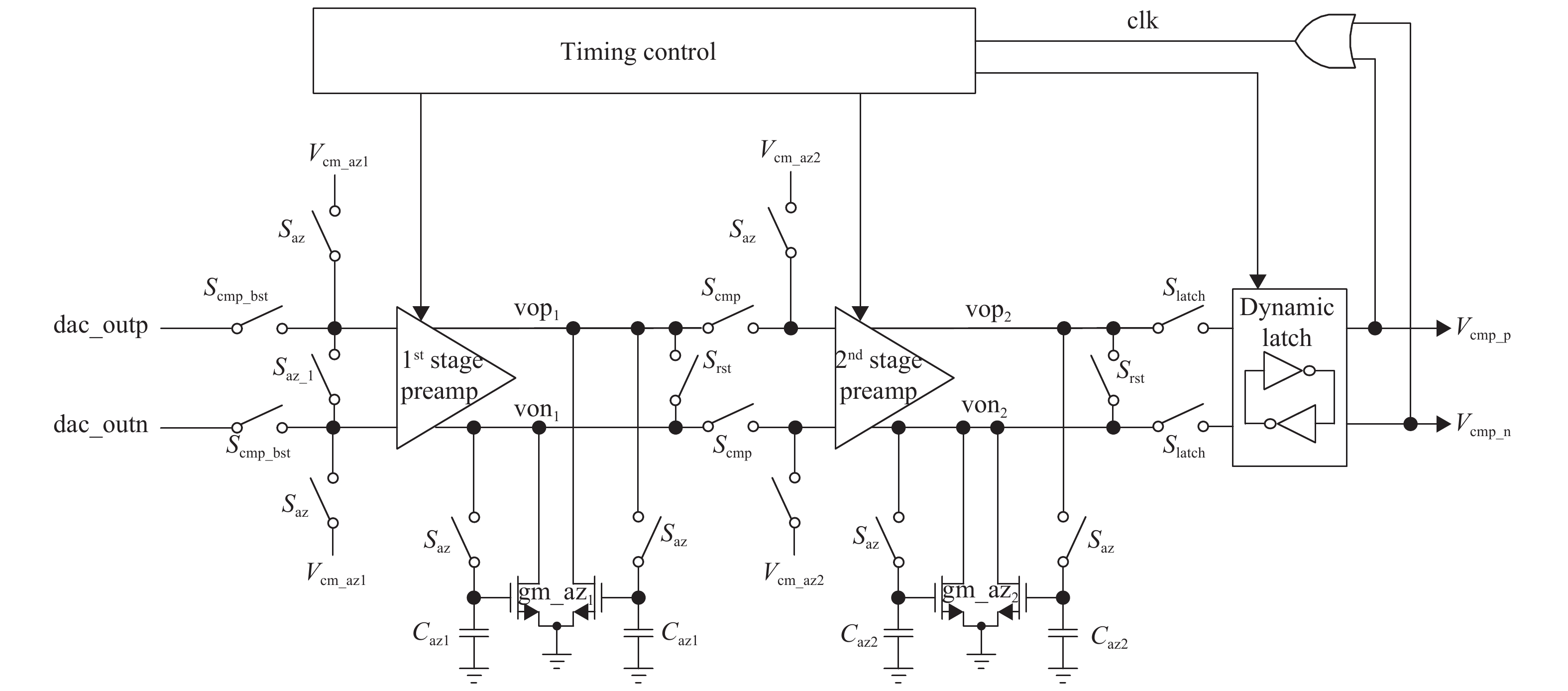

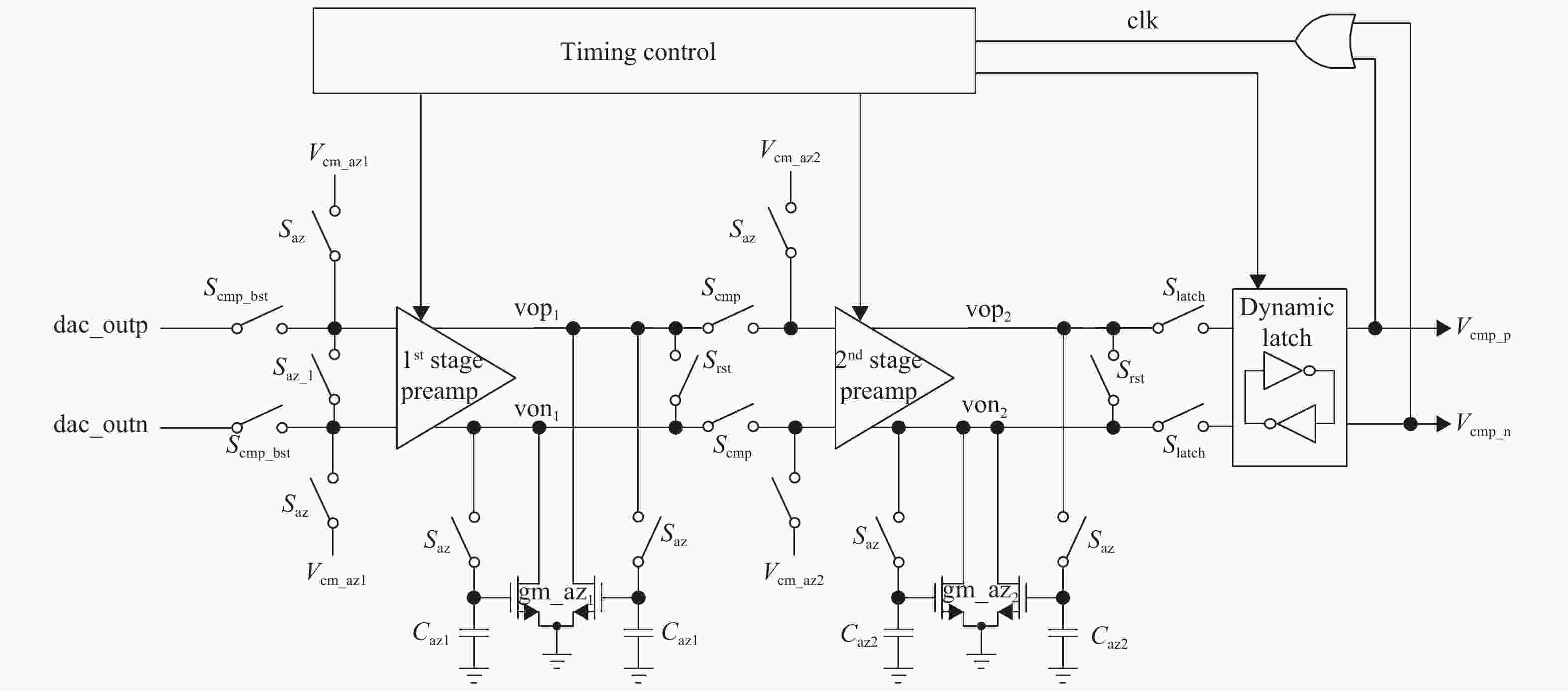

图7是本设计中的比较器结构框图,包含两级预放大器、动态锁存器和时序控制模块。得益于前述采样保持结构设计,比较器输入共模电平较低,两级预放大器均采用了文献[7]第二级的结构,简化了第一级设计复杂度,减少了噪声贡献源,有助于实现更低的等效输入噪声。

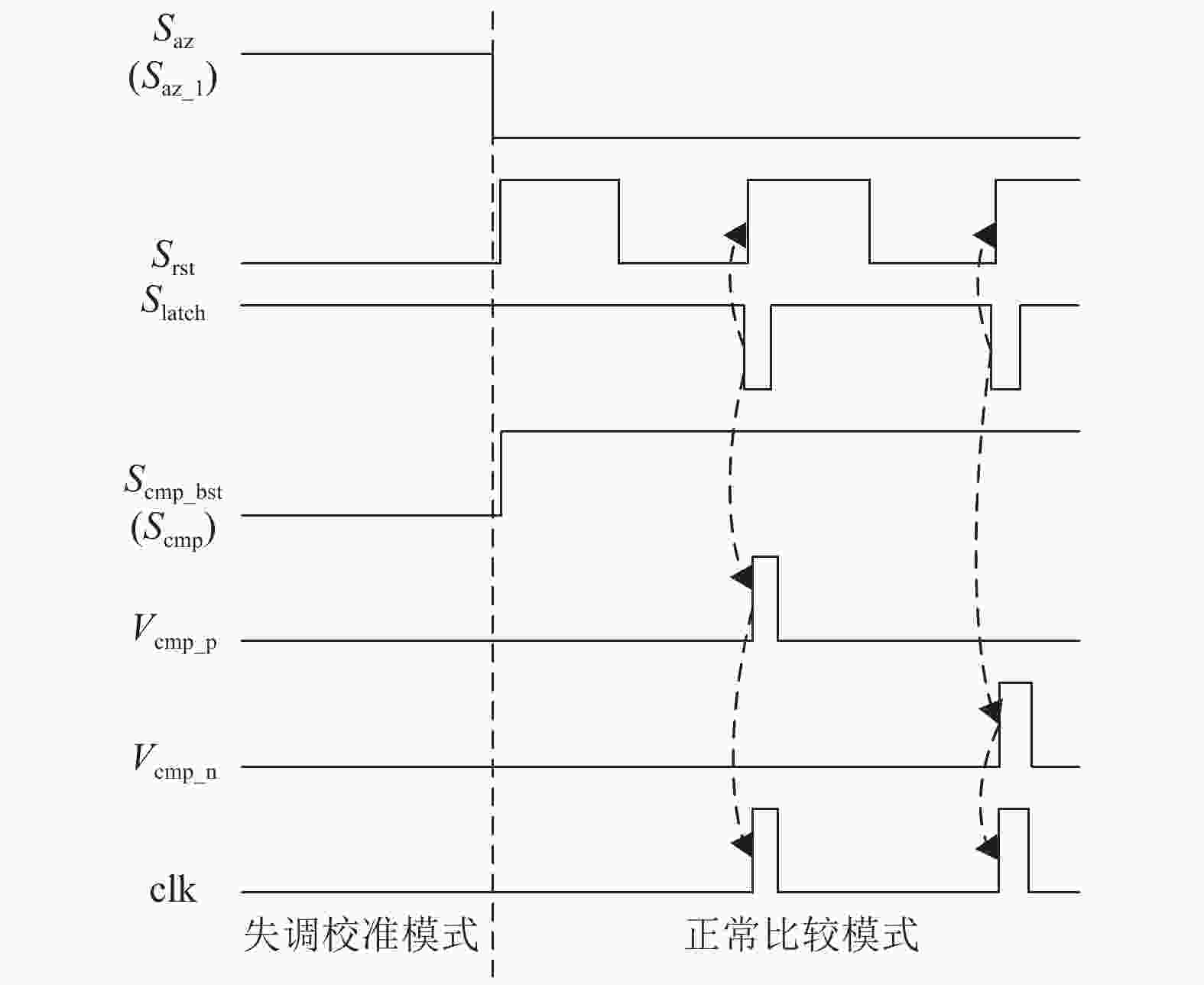

比较器可工作在失调校准模式和正常比较模式,由图8所示的工作时序决定。当开关Saz、Saz_1闭合,其余开关断开时,两级预放大器均工作在失调校准模式,放大器的差分输入端分别连接至共模电压

$V_{{\rm{cm}}\_{\rm{az}}_1} $ 和$V_{{\rm{cm}}\_{\rm{az}}_2} $ ,此时放大器处于闭环工作状态。当Saz、Saz_1断开时,输出失调电压以及1/f噪声分别存储于电容$C_{{\rm{az}}_1} $ 和$C_{{\rm{az}}_2} $ 上。以第一级为例,存储于$C_{{\rm{az}}_1} $ 上的失调电压为:式中,

$ {{V}}_{\mathrm{o}\mathrm{f}\mathrm{f}1\_\mathrm{i}} $ 和gm1分别为输入对管失调电压和跨导;gm_az1为失调消除对管跨导。当比较器切换到正常比较模式时,放大器处于开环放大状态,输入等效失调电压为:式中,Rout为放大器在开环状态下的输出阻抗。从式(4)可以看到,比较器的输入失调被抵消。

预放大级在失调校准结束时刻将失调电压存储在电容上时,还同时会采样预放大级的输出噪声以及输入开关Saz引入的热噪声。放大器的输出噪声等效到输入端时会被自身增益衰减,而Saz的噪声不会被衰减。为进一步降低Saz在比较器输入端引入的噪声,本设计在传统设计基础上加入了低导通电阻的Saz_1开关,对Saz开关的噪声进行抑制,从而减小存储于

$C_{{\rm{az}}_1} $ 上的失调电压噪声。由于Saz、Saz_1开关噪声的非相关性,其在比较器输入端产生的噪声为:式中,

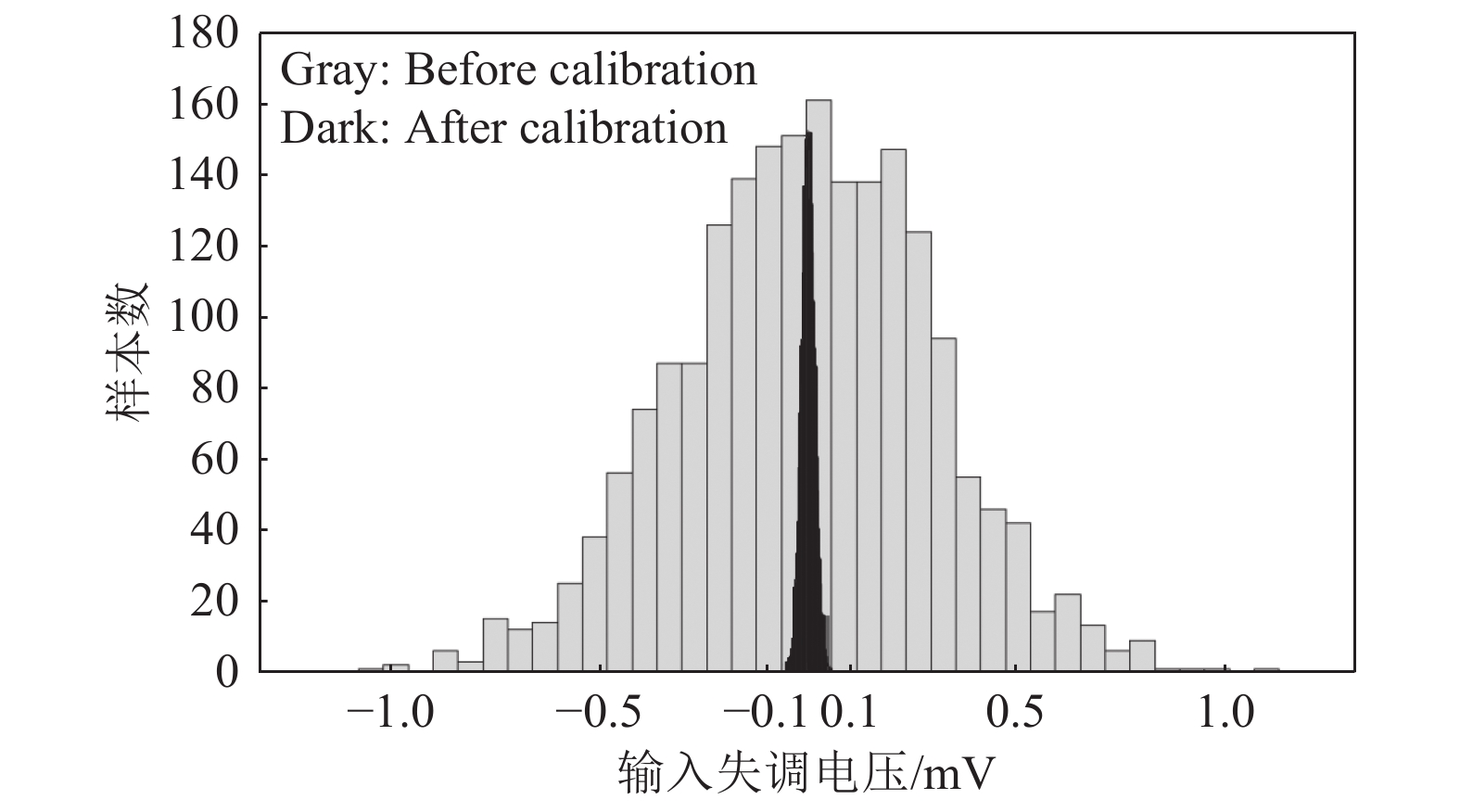

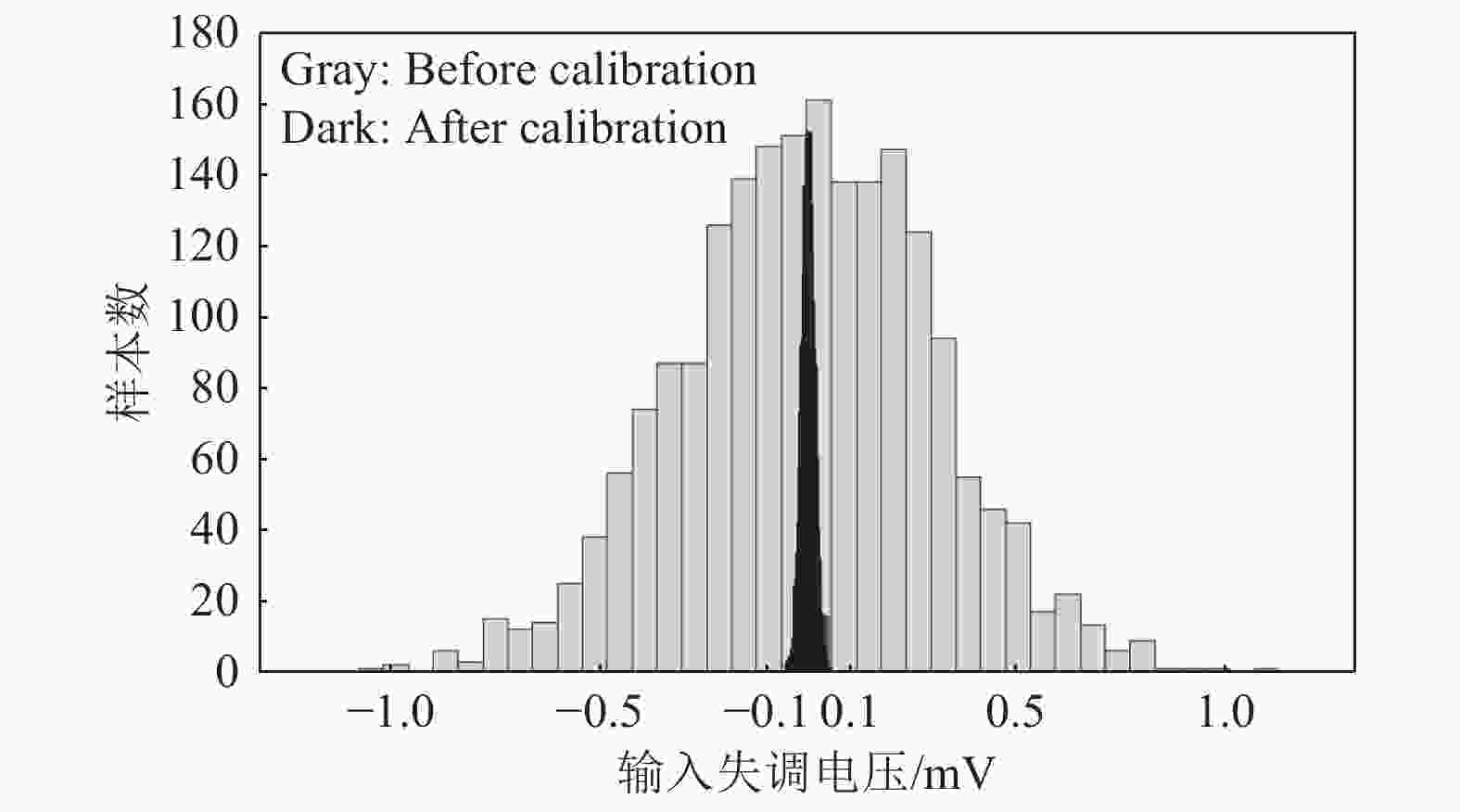

$ {{V}}_{\mathrm{n},\mathrm{s}\_\mathrm{a}\mathrm{z}} $ 和$ {{V}}_{\mathrm{n},\mathrm{s}\_\mathrm{a}\mathrm{z}\_1} $ 分别为Saz和Saz_1开关的噪声;$ {{R}}_{\mathrm{s}\_\mathrm{a}\mathrm{z}} $ 和$ {{R}}_{\mathrm{s}\_\mathrm{a}\mathrm{z}\_1} $ 分别为Saz和Saz_1的导通电阻。当$ {{R}}_{\mathrm{s}\_\mathrm{a}\mathrm{z}\_1} $ 远小于$ {{R}}_{\mathrm{s}\_\mathrm{a}\mathrm{z}} $ 时,Saz的噪声被衰减,且Saz_1的噪声很小,因此失调校准开关附加的噪声被抑制。第二级放大器的失调和噪声在等效到比较器输入时会被第一级放大器的增益衰减,因此第二级输入端的失调校准开关采用传统设计结构,节省面积。图9为校准前后比较器输入失调电压的蒙特卡洛仿真结果,经过校准,比较器的输入失调电压从校准前的±1.2 mV减小到了±70 μV。在正常比较模式,两级预放大器均工作在积分器状态,通过最大化设计输入差分对管跨导,在放大器电路中采用Cascode以及交叉反馈负载管技术提升稳态放大增益,克服了动态锁存器失调和噪声的影响。积分时间由时序电路控制。图7中开关Scmp_bst由自举电压控制,降低导通电阻和寄生电容,加快CDAC输出稳定速度。采用周期性地将预放大器输出短路的方法(由图7中的Srst信号控制)在CDAC建立稳定后再开始输出信号放大,避免了CDAC输出稳定过程中的波动造成锁存器误翻转。基于以上改进并对电路进行优化设计,仿真得到比较器的输入等效噪声最大为30 μVrms,满足16位ADC的要求。

-

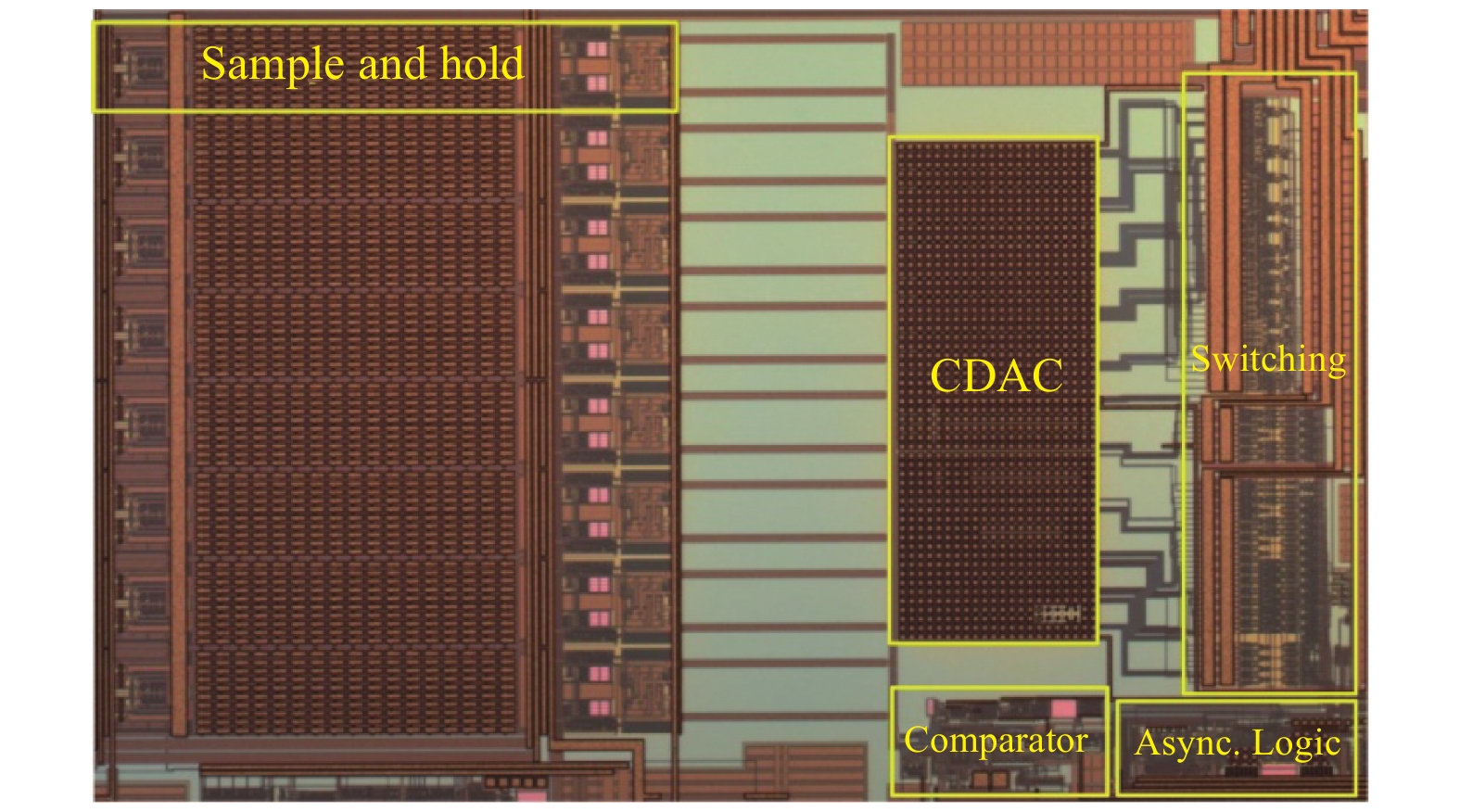

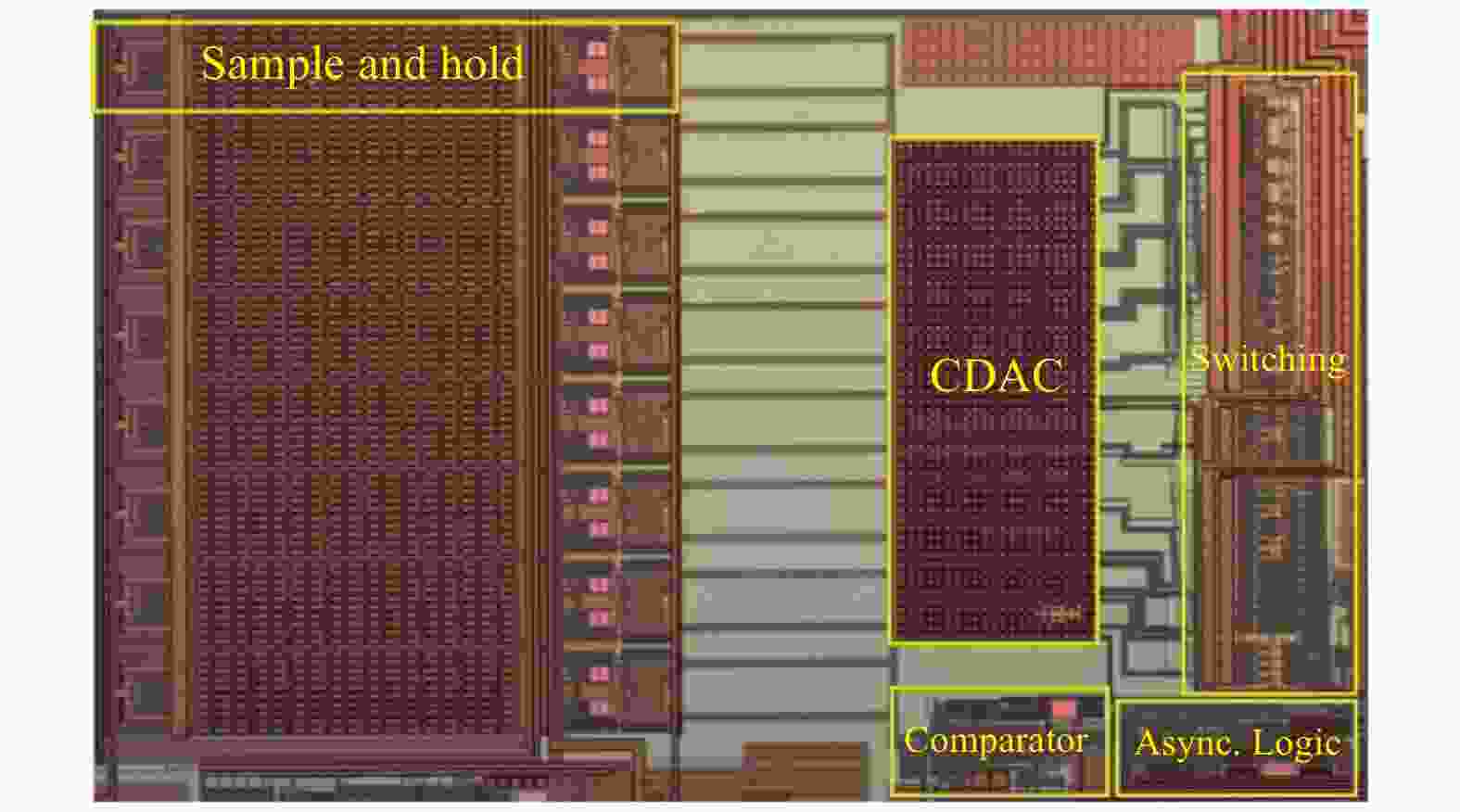

本文设计的ADC在CMOS 0.18 μm工艺上进行了流片验证,图10为测试芯片中ADC核心的照片,面积为1.15 mm2,芯片由外部5 V电源和片上1.8 V LDO供电。测试芯片包含8个ADC通道,各通道均以200 kS/s采样率工作,ADC内核对8个通道信号依次进行转换,完成一次转换需要500 ns,因此内部ADC实际转换速率可达625 kS/s。

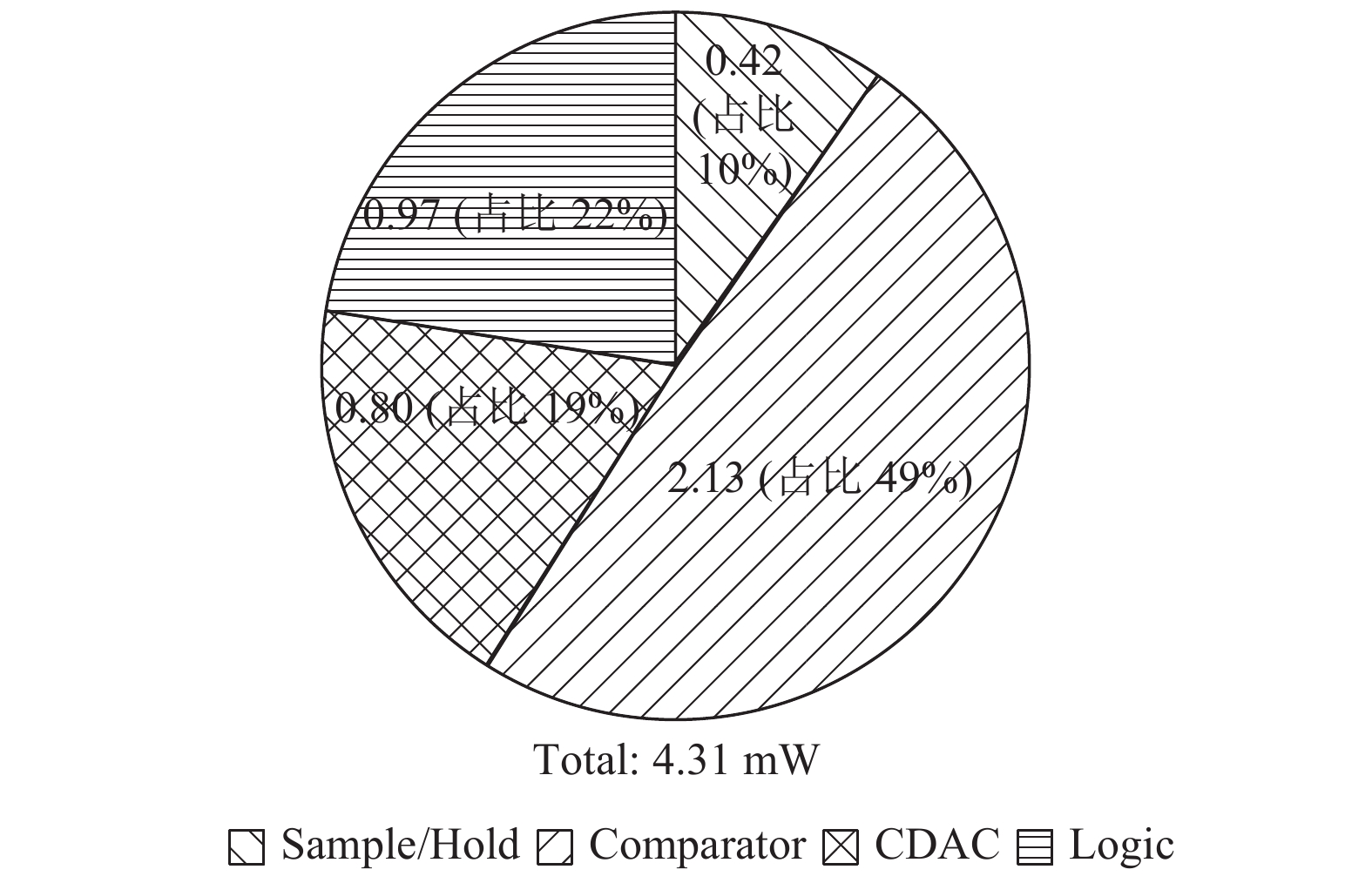

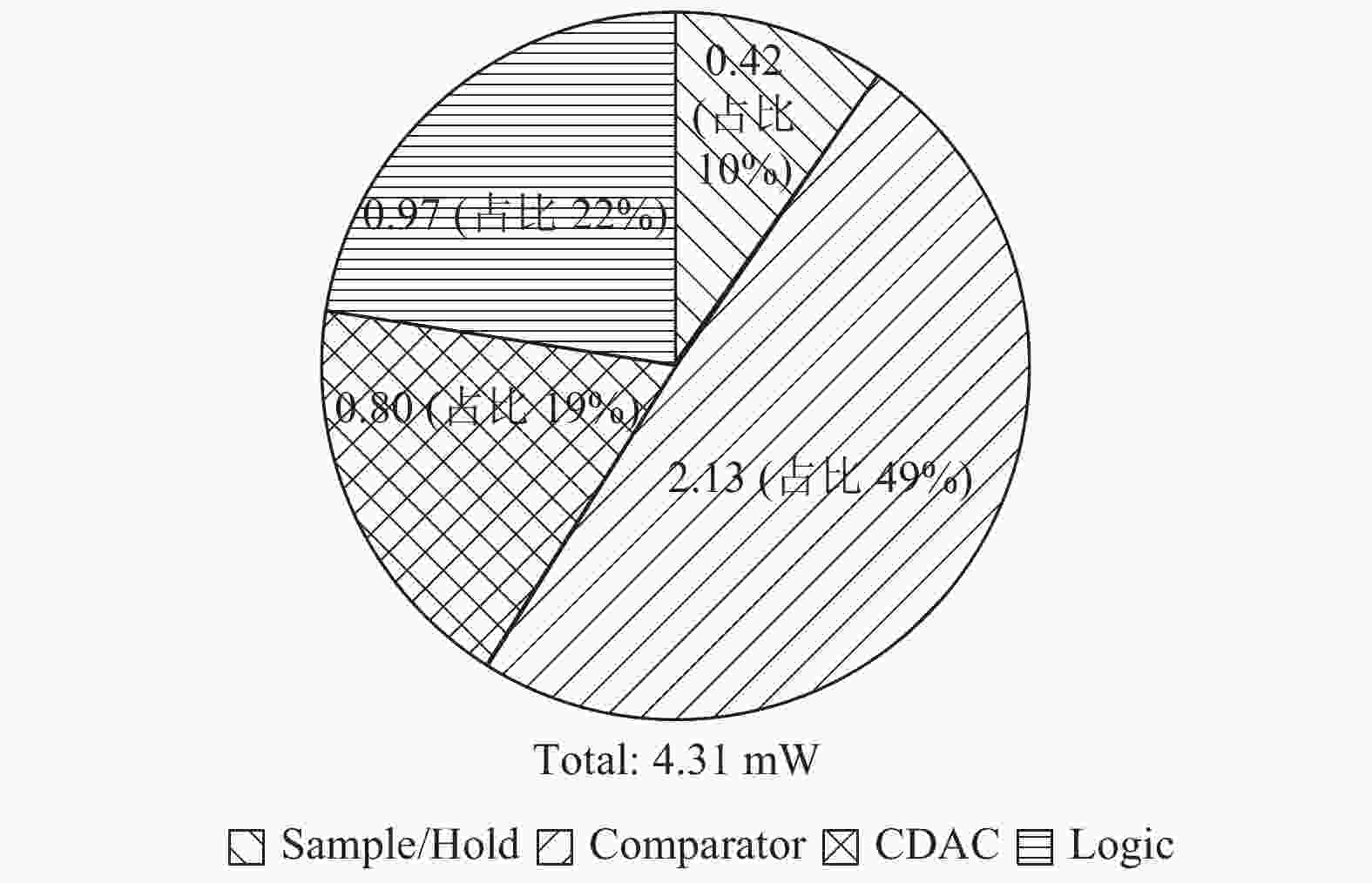

图11为27℃下ADC各部分功耗占比,ADC转换期间总消耗功率为4.31 mW,其中比较器占比最大,主要是因为第一级预放大器需要消耗较多的电流以满足噪声和失调需求。逻辑部分需要完成数据锁存、计算和非线性校准,功耗占比次之。得益于本设计优化的CDAC架构,其开关切换所需的能量占比较小。

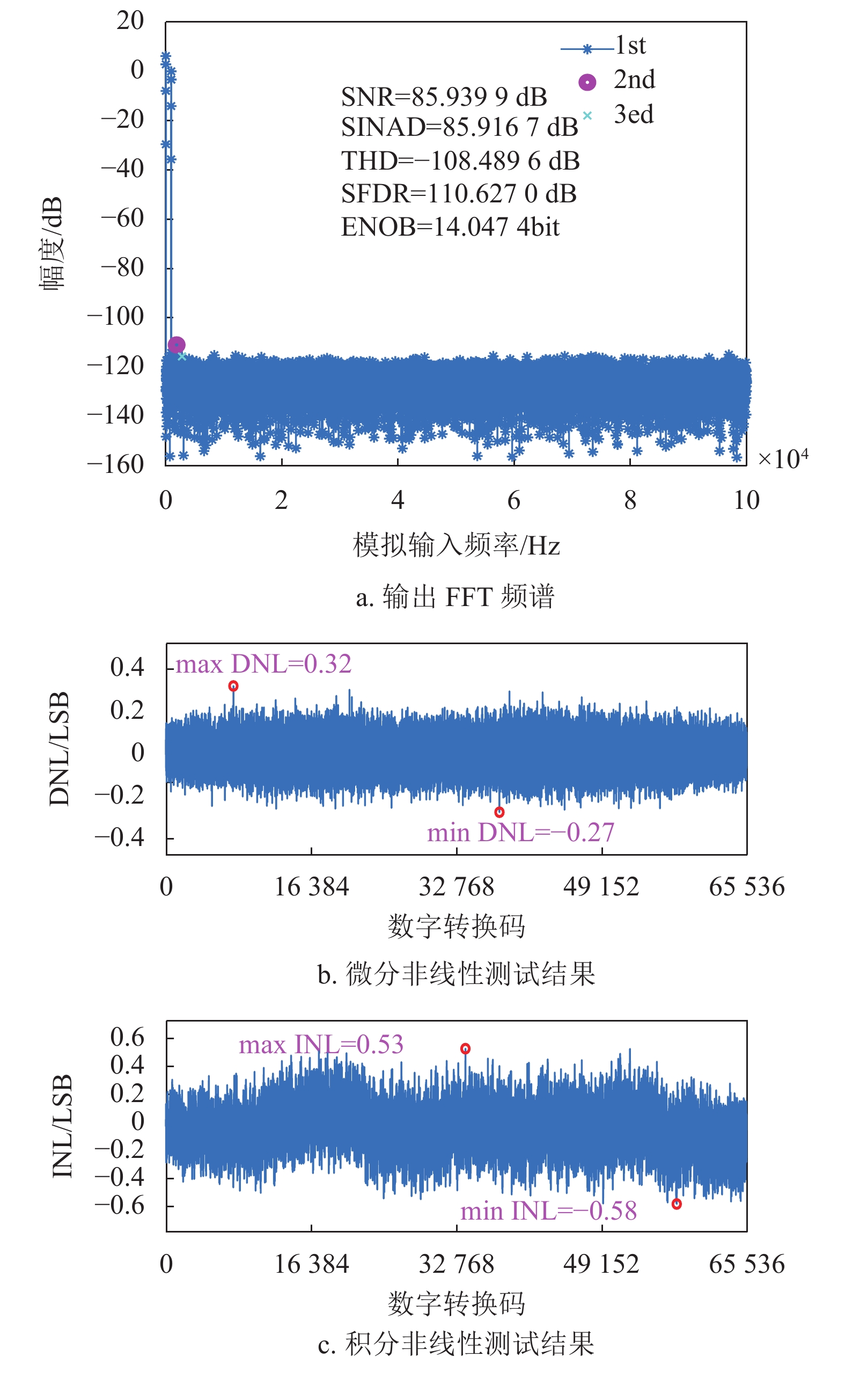

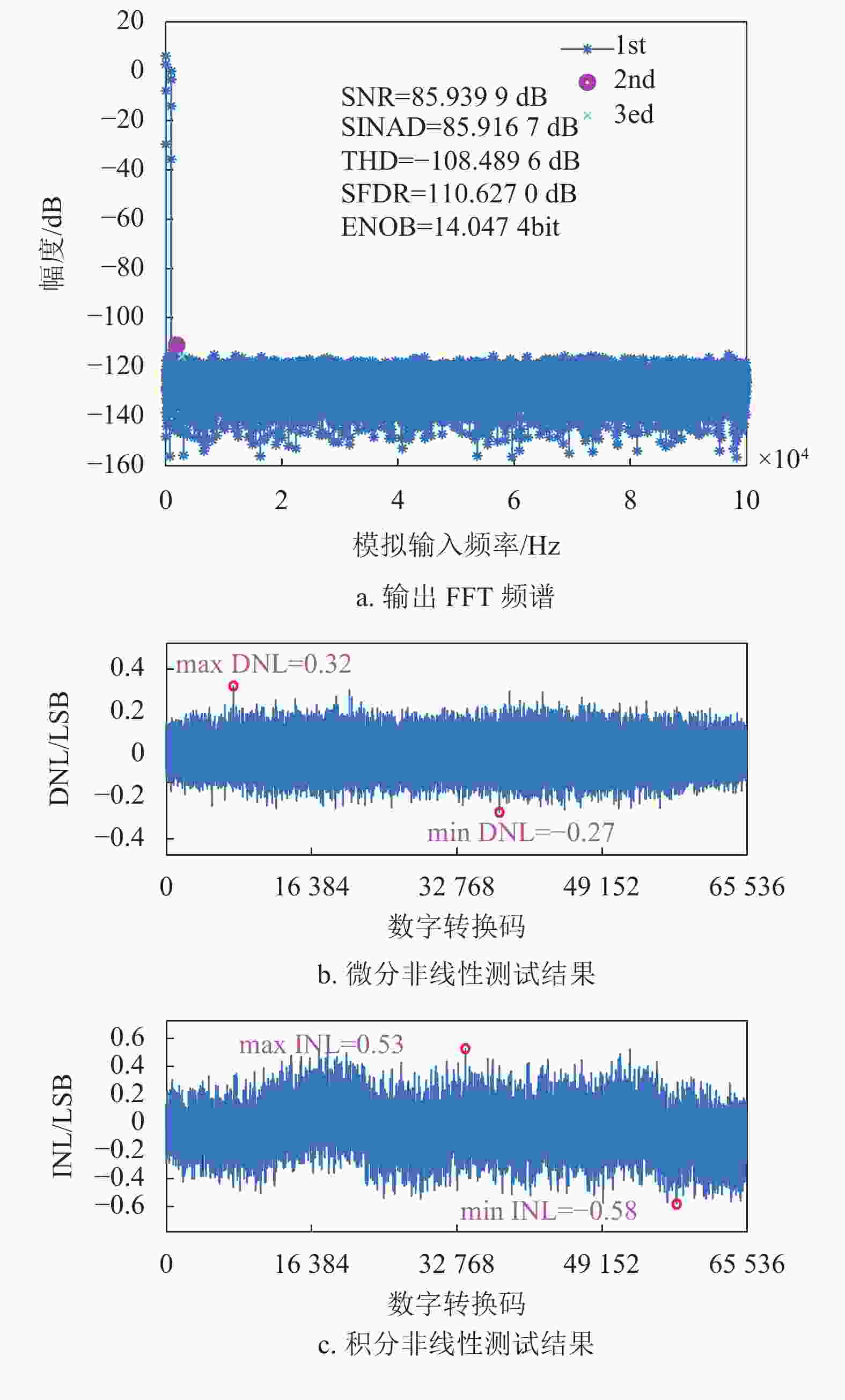

ADC动态性能测试通过外部信号源产生正弦波,经过片上驱动器输入ADC采样电路,转换后的数据在片外通过MATLAB程序进行快速傅里叶变换(FFT)分析计算。直流线性度测试通过输入正弦波,采集足够的转换数据点,利用码密度法计算微分非线性(DNL)和积分非线性(INL)。图12a为输入信号频率为1 kHz时,采集30 000个输出数据点得到的FFT频谱,信纳比(SINAD)为85.9 dB,有效位数(ENOB)为14位,SFDR为110.6 dB。图12b和图12c分别为输入信号频率为30 Hz时,采样2 160万个数据点分析得到的DNL和INL随转换码的分布,得到的DNL最大值为−0.27/+0.32 LSB,INL最大值为−0.58/+0.53 LSB。

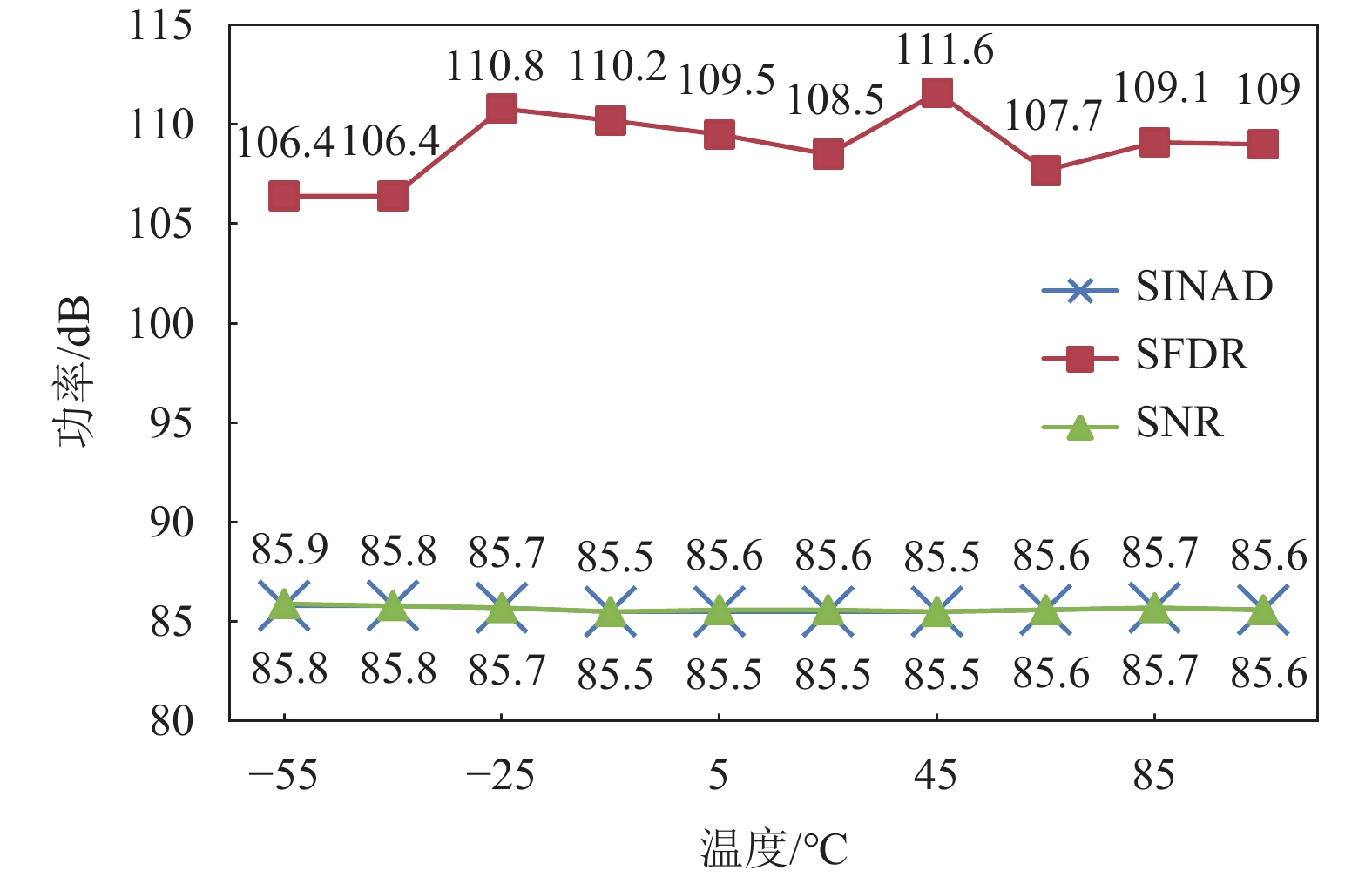

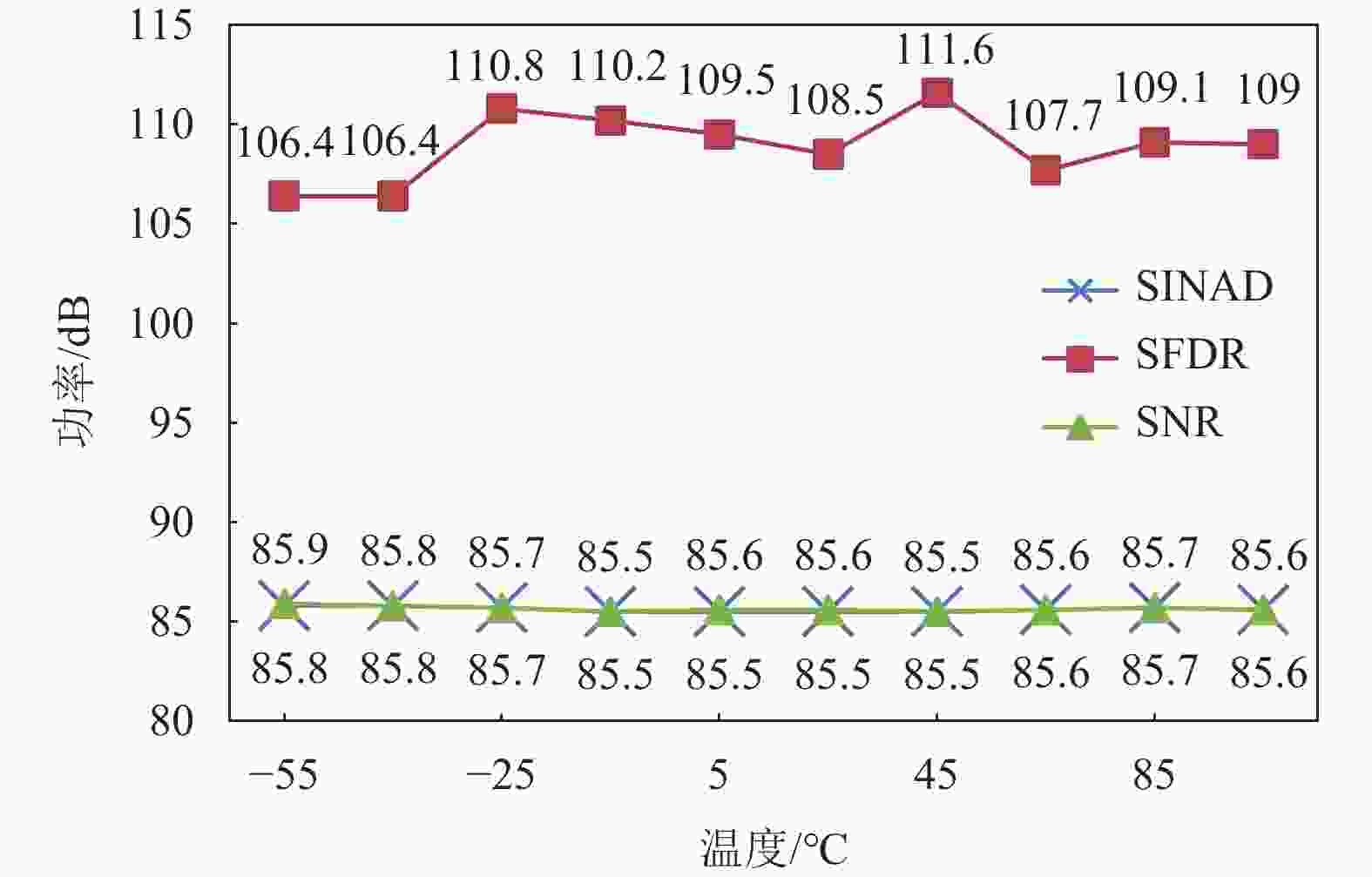

图13为ADC动态性能在−55 ℃~105 ℃范围内的测试结果,可以看到,SINAD在全温区内变化不大于0.3 dB,SFDR在全温区内变化不超过5.2 dB,线性度和噪声性能具有良好的温度稳定性。

表1为本文的ADC与近几年发表的文献中SAR ADC性能的比较,可以看到,本设计的ADC具有较大的输入范围,最大的无杂散动态范围和优良的直流线性度。同时也看到,在转换速率和噪声性能方面,本设计还有一定的提升空间。

参数 架构 工艺/μm 电源/V 分辨率/bit 采样率/(kS·s−1) 输入范围/Vpp SINAD/dB SFDR/dB DNL/LSB INL/LSB 面积/mm2 功耗/mW FOMs/dB* 本文 SAR 0.18 5/1.8 16 625 8.8 85.9 110 −0.27/+0.32 −0.58/+0.53 1.15 4.31 164.5 文献[2] BW-SAR 0.18 3.3/1.8 16 1000 1.8 83 100 −0.65/+0.45 −2.2/+2.1 0.53 1.05 169.8 文献[4] SAR 0.18 1.8 12 250 / 65.0 77.8 / / 0.36 0.0257 161.9 文献[11] SAR 0.5 5 16 200 20** 88.19 103.33 −0.52/+0.57 −0.67/+0.69 5.95 20 155.2 文献[12] SAR 0.6 12 V/5 V 16 250 10 80 / 3.2 7.3 1.8 6.36 152.9 *FOMs=SINAD+10log(Fs/2/Power)

**经过内部电阻网络衰减前的输入信号幅度 -

SAR ADC具有低延迟、结构相对简单、对工艺节点缩减友好以及低功耗等特点,也是众多新型混合架构高性能ADC中常用的子ADC结构。低噪声、大动态范围以及高线性度等指标对工业、医疗等应用中的高精度ADC至关重要。就SAR ADC而言,采样保持电路的线性度、CDAC的匹配及切换能耗、比较器的失调和噪声等因素都是制约其实现高精度的瓶颈。

本文基于CMOS 0.18 μm工艺设计了一种较大输入范围、16位分辨率的SAR ADC,提出了改进的采样保持电路结构优化采样线性度和噪声性能,采用分段结构设计的CDAC结合扰动注入以及混合型电容切换方式等技术优化了电路面积、噪声、线性度以及功耗。在比较器中采用两级积分型预放大器设计优化噪声,采用输出失调存储技术及优化的电路设计减小比较器失调电压和失调校准引入的噪声,采用自举开关及优化的时序控制提升比较器速度。测试结果表明,以上技术提升了ADC的动态和静态性能,设计的低功耗ADC具有优良的线性度和较低的噪声,适合工业场景等高性能数据采集系统应用。

A 16-Bit Low Power SAR ADC with 110 dB Spurious Free Dynamic Range

doi: 10.12178/1001-0548.2023272

- Received Date: 2023-10-31

- Rev Recd Date: 2023-11-28

- Available Online: 2024-04-01

- Publish Date: 2024-03-30

-

Key words:

- analog-to-digital converter (ADC) /

- digital-to-analog converter (DAC) /

- low noise comparator /

- offset calibration /

- sample and hold /

- successive approximation register (SAR)

Abstract: A 16-bit 625 kS/s Successive Approximation Register Analog-to-Digital Converter (SAR ADC) is presented. An improved sampling and hold circuit is proposed to optimize sampling linearity and noise performance. Segmented Capacitor Digital-to-Analog Converter (CDAC) is designed and hybrid capacitor switching method is adopted to reduce layout area and switching energy. Dither injection technique is used to improve ADC’s linearity. Two-stage integrating preamplifier is adopted to reduce comparator’s noise. Output offset storage and optimized circuit design techniques reduce comparator’s offset and noise induced by offset calibration. Comparator speed is also improved by circuit design. The prototype is fabricated using CMOS 0.18 μm process and occupies an active area of 1.15 mm2. With 1 kHz sinusoid input, the measured differential input peak-to-peak amplitude is 8.8 V. Signal to Noise and Distortion (SINAD) and Spurious Free Dynamic Range (SFDR) are 85.9 dB and 110 dB respectively. Differential Nonlinearity (DNL) and Integral Nonlinearity (INL) are −0.27/+0.32 LSB and −0.58/+0.53 LSB respectively with a power consumption of 4.31 mW.

| Citation: | XING Xianglong, WANG Qian, KANG Cheng, PENG Jiangling, LI Qing, YU Jun. A 16-Bit Low Power SAR ADC with 110 dB Spurious Free Dynamic Range[J]. Journal of University of Electronic Science and Technology of China, 2024, 53(2): 185-193. doi: 10.12178/1001-0548.2023272 |

ISSN

ISSN

DownLoad:

DownLoad: