## **Review of Electromigration Modeling of IC Interconnects**

MA Jian-guo<sup>1</sup>, YAO Ming<sup>1</sup>, and TAN Cher Ming<sup>2</sup>

(1. School of Electronic Engineering, University of Electronic Science and Technology of China Chengdu 610054;

2.School of Electrical and Electronic Engineering, Nanyang Technological University Singapore)

**Abstract** The history of electromigration (EM) modeling of IC interconnects is briefly reviewed. The widely used one-dimension (1-D) EM-induced back flow model is introduced. Based on the conception of atomic flux divergence (AFD), the EM modeling can also be mainly grouped into two approaches. One is the conventional diffusion path approach, which has explained many important phenomena in traditional Al on-chip metallization. However, the microelectronic industry has turned to Cu/low-k interconnects in need of better performances of the shrinking chip, and three-dimensional (3-D) integrated circuit technology is also introduced. In this trend, the driving force approach is developed, which can help to understand many phenomena in narrow interconnection. The finite element modeling (FEM) is used more and more in the driving force formalism.

Key words diffusion path approach; driving force approach; electromigration; FEM; ICs; interconnects; modeling

# 集成电路互连线电迁移建模综述

# 马建国<sup>1</sup>,姚 明<sup>1</sup>, TAN Cher Ming<sup>2</sup>

(1. 电子科技大学电子工程学院 成都 610054; 2. 新加坡南洋理工大学电气与电子工程学院 新加坡 639798)

【摘要】简要介绍了集成电路互连线建模发展的历史。回顾了曾广泛使用的一维电迁移引起的回流模型。基于原子通量 散度的概念,电迁移建模可以分为两种方法。一种是常用的扩散路径法,该方法能够解释传统的铝片上金属互连的许多重要 电迁移现象。然而,随着芯片尺寸越来越小,工业界为了追求更好的性能,转向了使用铜/低k组合作为互连材料,同时引进 了三维集成电路技术。顺应这种趋势,第二种驱动力电迁移建模方法发展了起来,该方法有助于人们理解窄互连工艺中的许 多现象。有限元模拟也越来越多地用于驱动力分析法。

**关 键 词** 扩散路径法; 驱动力法; 电迁移; 有限元; 集成电路; 互连线; 建模 中图分类号 TN47 **文献标识码** A doi:10.3969/j.issn.1001-0548.2009.05.003

## **1** Introduction

Concurrent to IC scaling, interconnect width and thickness are shrinking to nanometer. If an interconnect carries a current of several, the current density can be as high as  $10^6$  A/cm<sup>2</sup>. As a point of reference, this is on the order of 10 000 times that allowed for house wiring. Such current density can cause mass transport in the metal line at an operation

temperature of 100  $^{\circ}$ C and lead to void formation at the cathode and hillock at the anode, and this phenomenon is called electro migration (EM). The void formation in the interconnection results in increased line resistance or open circuit, and on the other hand, the hillock formation in the interconnection results in short circuit between adjacent interconnects. The two kinds of results can cause circuit functional (or parametric) failure.

作者简介:马建国(1961-),男,长江学者特聘教授,主要从事射频、微波、毫米波电路与系统,集成系统芯片(SoC)设计与验证方面的研究.

Received date: 2009 - 06- 05

收稿日期: 2009-06-05

Foundation item: Natural Science Foundation of China (NSFC60688101); National 111 Project

基金项目: 国家自然科学基金(NSFC60688101); 国家111工程

Biography: MA Jian-guo was born in 1961. He is a professor. His research interest is in RF, MW, MMW circuit and systems, SoC design and testing.

The electromigration phenomenon was first discovered in the 19th century. However, this topic remained of limit interest until the 1960's, when failures of interconnects in IC's due to electromigration were reported. Early EM studies focused on the electron wind force (EWF) as the sole driving force that makes the metal atoms to diffuse along the electron flow direction, based on ballistic transport theory. This EM formulation was reported by Fiks<sup>[1]</sup> and Huntington<sup>[2]</sup>. A few years later, Black<sup>[3]</sup> proposed a semi-empirical equation to calculate the median time to failure (MTF) of a group of interconnects under the same EM condition, and this is known as the famous Black equation. In this equation, the MTF of interconnects is related to the current density and temperature, both of which are assumed to be constants. Black equation is still widely used today as a general estimation of MTF in Al-based metallization. In 1976, Blech found the "Blech effect" phenomenon, and proposed the "back flow" effect of atoms in the opposite direction of electron flow due to back stress in the interconnect when voids and hillocks are formed<sup>[4-5]</sup>. In 1986, M. Shatzkes and J.R. Lloyd<sup>[6]</sup> provided a model in which the driving force is composed of the electromigration term and an opposing concentration gradient term acting in the presence of a "blocking boundary" with a vanishing atomic flux, and suggested a modification of Black equation. In 1993, Korhonen and his coworkers<sup>[7]</sup> also gave some solutions to the differential equation which is consisted of the electromigration term and a back stress term for several representative cases. Based on Shatzkes and Korhonen's contribution, a widely used 1-D model was developed, and it will be briefly introduced in this work. In Korhonen's model, the vacancy relaxation effects and vacancy equilibrium are not considered. Sarychev<sup>[8]</sup> proposed a more accurate model to predict the stress and vacancy evolution.

Since IC was born, Al has been used as the material of interconnects for decades. However, due to the trend of miniaturization, the industry has turned to Cu as the interconnect conductor in pursuit of low resistance-capacitance delay and cost. With respect to the shrinking line width and unique processing

technologies in Cu metallization, other driving forces such as stress gradient and temperature gradient induced driving forces become significant. So the traditional EM formalism in Al system and Black equation can no longer be blindly used in Cu systems.

In this work, an elaboration of the diffusion path and driving force approaches will be presented. We will see that EM is the fact that the metal atoms move through various diffusion paths under several driving forces in metal interconnection. The temperature and thermo-mechanical stress in the various part of the IC are highly dependent on the surrounding materials (the inter-layer dielectrics, the cap layers, and the liners) and their materials properties, including their thermal conductivities, thermal expansions, Young modulus, etc., and the architectures of the IC will also affect the current density, temperature, and thermo-mechanical stress distributions. A change in design geometry and process of an interconnect system could result in a change of dominant driving force and diffusion path, and, thus making the EM modeling more complicated, especially in Cu-based systems. So we turn to numerical tools to have a better understanding of the intrinsic physics in EM. The numerical modeling of EM can be built using finite-element-analysis (FEA), and in the view of the above mentioned, the traditional 1-D model can no longer be used in the electrical-thermal-mechanical analysis, so a 3-D finite element modeling (FEM) is required. The method of static and dynamic simulation to study the void nucleation and evolution will be presented in this work.

## 2 An Early 1-D Analytic Model of EM

As the evolution of EM modeling, several sophisticated EM models have been developed. In this paper, we only take the EM-induced back stress build up (back flow) model of Shatzkes and Korhonen for example, as this model has been widely used in traditional 1-D EM analysis.

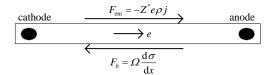

Fig. 1 shows a top view of an interconnect ended with two vias as diffusion barriers which are denoted by dark areas. When a difference in electrical potential is applied to the interconnect, electrons flow from the cathode to the anode terminal, and the atoms start to diffuse along the electron flow direction due to scattering and momentum transfer. There are two forces acting upon the atoms, one is the electron wind force which is along the electron flow, the other is the electrostatic force which it is in the opposed direction and it is much smaller than the first one when EM happens. The resultant force of the two is usually called the electron wind force for simplicity, and it can be expressed as <sup>[6]</sup>:

$$F_{\rm em} = -q^* E = -Z^* e \rho j \tag{1}$$

where  $q^* = Z^* e$  is the effective atomic charge,  $Z^*$  is the effective atomic charge number, e is the fundamental electron charge,  $E = \rho j$  is the electric field,  $\rho$  is the electrical resistivity of the metal, and j is the current density. A negative sign for j means current density is opposite to the electron flow direction.

Fig. 1 Electron wind force and back stress on an interconnect (on the top view).

In an interconnect terminating at diffusion barriers such as Tungsten (W) filled vias in Al systems or Tantalum (Ta) liners in Cu systems, atoms are driven by EWF and deplete near the cathode thus creating tensile stress while compressive stress occurs near the anode because of the atom accumulation. The resulting stress gradient leads to a mechanical driving force, referred to as the back-stress force, which opposes the electromigration wind force. The net atomic flux can be expressed as <sup>[7]</sup>:

$$J_a = \frac{cD}{kT} (\nabla \mu + q^* E)$$

(2)

where *c* is the atomic concentration, *k* is the Boltzmann's constant, *T* is the temperature, and *D* is the atomic diffusivity. The chemical potential  $\mu$ , depends on the hydrostatic stress,  $\sigma$ , as  $\mu = \mu_0 - \Omega \sigma^{[9]}$ , where  $\Omega$  is the atomic volume. The stress is tensile for  $\sigma > 0$ ,and compressive for  $\sigma < 0$ . So the atomic flux can be written as:

$$J_a = -\frac{cD}{kT} \left( -\Omega \frac{\partial \sigma}{\partial x} + q^* E \right)$$

(3)

The vacancy flux (which is opposite to the atomic flux) for EM mass transport is:

$$J_{v} = -J_{a} = \frac{cD}{kT} \left( -\Omega \frac{\partial \sigma}{\partial x} + Z^{*} e\rho j \right)$$

(4)

In confined metal lines, the relative density change dc/c corresponds to an increment in stress as <sup>[7]</sup>:

$$\frac{\partial c}{c} = -\frac{\partial \sigma}{B} \tag{5}$$

where *B* is the applicable modulus. The continuity equation in the line direction gives the material balance as  $^{[7]}$ :

$$\frac{-\partial J_a}{\partial x} = \frac{\partial c_v}{\partial t} + \left(\frac{c}{B}\right)\frac{\partial \sigma}{\partial t}$$

(6)

where  $c_{\nu}$  is the vacancy concentration. Then the continuity equation (6) becomes <sup>[7]</sup>:

$$\left(\frac{B\Omega}{kT}\frac{c_{\nu}}{c}+1\right)\frac{c}{B}\frac{\partial\sigma}{\partial t}+\frac{\Omega}{kT}\frac{\partial}{\partial x}\left[c_{\nu}D_{\nu}\left(\frac{\partial\sigma}{\partial x}\frac{q^{*}}{\Omega}E\right)\right]=0$$

(7)

using equation (7), the electromigration-induced stress evolution in the interconnect can be calculated.

With Fick's second law in diffusion giving as:

$$\frac{\partial c}{\partial t} = -\mathrm{div}J_{v} \tag{8}$$

equation (4) becomes<sup>[10]</sup>:

$$\frac{\partial c}{\partial t} - D \frac{\partial}{\partial x} \left( \frac{\partial c}{\partial x} - \frac{Z^* e \rho j}{kT} c \right) = 0$$

(9)

The solutions to equation (6) with a fixed boundary condition for all *x* respectively were reported by reference<sup>[6]</sup>, and the time-to-failure ( $t_f$ ) was expressed as:

$$t_f = BT^2 j^{-2} e^{E_A/kT}$$

(10)

where  $E_A$  is the activation energy for grain-boundary self-diffusion.

Although the 1-D model has its limitations for metallization with various structures and surrounding materials, the healing effect of the mass backflow due to EM-induced inhomogeneities is still considered as an important role in the reduction of the EM growth rate.

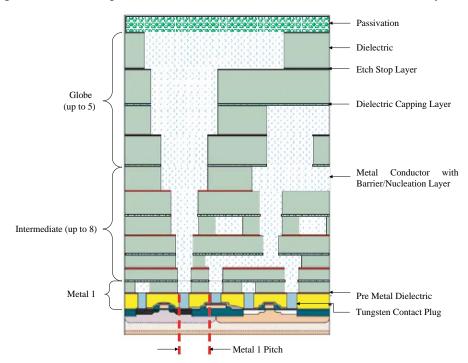

As 3-D IC is an emerging technology for the near future, ICs can have up to 14 layers of metal interconnects as predicted by the International Technology Roadmap for Semiconductors (ITRS)

#### 2003 edition (Fig. 2), so more complicate models of IC EM need to be built, theoretically and numerically.

Fig.2 Cross-section of an integrated Circuit showing multi-layer metal interconnects on top of a device layer [11]

## **3** Two Developed Models of EM

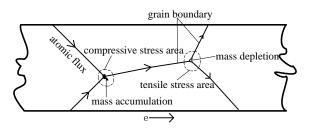

EM is a mass transport phenomenon. In any part of a metal interconnect, if the material flowing into and out from the part is exactly the same, void will not occur. EM failure happens only when there is a non-zero atomic flux divergence, that is,  $\nabla J_a \neq 0$ which leads to mass accumulation or depletion. A typical AFD area is the so-called "triple point", which is usually the junction of three metal grains. Fig. 3 shows two triple points: the right one is a mass depletion area, which leads to void formation; the left one is a mass accumulation area, which causes hillocks.

#### Fig. 3 AFD in triple points

In steady state, the vacancy generation rate is equal to the opposite value of the atomic flux divergence<sup>[12]</sup>.

The failure line occurs around the point where the divergence of the atomic flux is maximum<sup>[13]</sup>. During EM process, AFD varies with diffusion paths and time. It was theoretically proved that the failure time is the inversely proportional to the averaged AFD by the equation below <sup>[14]</sup>:

$$N_0 = t_f \cdot \overline{\text{AFD}} \tag{8}$$

where  $N_0$  is the initial atomic concentration of a given metal and it is a constant. AFD is the volumeaveraged total AFD averaged over the time of  $t_f$ . In other words, AFD can be employed to predict the EM lifetime qualitatively. A decrease of AFD can improve the interconnect EM life time, and this can give us a design guide.

Developed with the concept of AFD, the EM formulation can be mainly grouped into two approaches, one is the diffusion path approach and the other is the driving force approach.

## 3.1 Diffusion Path Approach

In this approach, all kinds of EM mass transport are assumed to be caused by electron wind force. Vacancies and metal atoms flow along one or more dominate diffusion paths related to a given interconnect structure, and other paths could be negligible<sup>[15]</sup>. The atomic flux due to the EWF is traditionally expressed as <sup>[16]</sup>:

$$\overline{J_A} = \frac{N}{k_B T} Z^* e \rho D_0 \exp\left(-\frac{E_A}{k_B T}\right) \overline{j}$$

(9)

The inhomogeneity of the interconnect microstructure leads to different atomic diffusivities along the various diffusion paths. There are actually several possible diffusion paths for electromigration transport in an interconnect such as surface, interface, grain boundaries, bulks, pipes, and lattice. The fastest diffusion path can be identified as the dominate diffusion path that drives EM failure, and this identification can be based on the drift velocity equation <sup>[17]</sup>:

$$v_{d} = \frac{D_{\text{eff}}}{kT} (F_{\text{em}} + F_{b}) = \frac{D_{\text{eff}}}{kT} \left( Z_{\text{eff}}^{*} e\rho j - \Omega \frac{\partial \sigma}{\partial x} \right) \quad (10)$$

From equation(10) and ignoring the back-stress flow, the various diffusion paths can be expressed as<sup>[18]</sup>:

$$D_{\rm eff} Z_{\rm eff}^* = D_b Z_b^* f_b + D_s Z_s^* f_s + D_i Z_i^* f_i + D_{gb} Z_{gb}^* f_{gb} + D_p Z_p^* f_p$$

(11)

The subscripts denote various diffusion paths as follows: *b*: bulk, *s*: surface, *i*: interface, *gb*: grain boundary, *p*: pipe, with  $f_r$  (r = b, *s*, *i*, *gb*, *p*) as the fraction of atoms diffusing through a given path way, which depends on the geometry of the interconnect. As bulk and pipe diffusion can be negligible at the temperature below 400 °C, EM failures are assumed to mainly arise from surface, interface and grain boundary diffusion paths <sup>[18]</sup>.

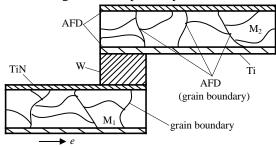

In Black's equation, activation energy in dominant diffusion path is an important factor to determine the interconnect life time. In Al systems, the major diffusion paths are grain boundaries and metal/oxide or metal/barrier interfaces. Because Al tends to protect its surfaces by forming aluminum oxide, and the activation energy for interfacial diffusion is greater than that for grain boundary diffusion, grain boundary diffusion will dominate in Al systems. Fig. 4 shows an idealized schematic of 2-level Al. We can see the triple points of grain boundaries can serve as centers of AFD. So reducing the number of triple points can be a way of improving the interconnect life time. Surface diffusion will only be observed in large grain films or in narrow lines that exhibit a "bamboo" structure, and in this situation, void is often located at the cathode end of the W<sup>[19]</sup>.

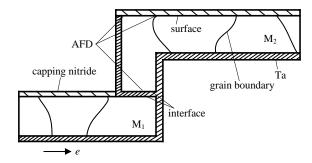

Cu, on the other hand, does not adhere well to oxides, and its surface is not self-protective. Especially for Cu interconnects in the deep submicron regime, which can possess more bamboo-like microstructure, there are few grain boundaries to provide effective diffusion paths, even if the grain boundary pathways is indeed the fastest overall. The activation energy possessed by interface or surface diffusion paths is lower than the others. So the EM failure in Cu-based metallization is surface/interface dominated in contrast to grain boundary dominated failure in Al-based metallization. Fig. 5 shows an idealized schematic of 2-level bamboo-like dual-damascene (DD) Cu interconnect. where surface diffusion is dominated<sup>[20]</sup>. In DD metallization, the interface between the capping nitride and M<sub>2</sub> can be regarded as the surface, and usually this surface is considered as the fastest diffusion path, compared to Cu/Ta interface and grain boundary. If the electrons flow from  $M_1$  to  $M_2$  as demonstrated in Fig. 5, failure sites will locate at the cathode end of  $M_2$ , where the Ta liner and the capping layer meet. The Cu/Ta interface at the cathode end of the via can be another important AFD sites, too. Thus a bimodal failure distribution, which is an important factor of quantitative reliability evaluation in DD systems, is often found. Generally, EM diffusion in DD Cu is likely to follow the hierarchy of surface> interface  $\geq$  gb >> other pathways <sup>[18]</sup>

Fig. 4 Idealized schematic of 2-level Al interconnect

Fig. 5 Idealized schematic of 2-level DD Cu interconnect (bamboo like)

### 3.2 Driving Force Approach

Black equation is a classic equation, but it was presented for Al interconnects and it is assumed that electron wind force is the only driving force for EM. With the appearance of Cu interconnect and low-k material, that is not a suitable case now. As interconnect line width shrinks to submicron level, the diffusion path approach can also no longer explain some important EM phenomena in narrow interconnection, as other driving forces become dominant <sup>[21]</sup>.

In the driving force approach, other sources of driving force such as non-uniform temperature and stress can counteract the electron wind force, and their impact on EM cannot be ignored. These driving forces produce different massflow mechanisms such as electron-wind force-induced migration (EWM), thermo-migration (TM), stress migration (SM), and surface migration (SFM), etc. Some researchers also concluded that atomic concentration gradient migration (ACGM) can not be ignored <sup>[22-23]</sup>, while in this work, we considered the atomic concentration gradient is the result of EMW, and is not a unique cause of driving force <sup>[15]</sup>. As the SFM is not so significant as TM and SM during most part of the EM process, we only discuss the SM and TM driving forces.

3.2.1 Stress Migration

The AFD driven by stress gradient is called stress migration, and can be formed as <sup>[16]</sup>:

$$\overline{J_s} = \frac{N\Omega D_0}{kT} \exp\left(-\frac{E_A}{kT}\right) \nabla \sigma_H$$

(12)

where *N* is the atomic density.  $D_0$  is the prefactor of the self-diffusion coefficient,  $\sigma_H$  is the hydrostatic stress.

Generally, there are two sources of stress gradient

which may influence EM failure in metal interconnect. The first one is the above mentioned back-stress force. In an interconnect terminating at diffusion barriers such as Tungsten (W) filled vias or Tantalum (Ta) liners, the "electron wind" force creates tensile stress near the cathode where the atoms deplete and compressive stress near the anode where the atoms accumulate. The resulting stress gradient leads to the back-stress force, which opposes EWF.

The second source is the thermo-mechanical stress gradient due to different thermal expansion coefficient of metal interconnect and its surrounding materials. For example, when the water is cooled from high deposition temperatures, the metal wants to shrink much more than the surrounding medium. Therefore, the metal is left in a state of very high tensile stress that causes the metal failing faster. This stress gradient can be anywhere in interconnects. It is suggested that thermo-mechanical stress gradient induced driving force acts at the very beginning of EM, and causes void to form. After that, it is relaxed during void formation <sup>[24]</sup>.

The two kinds of stress play a different role in EM. The back-stress force compensate the AF caused by EWF, and is only along the length of interconnect, while the thermo-mechanical stress makes the interconnect fail faster, and can be find in any place in the interconnect.

#### 3.2.2 Thermo-Migration

Though been neglected for many years, temperature gradient induced thermo-migration has been proved a dominant driving force recently <sup>[15, 25]</sup>. It can be expressed as <sup>[16]</sup>:

$$\overline{J_{th}} = -\frac{NQ^*D_0}{kT^2} \exp\left(-\frac{E_A}{kT}\right) \nabla T$$

(13)

where  $Q^*$  is heat of transport.

Atoms tend to move from a high temperature region to a low temperature region. Thus temperature gradient is expected to contribute to the resultant atomic flux, inducing a driving force. It was shown experimentally by Guo et al. <sup>[26]</sup> that an increasing temperature in the direction of electron flow greatly improved the MTF of electromigration. F. Giroux and his co-workers <sup>[14]</sup> also declared that in the SWEAT

test structures, the temperature gradient controls the movement of the AFD points. Temperature gradient can also disintegrate the components of an initially homogeneous two phase alloy, because one component diffuses preferentially faster to the cold end, and as a result the hot region becomes depleted in that component<sup>[27]</sup>. Temperature gradient comes from Joule heating at the interconnect surface, via regions, structural variation such as thickness and width, and so on. Typically temperature gradient is higher near the edges and surfaces where different materials meet. Temperature gradient is affected strongly by the heat dissipation path, such as the vias, which must be considered as an important role in the thermal profile of interconnect structures <sup>[28]</sup>, and a proper design of geometries of interconnect will be possible to improve its life-time.

## 4 Finite Element Modeling of the Driving Force Formalism

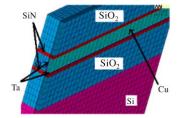

In order to incorporate different driving forces in EM diffusion process, finite element modeling is used<sup>[29]</sup>. Dalleau and Weide-Zaage also developed a finite element analysis model integrating the driving forces and voiding growth dynamics<sup>[30]</sup>.

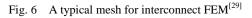

Finite element models can be established in multi-physics 3-D finite element analysis software such as ANSYS<sup>®</sup>, based on the equations of (9), (12), (13). The basic formalism for driving force using FEM can be categorized into two different approaches, depending on whether the diffusion time is directly or indirectly coupled with the interacting fields such as current, temperature, stress, etc. Both approaches assume void will occur at the highest positive AFD site. A typical mesh for FEM is showed in Fig. 6.

In order to point out the void nucleation sites, static simulation should be carried out. In this method,

electrical-thermal coupled field thermaland mechanical coupled field FEA are performed, and the location of the maximum total AFD which is also the initial void location of the structure can be found. The maximum AFD sites due to several driving forces are calculated respectively, too. If the maximum AFD site due to one driving force is coincide with the maximum total AFD site, this driving force can be regarded as the dominant one in EM, for example, stress gradient induced driving force in narrow interconnections<sup>[32]</sup>. The typical AFD distributions from various driving forces are shown in Fig. 7, and we can conclude that in this situation, stress gradient induced driving force is dominant.

Fig. 7 Static simulation of AFD distribution in Cu DD line–via structure in the case of  $M_1$  test<sup>[33]</sup>

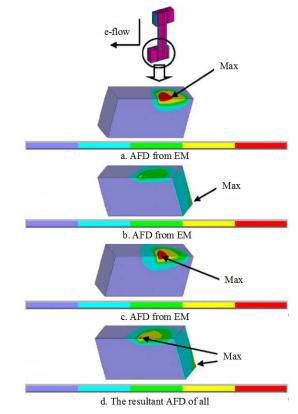

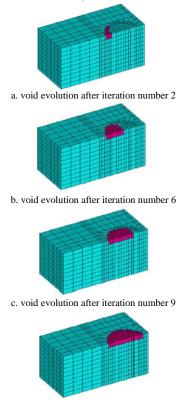

After the void nucleation, void evolution due to the continuous removal of the material from the nucleation sites can be analyzed, using dynamic simulation, which also carries out the electricalthermal coupled field and thermal-mechanical coupled field FEA to determine the total AFD value. Fig.8 shows a process of dynamic simulation, which is an iterative process<sup>[13]</sup>. In each loop of this simulation, a certain number (20 or 30) of elements with the highest total AFD value are selected and then deleted physically, followed by the calculation of the highest AFD sites again. So the geometry of the EM model is then modified. And this process repeats itself until a certain critical value, e.g. 20% increase of the interconnect resistance, is achieved, and the final failure profile of the metal line can be identified.

d. void evolution after iteration number 13

Fig.8 Dynamic simulation of void evolution process <sup>[15]</sup>

In the above two kinds of simulations, void nucleation cannot be simulated. As we know, in early stage of EM, voids are nucleated by vacancies migrating along various diffusion paths and merging into each other, in order to minimize the system energy. The Monte Carlo algorithm can be used for this process. Recently, a more realistic EM dynamic simulation model was provided by Li et al. <sup>[34]</sup>. They used Monte Carlo simulation for the initial void nucleation process, and combined both diffusion and driving force approach to model the void growth. They showed that the barrier layer-grain boundary intersections are the weakest points for the void formation in Cu metallization due to the thermal mismatch of different materials at that place.

Recently, a method of converting 2-D circuit layout into a 3-D model has been reported<sup>[35]</sup>. First, the circuit layout in drawn is Cadence (a circuit simulator), and the current and voltage can also be determined. Then through a simulation file transition, the Cadence file is converted to an ANSYS compatible one, and additional layers are also imported into ANSYS. After that, the transient thermal and structural analysis is performed using ANSYS, and the thermal and stress distribution of the circuit can be plotted, to help improving the circuit reliability.

The flip chip solder joints have became another major reliability concern in microelectronic devices these years. The material in solder joints, leads as SnPb, needs much smaller current density to cause EM than Al and Cu needs, while the current crowding effect in a flip chip joint lead to a high current density at the contact interface<sup>[35]</sup>. So, EM problem can be serious in this special kind of metal interconnect, and its EM formalism can be modeled by driving force approach and FEM<sup>[22, 36]</sup>, too. L.H. Liang etc.<sup>[23]</sup> also concluded that the ACGM should be taken into account in the FEA.

### 5 Summary

Electromigration has been a major concern in IC reliability for decades. This work reviews several EM modeling approaches to determine the key factors that affect the EM performance of an interconnection system. The conventional diffusion path approach alone can no longer be adequate to explain the EM phenomena in narrow interconnections of ULSI. The inclusion of other driving forces besides electron wind force in the study of EM for narrow interconnections is necessary. As EM is a complicated process related to the metal line and its surrounding materials, a 3-D finite element modeling is necessary and useful to couple different key factors which affect the EM performance together. There is still much work to do to predict the EM time-to-failure of interconnects through dynamic simulation.

#### References

[1] FIKS V B. On the mechanism of the mobility of ions in

metals[J]. Sov Phys Solid, 1959, 1: 14.

- [2] HUNTINGTON H B, GRONE A R. Current-induced marker motion in gold wires[J]. J Phys Chem Solids, 1961, 20: 76-87.

- [3] BLACK J R. Electromigration failure modes in aluminum metallization for semiconductor devices[J]. Proc IEEE, 1969, 57(9): 1587-1594.

- [4] BLECH I A. Electromigration in thin aluminum films on titanium nitride[J]. J Appl Phys, 1976, 47: 1203-1208.

- [5] BLECH I A. HERRING C. Stress generation by electromigration[J]. Appl Phys Lett, 1976, 29: 131-133.

- [6] SHATZKES M, LLOYD J R. A model for conductor failure considering diffusion concurrently with electromigration resulting in a current exponent of 2[J]. J Appl Phys, 1993,59: 3890-3893.

- [7] KORHONEN M A, BØRGESEN P, TU K N, et al. Stress evolution due to electromigration in confine metal lines[J]. J Appl Phys, 1993, 73: 3790-3799.

- [8] SARYCHEV M E, ZHITNIKOV Y V, BORUCKI L, et al. General model for mechanical stress evolution during electromigration[J]. Thin Solid Films, 2000, 365: 211-218.

- [9] HERRING C. Effect of change of scale on sintering phenomenon[J]. J Appl Phys, 1950, 21: 301-303.

- [10] CLEMENT J J, LLOYD J R. Numerical investigations of the electromigration boundary value problem[J]. J Appl Phys, 1992, 71: 1729-1731.

- [11] The ITRS organization. International technology roadmap for semiconductors[EB/OL]. [2009-02-03]. http://public. itrs.net.Interconnects.

- [12] SCORZONI A, CAPRILE C, FANTINI F. Electromigration in thin-film interconnection lines: models, methods and results[J]. Mat Sci Rep, 1991, 7: 143-220.

- [13] GIROUX F. Current and temperature distribution impact on electromigration failure location in SWEAT structure [C]//Proc IEEE Int Conference on Microelectronic Test Structures. [S. l. ]: IEEE, 1994, 7: 214-217.

- [14] TAN C M, HOU Y, LI W. Revisit to the finite element modeling of electromigration for narrow interconnects[J]. J Appl Phys, 2007, 102: 033705.

- [15] TAN C M, ROY A. Electromigration in ULSI interconnects[M]. [S. l. ]: Mater Sci and Engi, 2007.

- [16] TAN C M, ROY A. Investigation of the effect of temperature and stress gradients on accelerated EM test for Cu narrow interconnects[J]. Thin Solid Films, 2006, 504: 288-293.

- [17] HU C K, ROSENBERG R, LEE K Y. Electromigration path in Cu thin-film lines[J]. Appl Phys Lett, 1999, 74: 2945-2947.

- [18] OGAWA E T, LEE K D, BLASCHEKE V A, et al. Electromigration reliability issues in dual-damascene Cu interconnects[J]. IEEE Trans Reliab, 2002, 51: 403.

- [19] HU C K, HO P S, SMALL M B. Electromigration in two-level interconnect structures with Al alloy lines and W studs[J]. J Appl Phys, 1992, 72: 291-293.

- [20] HU C K, LEE K Y, GIGNAC L, et al. Electromigration in physical vapor deposited copper lines[C]// in AIP Conf Proc Stress Induced Phenomena in Metallization: 4th Int. Workshop. [S. l. ]: [s. n. ], 1998.

- [21] TAN C M, ROY A, VAIRAGAR A V, et al. Current crowding effect on copper dual damascene via bottom

failure for ULSI applications[J]. IEEE Trans Device Mater Reliab, 2005, 5: 198-205.

- [22] CHEN X F, LIANG L H. Electromigration simulation with consideration of the atomic concentration gradient[C]//2008 International Conference on Electronic Packaging Technology & High Density Packaging. [S.l.]: [s.n.], 2008.

- [23] LIANG L H, ZHANG Y X, CHEN X F. A new algorithm for EM analysis considering multiple driving forces mechanism[C]//10th Electronics Packaging Technology Conference[S.1.]:[s.n.], 2008.

- [24] LI C Y, BØRGESEN P, SULLIVAN T D. Stress-migration related electromigration damage mechanism in passivated, narrow interconnects[J]. Appl Phys Lett, 1991, 59: 1464-1466.

- [25] RU C Q. Thermomigration as a driving force for instability of electromigration induced mass transport in interconnect lines[J]. J Mater Sci, 2000, 35: 5575-5580.

- [26] WEILING G, LI Z, ZHU H, et al. Temperature gradient impact on electromigration failure in VLSI metallization [C]// Proc of the Semi-Therm Symposium[S.I.]: IEEE, 1998, 122-127.

- [27] PLATTEN J K. The soret effect: a review of recent experimental results[J]. J Appl Mechan, 2006, 73: 5-15.

- [28] CHINANG T. BANERJEE Y K, SARASEAT K C. Analytical thermal model for multilevel VLSI interconnects incorporating via effect[J]. IEEE electron device lett, 23: (2002), 31-33.

- [29] RZEPKA S, MEUSEL E, KORHONEN M A, et al. 3-D finite element simulator for migration effects due to various driving forces in interconnect lines[C]// Proceedings of the Stress-Induced Phenomena in Metallization: Fifth International Workshop. [S.l.]: [s.n.], 1999.

- [30] DALLEAU D, ZAAGE K W. Three-dimensional voids simulation in chip metallization structures: a contribution to reliability evaluation[J]. Microelectron Reliab, 2001, 41: 1625-1630.

- [31] ROY A, KUMAR R, TAN C M, et al. Electromigration in damascene copper interconnects of line width down to 100 nm[J]. Semicond Sci Technol, 2006, 21: 1369-1372.

- [32] TAN C M, ZHANG G, GAN Z H. Dynamic study of the physical processes in the intrinsic line electromigration deep submicron copper and aluminum interconnects[J]. IEEE Tans Device Mater Reliab, 2004, 4: 450-456.

- [33] ROY A, TAN C M. Probing into the asymmetric nature of electromigration performance of submicron interconnect via structure[J]. Thin Solid Films, 2007, 515: 3867-3874.

- [34] LI W, TAN C M, HOU Y. Dynamic simulation of electromigration in polycrystalline interconnect thin film using combined Monte Carlo algorithm and finite element modeling[J]. J Appl Phys, 2007, 101: 104314.

- [35] TAN C M, HE F F. 3D Circuit Model for 3D IC Reliability Study[C]//Proc IEEE Int Conference on Thermal, Mechanical and Multiphysics Simulation and Experiments in Micro/Nanoelectronics and Systems. [S.1.]: IEEE, 2009.

- [36] TU K N. Recent advances on electromigration in very-large-scale-integration of interconnects[J]. J Appl Phys, 2003, 94: 5451-5473.

- [37] LI S D, ABDULHAMID M F, BASARAN C. Damage

mechanics of low temperature electromigration and thermomigration[J]. IEEE Trans on Adv Pack, 2009, 32: 478-485.

### 编辑税红

马建国,教授,博士,长江学者 特聘教授、国家自然科学杰出青年基金 获得者。在兰州大学获理学学士及硕士 学位,在德国杜伊斯堡大学(Duisburg University)获工程博士学位;1997年在 加拿大新斯科舍工业大学(Technical University of Nova Scotia)博士后出站 后,在新加坡南洋理工大学任副教授、新加坡南洋理工大学 集成电路与集成系统中心主任;2005年6月起任电子科技大 学教授、博士生导师。

在射频、微波、毫米波电路与系统、集成系统芯片(SoC) 设计与验证、射频集成电路(RFIC)设计及其应用等方向开展 了大量的科学研究,已获得授权美国专利6项,13项中国专 利已授权或在公示中,在IEEE期刊和国际会议上发表学术论 文245篇(其中105篇发表在SCI源期刊上)。