## AIN 基片上重掺杂硼的多晶硅膜电阻率温度特性

何进\*杨传仁(电子科技大学微电子所成都 610054)

【摘要】 研究了 AIN 基片上重掺杂硼的多晶硅膜电阻率温度特性。实验发现,膜电阻率随温度变化呈现出从 NTC 过渡到 PTC 的 U 型特性, 转折温度  $T_M$  的位置依赖工艺条件的变化。理论分析表明: 晶界势垒使膜电阻率在温度变化上存在 一个极小值, 极小值对应的转折温度正比于晶界势垒。

**关** 键 词 多晶硅; 晶界势垒; U 型特性; 转折温度 中图分类号 TM 544: TN 304, 055

近年来, 在微电子器件和集成电路中得到广泛应用的多晶硅薄膜材料受到传感领域的日益重视  $^{[1]}$ 。作为热敏电阻与压敏电阻,多晶硅薄膜由于无 PN 结隔离, 性能稳定, 成本低廉, 具有广泛的应用前景。但是以前的研究局限于  $150\,^{\circ}$ C以下的低温和单一的硅及硅化物衬底, 认为多晶硅膜电阻率温度特性为单纯的 NTC 曲线。本文用 APCVD 薄膜制备法, 以不同工艺条件沉积了 AIN 基片上的重掺杂硼多晶硅膜, 研究了此薄膜在室温至  $450\,^{\circ}$ C的温度范围内的电阻率温度特性。实验发现此多晶硅膜电阻率温度特性为一复杂的"U"型曲线。本文研究以 N. C. C. Lu 的晶界陷阱模型为基础, 推出了多晶膜硅电阻率温度特性理论上的"U"型特征, 理论拟合证实了实验的结果, 为非硅类绝缘衬底上掺杂多晶硅膜用于敏感材料打下了基础。

## 1 实验及结果

#### 1.1 实验方法

将经 HNO<sub>3</sub> :HF :H<sub>2</sub>O=1 :2 :3 混合液清洗干净的 AIN 基片 (30 mm×15 mm×1.0 mm)垂直插入 APCVD 基座上后加热至沉积温度。按一般 APCVD 工艺通入按比例掺杂的 SiH<sub>4</sub> 和 B<sub>2</sub>H<sub>6</sub> 混合气体,并在不同沉积温度下沉积不同厚度的多晶硅膜。然后,500 <sup>©</sup>热氧化一层 SiO<sub>2</sub> 作为多晶硅膜的保护层,将得到的膜片经常规光刻腐蚀和金属化工艺制成待测量的电阻样品,用 HP4145 测定样品在各温度点上电阻后根据样品几何尺寸计算出相应的电阻率,膜厚用阶梯腐蚀染色法测算,粒径用 SEM 测算。

#### 1.2 实验得到的重掺硼多晶硅膜电阻率温度特性

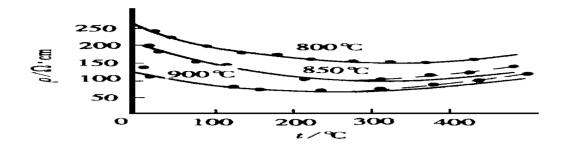

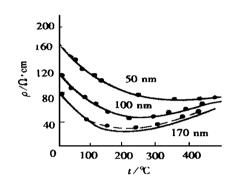

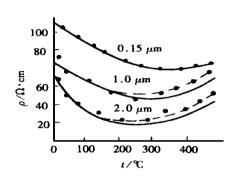

本研究试验了不同沉积温度,不同晶粒大小以及几种膜厚的样品。多次实验发现它们的电阻率温度特性具有一定的相似规律,如图 1~图 3 所示。

<sup>1997</sup>年6月2日收稿,1997年10月8日修改定稿

<sup>\*</sup> 男 30岁 博士生

图 1 重掺硼多晶硅膜不同沉积温度的  $\rho$  -T 特性

图 2 重掺硼多晶硅膜不同晶粒尺寸的  $\varrho$ — T 特性

图 3 重掺硼多晶硅膜不同膜厚的  $\rho-T$  特性

## 2 理论分析

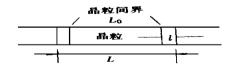

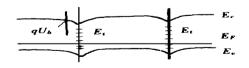

处理掺杂多晶硅电学性质的基本理论是 N. C. C. Lu 提出的晶界陷阱模型<sup>[2]</sup>。该模型认为: 多晶硅材料是由许多小晶粒和连接小晶粒的晶粒间界构成的, 每一小晶粒可以看作一块小晶体, 晶粒间界为载流子陷阱, 自由载流子被陷阱俘获后使晶界带电形成多子势垒区, 势垒高度为  $qU_b$ 。由于样品是硼重掺杂( $\geq$ 10<sup>18</sup>cm<sup>-3</sup>)的多晶硅, 按陷阱模型, 晶粒通常处于部分耗尽状态。因此, 耗尽区通常可视为一高阻区, 图 4a、4b 分别表示出硼掺杂多晶硅的一维简化晶粒结构和晶粒间界陷阱能级图。

(a) 一维简化晶粒结构

(b) 晶粒间界陷阱能级

图 4 硼掺杂多晶硅的能带图

从以上的讨论可以看出,多晶硅膜的总电阻率可视为晶界电阻(耗尽层电阻)与晶粒中性区电阻的串联。即<sup>[3]</sup>

$$\varrho_m = \frac{L - 2l}{L} \, \varrho_g + \frac{2l}{L} \, \varrho_b \tag{1}$$

式中 $ho_m$  为多晶硅膜电阻率 $(\Omega^\circ{

m cm})$ ;  $ho_g$  为单晶硅电阻率 $(\Omega^\circ{

m cm})$ ;  $ho_b$  为晶界电阻率 $(\Omega^\circ{

m cm})$ ; L 为

晶粒长度(nm); l 为耗尽区长度(nm),  $L_0$  晶粒本征长度(nm),  $L_0 = L - 2l$ .

对于 P 型单晶硅, 其电阻率存在为<sup>[4]</sup>

式中 q 为电子电荷量(C);  $U_p$  为空穴迁移率(cm<sup>2</sup>/V °s); P(0) 为本征空穴浓度(cm<sup>-3</sup>);  $N_A$  为掺杂浓度(cm<sup>-3</sup>); P 为全部空穴浓度(cm<sup>-3</sup>)

$$U_p = \frac{q}{m_h} \frac{1}{AT^{3/2} + BPT^{-3/2}} \tag{3}$$

式中  $m_h^*$  为空穴有效质量(g); T 为温度( $^{\circ}$ );  $A \setminus B$  为常数项。

把晶界看作背靠背的双 Schoktty 势垒,在外加偏压未达到击穿电压时,晶界电阻率为<sup>5</sup>

$$\rho_b = \frac{1}{2 l a^2 P} (2 \pi m \, {}_h^* K_0 T)^{V2} \exp(q U_b / K T) \tag{4}$$

在 T=27 °C时,  $P(0)=1.5\times10^{10}\mathrm{cm}^{-3}$ ; 在 T=400 °C时,  $P(0)=10^{16}\mathrm{cm}^{-3}$ 。而样品掺杂  $N_A \ge 10^{18}\mathrm{cm}^{-3}$ ,故可忽视本征载流子激发,认为  $P=N_A$  基本上与温度无关。综合以上各式可得多晶硅膜电阻率表达式为

$$\varrho_{m}(T) = K_{1}(K_{0}T)^{3/2} + K_{2}(K_{0}T)^{-3/2} + K_{3}(K_{0}T)^{1/2} \exp(qU_{b}/KT)$$

$$K_{1} = \frac{(L-2l)m_{h}^{*}A}{N_{A}Lq^{2}K_{0}^{3/2}}$$

$$K_{2} = \frac{(L-2l)K_{0}^{3/2}m_{h}^{*}B}{Lq^{2}}$$

$$K_{3} = \frac{(2\pi m_{h}^{*})^{1/2}}{Lq^{2}N_{A}}$$

(5)

式中  $K_1, K_2, K_3$  是与温度无关的常数、取决于掺杂浓度、晶粒尺寸、晶界状态。

在沉积温度不太高的情况下,未再结晶的 CVD 多晶硅膜中,晶粒尺寸  $L_0$  与耗尽区宽度 l 相比不太大,即  $L_0 \le 2$  l 。 实验观察发现,当沉淀温度小于 850  $^{\circ}$ 时, $L_0$  大小一般在 40 nm ~ 100 nm 范围,而 l 平均大于 60 nm,一般在沉淀温度不高时  $L_0 \le 2$  l 是满足的。此时,从  $\varrho_m$  表达式知

$$\varrho_m(T) \approx \varrho_b(T) = K_3(K_0 T)^{1/2} \exp(qU_b/KT)$$

(6)

为研究式(6)的变化规律, 分别求  $d\rho_m/d(K_0T)$ 和  $d^2\rho_m/d(K_0T)^2$ 。并令  $d\rho_m/d(K_0T)$   $T_m=0$ ,求出  $T_m$  和  $d^2\rho_m/d(K_0T)^2$   $T_m$ , 得到

$$\frac{\mathrm{d}\rho_m}{\mathrm{d}K_0 T} \left| T_m = 0 \right| \tag{7}$$

$$T_m = 2qU_b/K_0 \tag{8}$$

$$\frac{\mathrm{d}^2 \rho_m}{\mathrm{d}(K_0 T)^2} \left| T_m > 0 \right| \tag{9}$$

从式(7)知, $T = T_m$  时, $\ell_m$  取得极值;综合式(8)、(9)知, $T = T_m$  时, $\ell_m$  取得极小值。从式(8)可知,转折温度  $T_m$  随势垒高度  $gU_b$  变化发生移动。

综上所述,多晶硅膜电阻率在  $T < T_m$  时,随温度上升而减小,表现为 N TC 效应;在  $T > T_m$  时,随温度上升而增加,表现为 P T C 效应。从而,多晶硅膜电阻率温度特性为一 U 型曲线。

同理, 可求出  $L_0 \ge 2$  l 时的电阻率。实验观察到, 沉积温度高达 850  $^{\circ}$   $^{\circ}$

大于  $100 \, \text{nm}$ , 而  $l - \Theta \cap T = 50 \, \text{nm}$ 。此时, 应计及晶粒电阻, 多晶硅电阻率表达式即为式(5)。

由于  $\theta_m$  随温度的变化在式(5)第三项表现为指数规律,第二项当温度上升时趋近于零值可以忽略不计,第一项仅改变  $\theta_m \sim T$  特性的 U 型曲线  $T_m$  位置并右部上抬,但并不改变 U 型这一特点,故同样得出与  $L_0 \leq 2$  l 时相同的  $\theta_m$  温度变化规律。

为了定量地证实以上分析的电阻率温度关系是否正确,本研究用式(5)和式(6)对实验数据进行了线性回归和曲线拟合,理论结果如图上实线和点划线所示。数据分析表明,在实验温度范围内, AIN 基片上重掺 B 的多晶硅薄膜电阻率温度特性的确可以用描述晶界电阻率特性的式(6)表示。如图  $1 \sim 3$  实线所示为一 U 型曲线,势垒高度大致在 0.05 eV  $\sim 0.2$  eV 范围内,理论和实验基本吻合。在 300  $^{\circ}$ 以上温度时,由于晶格散射使电阻率上升表现明显,此时用包括晶界电阻和晶粒电阻率的式(5)计算,如图  $1 \sim 3$  点划线所示,更能准确地反映实验结果。

### 3 结论

AIN 基片上硼重掺杂多晶硅膜的温度特性是:

- 1)多晶硅膜电阻率由晶粒中性区电阻率和晶界势垒电阻率两部分构成,晶界电阻率温度特性大致代表了膜电阻率特性:

- 2) 在室温至 450 <sup>℃</sup>的较宽温度范围内, 膜电阻率随温度的变化呈现一个 U 型特性;

- 3) 电阻率的转折温度  $T_m$  正比于晶界势垒  $qU_b$  这一特征值。工艺条件对  $\rho$ -T 特性的影响主要表现为微观上是改变  $qU_b$  的大小,宏观上是移动  $T_m$ ;

- 4) 对于特定的多晶硅器件,可以通过合理地选择工艺条件,如沉积温度  $T_s$ ,晶粒大小 L 和膜厚 h 来调整  $T_m$  以及 TCR。通过  $T_m$  和工作温区的匹配,可以自由地决定 TCR 的大小和正负。

#### 参考文献

- 1 Kamins T I. Design properties of polysilicon. Sensor and Actuators 1990, 21(A) '817

- 2 Lu N C C. Gertzberg L, Lu C Y et al. Modeling and optimization of monolithic polysilicon resistors IEEE Trans Electron Devices 1981, ED—28:818

- 3 周永溶. 半导体材料. 北京:北京理工大学出版社, 1992

- 4 刘恩科. 半导体物理. 北京:国防工业出版社, 1989

- 5 王阳元. 多晶硅薄膜及其在集成电路中的应用. 北京:科学出版社, 1988

- 6 Seto J Y W. The electrical properties of polysilicon films. J Appl Phys 1975, 46:5 247

- 7 Baccarani G, Ricco B. Transport properties of polysilicon films. J Appl Phys 1978, 49 '5 565

# Resistivity Temperature Characteristics of Polysilicon Films Heavily Doped With *B* on AIN Substrate

He Jin Yang Chuanren

(Institute of Microelectron, UEST of China Chengdu 610054)

**Key words** polysilicon; U type curve; interface barrier; criterion